基于VHDL语言的全加器的设计

全加器可以由两个半加器和一个或门连接而成,这样得到的半加器电路称为顶层文件。

设计原理图如下:

下面全加器的设计采用层次结构的VHDL程序设计方法,采用元件例化语句。

- 工程文件名与顶层文件(全加器)文件名一样;

- 把全加器、半加器、或门的vhdl文件都要包含到工程中;

- 在全加器文件中声明半加器、或门为元件;

- 然后例化三个元件:两个半加器和一个或门。

- 软件说明:ModelSimSetup-13.1.0.162,QuartusSetup-13.1.0.162。

建立工程:

第一步:打开Quartus软件。

第二步:点击New Project Wizard -> next.

第三步:选择工程文件的存放位置,输入工程名 -> next -> next。

第四步:在family栏选择芯片型号-Cyclone IV E,在Name栏选择EP4CE115F29C7,选择完之后点击next。(如果不进行硬件调试时,此处默认即可)

第五步:检查工程有没有建错,点击完成。如下图:

程序设计:

全加器顶层文件设计:

--文件名:adder.vhd 应与工程名保持一致:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity adder is port(ain,bin,cin:in std_logic;cout,sum:out std_logic);end adder;architecture fd1 of adder iscomponent h_adder--半加器原件声明port(a,b:in std_logic;co,so:out std_logic);end component;component or2a--声明或门原件port(a,b:in std_logic;c:out std_logic);end component;signal d,e,f:std_logic;beginu1:h_adder port map(a=>ain,b=>bin,co=>d,so=>e);--半加器原件例化u2:h_adder port map(a=>e,b=>cin,co=>f,so=>sum);--半加器原件例化u3:or2a port map(a=>d,b=>f,c=>cout);--半或门原件例化end fd1;

对半加器原件进行实例化:

--文件名:h_adder.vhdlibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;entity h_adder isport(a,b:in std_logic;co,so:out std_logic);end h_adder;architecture fh1 of h_adder isbeginso<=NOT(a XOR (NOT b));co<= a AND b;end fh1;

对或门原件进行实例化:

--文件名:or2a.vhdlibrary IEEE;use IEEE.STD_LOGIC_1164.ALL;entity or2a isport(a,b:in std_logic;c:out std_logic);end or2a;architecture one of or2a isbeginc<=a OR b;end one;

文件仿真(这里采用modelsim仿真波形):

- 选择File-> New -> Verification/Debugging Files ->University Program VWF。

2.打开测试文件。(右键点击添加端口,对输入信号初始化,赋值。)

3.仿真结果:

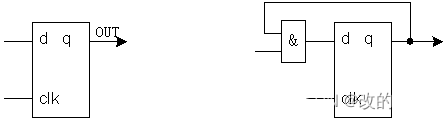

逻辑电路图:

显示编译成功后,选择菜单栏 Tools –>Netlist Viewers –>RTL Viewer 显示逻辑电路图

如果需要通过令一种方法:原理图法进行全加器设计请参看—基于原理图法的全加器设计