如前面的笔记所述,在VHDL语言中信号、变量、常数都要指定数据类型。为此,VHDL提供了多种标准的数据类型。另外,为使用户设计方便,还可以由用户自定义数据类型。这样使语言的描述能力及自由度更进一步提高,从而为系统高层次的仿真提供了必要手段。

同时,VHDL语言数据类型的定义相当严格,不同类型之间的数据不能直接代入,而且,即使数据类型相同,而位长不同时也不能直接代入。这样,为了熟练地使用VHDL语言编写程序,必须准确理解各种数据类型的定义。

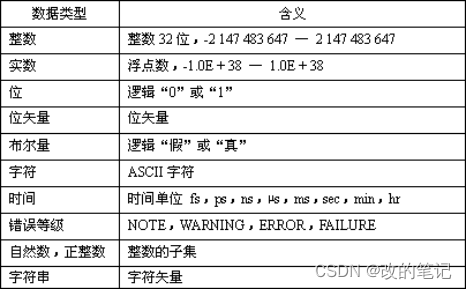

一、标准的数据类型

标准的数据类型共有10种,如表3.2所示。

表3.2 标准数据类型

1.整数(integer)

整数与数学中的整数的定义相同。在VHDL中,整数的表示范围为-2 147 483 647~

2 147 483 647,即从一(231-l)到(231-1)。千万不要把一个实数(含小数点的数)赋予一个整数变量,这是因为VHDL是一个强类型语言,它要求在赋值语句中的数据类型必须匹配。整数的例子如 +136,+12 456,-457。

尽管整数值在电子系统中可能是用一系列二进制位来表示的,但是整数不能看作是位矢量,也不能按位来进行运算,对整数不能用逻辑操作符。当需要进行位操作时,可以用转换函数,将整数转换成位矢量。

2.实数(real)

实数的定义值范围为一1.0E+38 ~ +1.0E+38。实数有正负数,书写时一定要有小数点。例如:

-1.0,十 2.5,-1.0E3 8

有些数可以用整数表示也可以用实数表示。例如,数字1的整数表示为1,而用实数表示则为1.0。两个数的值是一样的,但数据类型却不一样。

3.位(bit)

在数字系统中,信号值通常用一个位来表示。位值的表示方法是,用字符‘0’或者‘1’表示之。位与整数中的1和0不同,‘0’和‘1’仅表示一个位的两种取值。另外,位不能用来描述三态信号。

4.位矢量(bit_vector)

位矢量是用双引号括起来的一组位数据。例如:“001100”,X“00BB”。这里,位矢量最前面的X表示是十六进制。用位矢量数据表示总线状态最形象也最方便。

5.布尔量(boolean)

一个布尔量具有两种状态,“真”或者“假”。虽然布尔量也是二值枚举量,但它和位不同,布尔量没有数值的含义,也不能进行算术运算。它能进行关系运算。例如,它可以在IF语句中被测试,测试结果产生一个布尔量TRUE或者FALSE。

一个布尔量常用来表示信号的状态或者总线上的情况。如果某个信号或者变量被定义为布尔量,那么在仿真中将自动地对其赋值进行核查。一般这一类型的数据的初始值总为 FALSE。

6.字符(character)

字符也是一种数据类型,所定义的字符量通常用单引号括起来,如‘A’。一般情况下VHDL对大小写不敏感,但是对字符量中的大、小写字符VHDL则认为是不一样的。例如,‘A’不同于‘a’。字符量中的字符可以是a~z中的任一个字母,0~9中的任一个数以及空白或者特殊字符,如$,@,%等等。包集合STANDARD中给出了预定义的128个ASCII码字符类型,不能打印的用标识符给出。

7.字符串(string)

字符串是由双引号括起来的一个字符序列,它也称字符矢量或字符串数组。例如:

“ Integer range”

字符串常用于程序的提示和说明。

8.时间(time)

时间是一个物理量数据。完整的时间量数据应包含整数和单位两部分,而且整数和单位之间至少应留一个空格的位置。例如,55 sec,2 min等。在包集合STANDARD中给出了时间的预定义,其单位为fs,ps,ns,µs,ms,sec,min,hr。下面是时间数据的例子:

20 fs,100 ps,3 sec

在系统仿真时,时间数据特别有用,用它可以表示信号延时,从而使模型系统能更逼近实际系统的运行环境。

9.错误等级

错误等级类型数据用来表征系统的状态,它共有4种:NOTE(注意),WARNING(警告),ERROR(出错),FAILURE(失败)。在系统仿真过程中可以用这4种状态来提示系统当前的工作情况。这样可以使操作人员随时了解当前系统工作的情况,并根据系统的不同状态采取相应的对策。

二、用户定义的数据类型

用户自定义的数据类型包括枚举类型、整数类型、实数类型、数组类型、记录类型、存取类型、文件类型等。对于自定义的数据类型的一般书写格式是:

TYPE 数据类型名{,数据类型名} 数据类型定义;

1.枚举类型(enumerated type)

定义:把类型中的各个元素列表出来。

说明:方便、直观,提高程序的可读性。

格式:TYPE 数据类型名 IS(元素1,元素2,……);

例如:TYPE states is( state0,state1,state2,state3);

2.整数类型、实数类型

定义:将数规定在某个范围内。

说明:在标准的数据类型中已经有整数和实数的数据类型,用户再自定义一般是为了

电路设计的特殊要求。

格式:TYPE 数据类型名 IS 数据类型约束范围

例如:TYPE data IS INTEGER range 0 to 7;

3.数组类型(array type)

定义:把两个以上的同一类型的数据组织在一起而形成的新的数据类型称为数组。

说明:数组中的元素可以是VHDL语言的任何一种数据类型;可以是一维或多维数组,多维数组要用多个范围来描述。但多维数组不能生成逻辑电路,EDA工具不能用多维数组进行设计综合,只能用于设计仿真和系统建模。

格式:TYPE数据类型名 IS ARRAY (INTEGER 0 TO 9) OF STD_LOGIC;

例如:

TYPE d IS ARRAY(INTEGER range 0 to 3)of STD_LOGIC_VECTOR(7 downto 0)

SIGNAL data:d;

BEGIN

d(0)<= “01010110”;

d(1)<= “10101000”;

d(2)<= “01100011”;

d(3)<= “00010110”;

4.记录类型(record type)

定义:由不同类型的数据对象组织在一起而形成的单一的对象组称为记录。

说明:记录中的每个元素通过字段名访问;记录中的元素可以是相同或不同的类型;适用于仿真,不能用于综合;从记录中提取元素的数据类型应该用“.”。

格式:TYPE 数据类型 IS RECORD

元素名:数据类型名;

元素名:数据类型名;

END RECORD;

例如:TYPE date IS RECORD

year:INTEGER range 2000 to 2009;

month:INTEGER range 1 to 12;

date:INTERGER range 1 to 31;

END RECORD;

SIGNAL d:date;

BEGIN

d.year <= 2004;

d.month <= 2;

d.date <= 15;

END;

5.存取类型(access type)

定义:存储类型也称为寻址类型,用来在对象之间建立联系,或者给新对象分配或释放存储空间,与高级语言中使用的指针类似。在VHDL’ 93语言标准IEEE std_1076的程序包TEXTIO中定义了一个存取类型。

TYPE line IS ACESS string;

表示类型为line的变量,它的值是指向字符值的指针。只有变量才能定义为存取类型。

6.文件类型(files type)

定义:文件类型是在系统环境中定义为代表文件的数据对象。文件对象的值是系统文件中值的序列。文件类型允许对象有二个文件类型的说明。文件对象由规定的两个过程读出(read)、写入(write)和函数(endfile)检查文件的结尾。

格式:TYPE文件类型名 IS FILE;