本文并不是对VHDL的系统的讲解,而是我认为的关键部分,知道了这些,基本上可以使用VHDL语言进行一些相应的设计。并且在使用的过程中发现问题,再进行一些相应的检索,深入学习,最后达到精通。

首先要明白VHDL是硬件语言,相较于c语言等编程语言较为死板,有某些特定的要求,比如你选用的芯片,它的逻辑单元数量是固定的,所以你编写的代码所用的逻辑单元不能超过它固有的逻辑单元。

其次要明白我们学习VHDL语言是为了服务于硬件,通俗来讲就是要让你的硬件按照你的想法动起来,所以我们编写的代码编译成功并不代表成功要下载到硬件中检验。(这里按照老师的讲法是要先仿真再下载,但是一般情况下是直接下载到硬件中去,如果出现错误在进行各个部分的仿真,这是我个人认为编写最快的方式)。

VHAL的结构

分为库、实体、结构体三个部分。

对于库,就是库函数一般我们使用就加上如图所示的即可,可以满足我们的使用

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;对于实体,就是你的定义,你的输入输出一般常用的有三种类型 out(输出) in(输入) buffer (具有反馈的类型,通俗讲就是你给他赋值了,你有把他作为另一个条件了,“中间商”,使用也是比较方便),关于out与buffer的区别,我在后面会举例说明。

entity shitiming is--实体名要与新建的工程名一样port (one:in std_logic;two:out std_logic;three:buffer std_logic );

end shitiming;有关于定义的类型,在我其他文章中有介绍,需要学习可以去看看。

对于结构体可以理解成运行程序的地方,需要你编程的地方,介绍下基本结构体的组成和书写规则。

architecture jiegoutiming of shitiming is

signal a: std_logic;

signal b: std_logic;

signal c: std_logic;

signal d: std_logic;

beginp1:process()

beginend process p1;p2:process()

beginend process p2;

end jiegoutiming;关于在process中所用的顺序函数还有再process外所用的并列函数我会在其他文章中讲解,需要的可以去翻看。

VHDL的编写实例

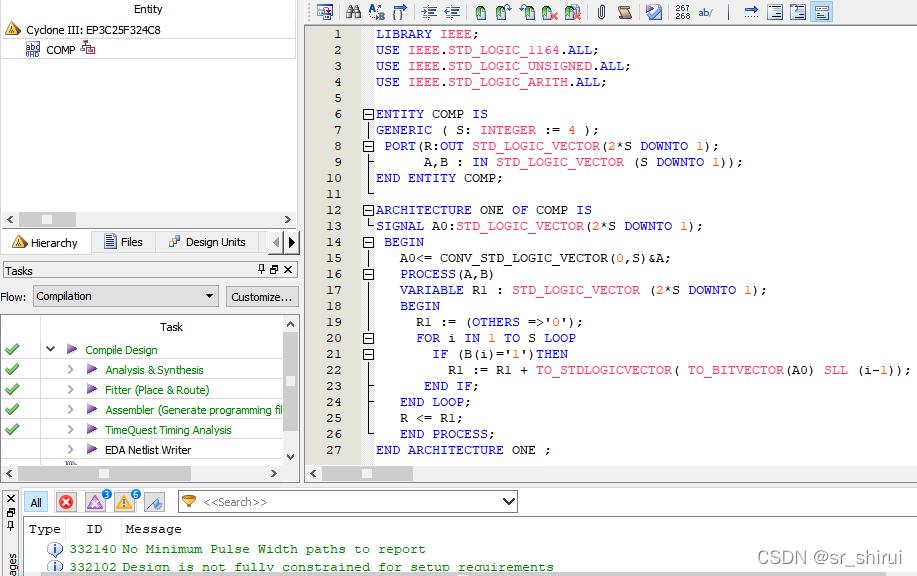

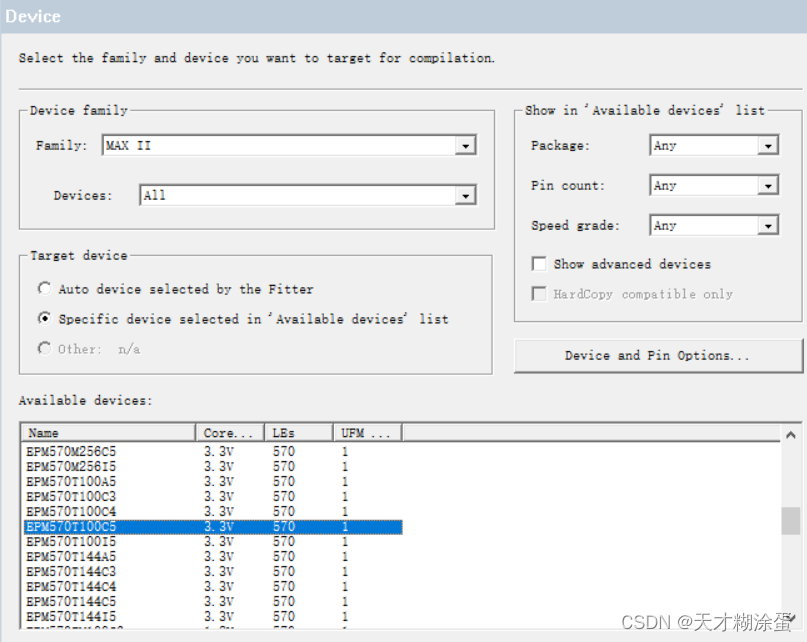

我这里以编写一个12进制的计数器为例,给大家讲解一下,我所用的芯片是

芯片内部的系统时钟的2.048MHz

设计思路也是很简单就是给大家演示一下书写VHDL的格式

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;entity jishuqi is

port(clk:in std_logic;clkclk:out std_logic;num:integer range 11 downto 0 );architecture wzj of jishuqi issignal:q:integer range 0 to 2048000; beginp1:process(clk)beginif(clk'event and clk='1')thenif(q<2048000)thenq=q+1;else q=0;end if;end if;if(q>=0 and q<=1024000)thenclkclk='1';elseclkclk='0';

end process p1;p2:process(clkclk)begin if(clkclk'event and clkclk='1')thenif(num<11)thennum=num+1;else num=0;end if;end if;

end process p2;end wzj;编程部分就是这样,若要显示在七段译码管上则需要加上译码以及编码的部分(在我的其他文章中有讲解)

VHDL的编程格式、步骤大致就是这样,有什么问题随时在评论区询问