目录

VHDL程序的基本结构:

一个完整的VHDL程序包括:

Example:

VHDL的主要构件:

VHDL程序的基本构件:

主要构件:

VHDL的主要构件—库:

使用格式:

Example:

VHDL的主要构件—包:

Example:

VHDL的主要构件—实体:

使用格式:

注意:

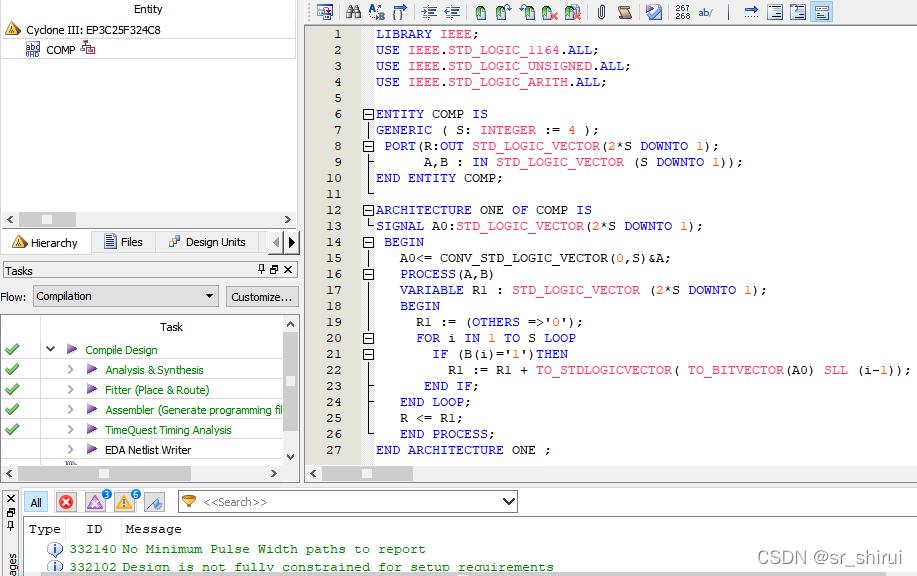

类属参数说明:

端口说明:

Example:写出如下器件的实体描述:

VHDL的主要构件—结构体:

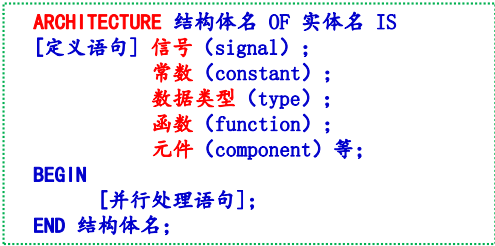

使用格式:

Example:半加器:

结构体的描述方法:

结构体的描述方法——全加器的行为描述:

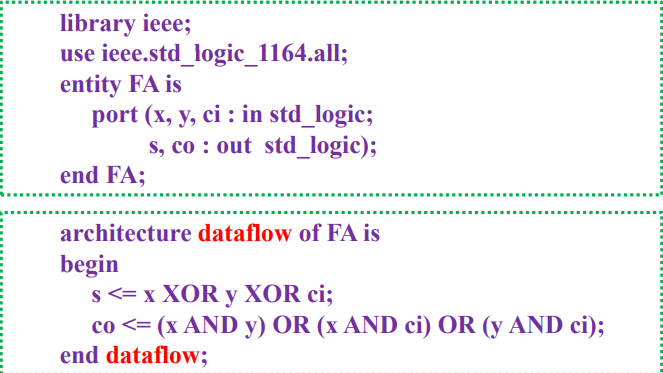

结构体的描述方法 ——全加器的数据流方式:

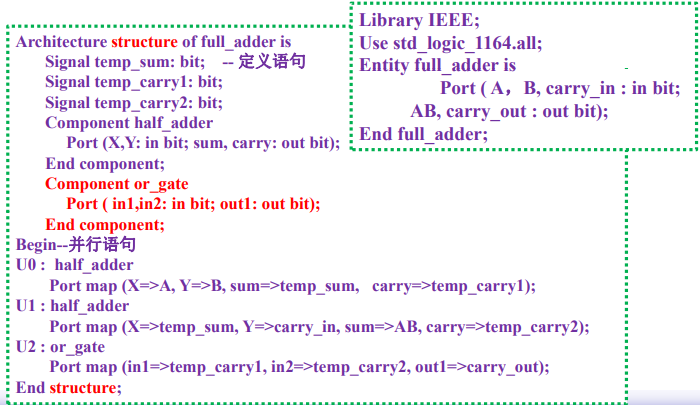

结构体的描述方法 ——全加器的结构描述方式:

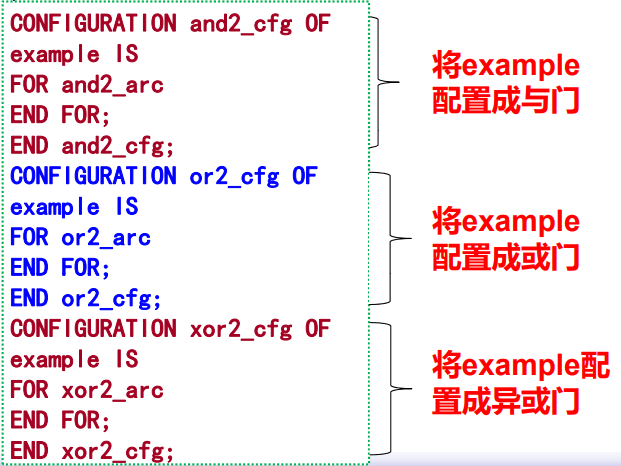

VHDL的主要构件—配置:

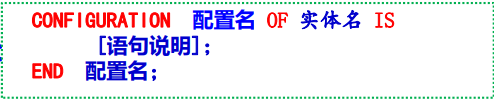

使用格式:

配置作用:

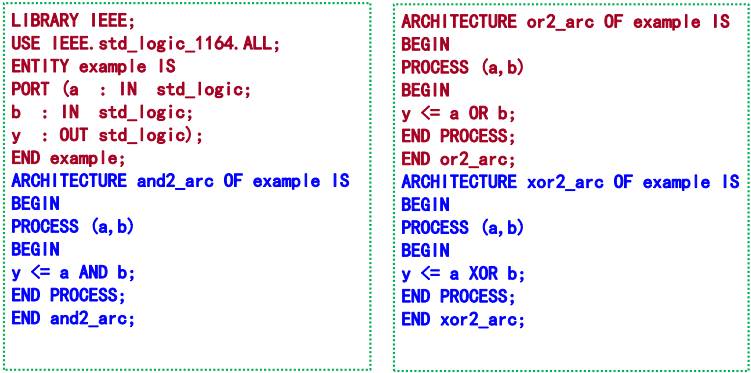

配置语句:设计时设计多个实体,以供配置选择

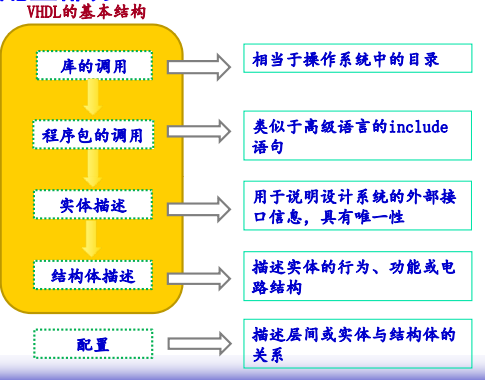

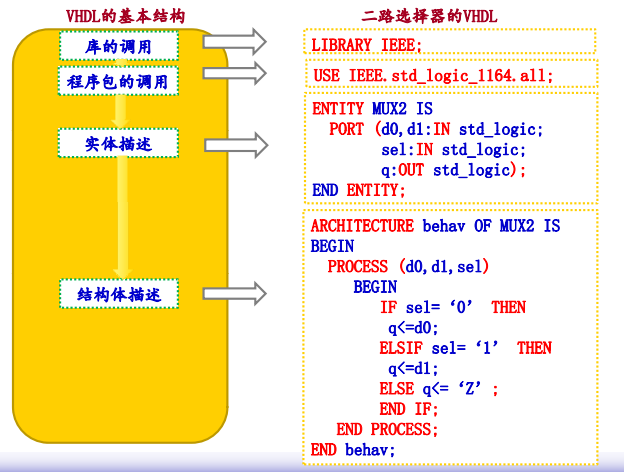

VHDL程序的基本结构:

一个完整的VHDL程序包括:

库的调用,程序包的调用,实体说明和结构体4个部分 。另外还可包括配置部分

Example:

VHDL的主要构件:

VHDL程序的基本构件:

包括库、包,配置,实体,结构体、块、子程序

主要构件:

库 、程序包 、实体 、结构体,配置

VHDL的主要构件—库:

库(Library)是编译后数据的集合,是存放预先完成的程序包和数据集合体的仓库 。

常用的库:STD库(默认库) IEEE库,WORK库(默认库),面向ASIC的库,用户自定义库

使用格式:

![]()

Example:

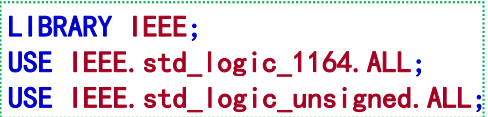

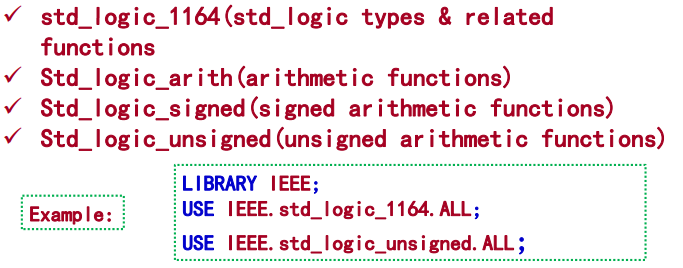

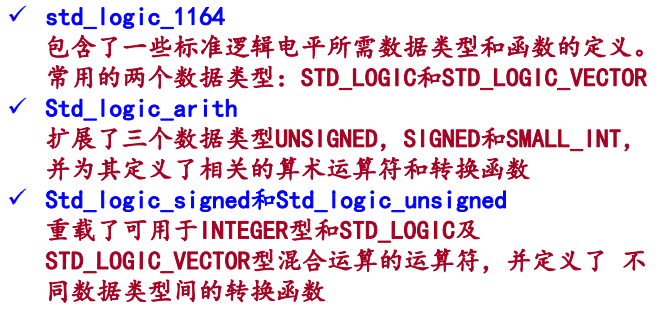

IEEE 库:IEEE库是VHDL设计中最常见的库,由于该库中的程序包并非符合VHDL语言标准 ,因此在使用时必须显示表达

IEEE库内定义了四个常用的程序包:

VHDL的主要构件—包:

包集合:包集合说明就像C语言中的include语句一样,用来单纯地罗列VHDL语言中所要用到的信号定义 、常数定义、数据类型、元件语句、函数定义和过程定义等

Example:

![]()

在VHDL中,同样的语句,使用不同的库或不同的包 , 所生成的电路 , 可能会 辑相 逻 同 ,电路不同

VHDL的主要构件—实体:

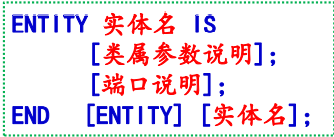

实体(ENTITY)包括实体名,类属参数说明,端口说明三部 分 ,由 留字 保 “ENTITY”引导

使用格式:

注意:

实体名不能以数字开头,不能与保留字相同

实体结束以“END ENTITY”或“END 实体名”结束

类属参数说明:

常用于说明静态信息 如器件延迟

由保留字GENERIC引导

格式如下:

GENERIC(常数名:数据类型:=设定值);

例如:GENERIC(m:time:=1ns);

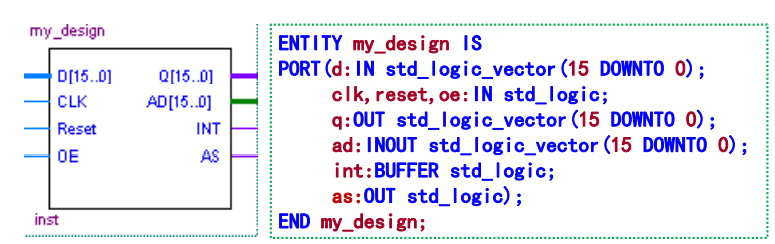

端口说明:

端口说明是一个设计实体界面的描述,提供外部接口信息。

由保留字PORT引导

格式如下:PORT (端口名:端口方向 数据类型 )

例如: PORT (d0:IN std_logic;);

Example:写出如下器件的实体描述:

VHDL的主要构件—结构体:

结构体(ARCHITECTURE)是设计实体的具体描述,指明设计实体的具体行为、所用元件及连接关系。

使用格式:

结构体名应有明确的意义

定义语句只对本结构体有效

结构体里面的语句是并行的

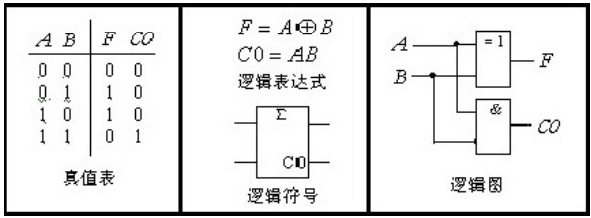

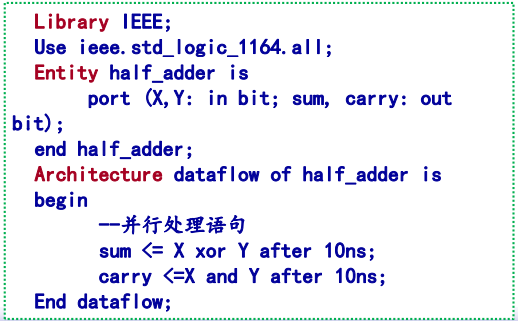

Example:半加器:

半加器电路是指对两个输入数据位进行加法,输出一个结果和进位 。

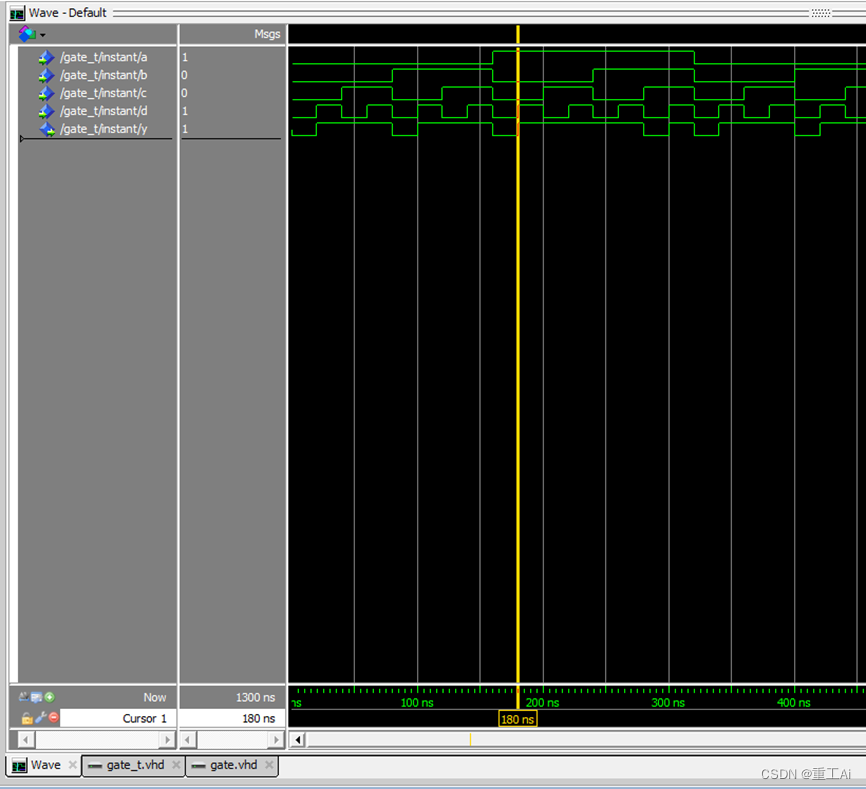

结构体的描述方法:

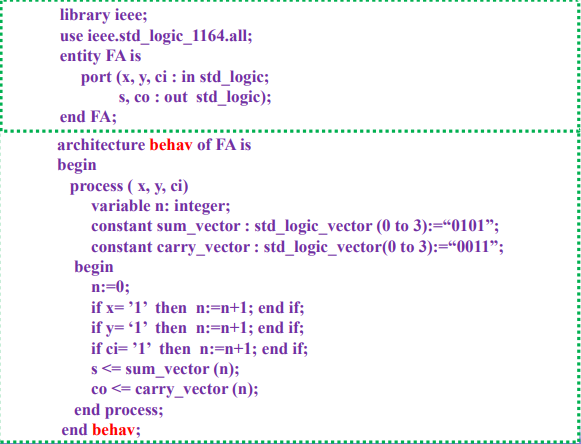

行为描述:描述输入与输出之间的转换行为,不包含内部的电路元件 、电路的结构信息,一般将结构体命名为“behav”

数据流描述:既表示行为,又隐含着结构;体现数据的流动路径和方向,一般将结构体命名为 “dataflow ”

结构描述法:描述电路元件与它们之间的连接关系,一般将结构体命名为“stru数据类型

结构体的描述方法——全加器的行为描述:

结构体的描述方法 ——全加器的数据流方式:

结构体的描述方法 ——全加器的结构描述方式:

VHDL的主要构件—配置:

配置语句:描述层与层之间的连接关系和实体与结构体之间的连接关系

使用格式:

配置作用:

设计实体仿真时 ,利用配置语句来选择不同的结构体,使其与要设计的实体相对应,从而进行性能的对比试验以得到性能最佳的结构体

配置语句:设计时设计多个实体,以供配置选择