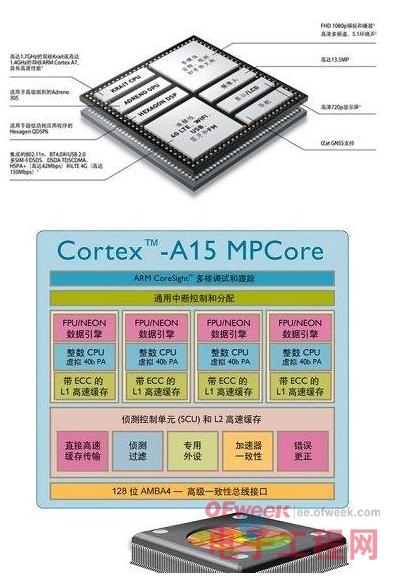

随着麒麟9000和三星Exynos 1080的发布,Android手机芯脏领域正式进入了5nm时代。可惜,麒麟9000的CPU架构仍然停留在ARM去年发布的Cortex-A77阶段,而Exynos 1080虽然用上了ARM最新发布的Cortex-A78,但出于定位的原因它并没能引入AMD在同期发布的最强音Cortex-X1。

如果不出意外,骁龙875、Exynos 2100和天玑2000这些新一代5nm旗舰级SoC都会采用Cortex-X1超大核+Cortex-A78大核+Cortex-A55小核的组合。换句话说,2021年,只有搭配了Cortex-X1核心的SoC,才有资格被称为“超旗舰”。

Cortex-X1之所以有着如此大的号召力,是因为它还有一个外号——自研的终结者。

自研的魅力

在GeekBench等专业测试软件中,苹果iPhone系列手机总能实现对同期旗舰级Android手机的“屠榜”。究其原因,是苹果从iPhone 5时期开始就展开了A系列处理器的“自研”之旅,凭借强大的研发实力和资金优势,ARM原生的Cortex-A系列核心根本就不是对手。ARM全新Cortex-X1核心IP的出现,给予了Android阵营挑战同期A系列处理器的一线曙光。

所谓的“自研”,就是购买ARM最高级的指令集授权,然后根据自身需要开发兼容ARM的架构,但能领先ARM公版的Cortex-A架构多少全看芯片商的技术水平。

自研遇阻 魔改当道

除了苹果,高通在骁龙600/800时代曾采用过自研的Krait架构,距离最近的骁龙820的核心也隶属于自研的Kyro。只是,高通发现自研架构的能耗比很难领先同期公版Cortex-A7x架构太多,非常不经济。因此,从骁龙835开始就采取了BoC战略,也就是咱们常说的“魔改”,基于现有的公版Cortex-A架构进行定制优化。

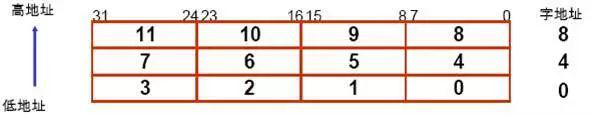

华为从麒麟980开始,也采用了类似的思路,其大核也是基于Cortex-A架构进行了“based”,同样是一种魔改。需要注意的是,公版Cortex-A架构可以进行“魔改”的地方并不多,大家基本都是拿缓存部分开刀,所以无论是高通还是麒麟,其魔改后的内核与公版架构之间的性能差异并不大,关键还是看主频。

三星从Exynos 8890开始也加入到自研大军,并推出了名为猫鼬(Mongoose)的架构核心。

但是,经过四代自主研发后,三星在2019年底已经决定放弃自研的Mongoose内核,并解散了位于德州奥斯汀的整个研发团队,未来将全面使用ARM的公版方案。可见,除了苹果,其他芯片商的自研之路可谓一路荆棘,费力不讨好。

好消息是,ARM此次发布的“三剑客”中的Cortex-X1,其实就是一种允许芯片商在其上进行高度定制的IP内核,可以完全取代辛苦的“自研”之路。

超核降临 排忧解难

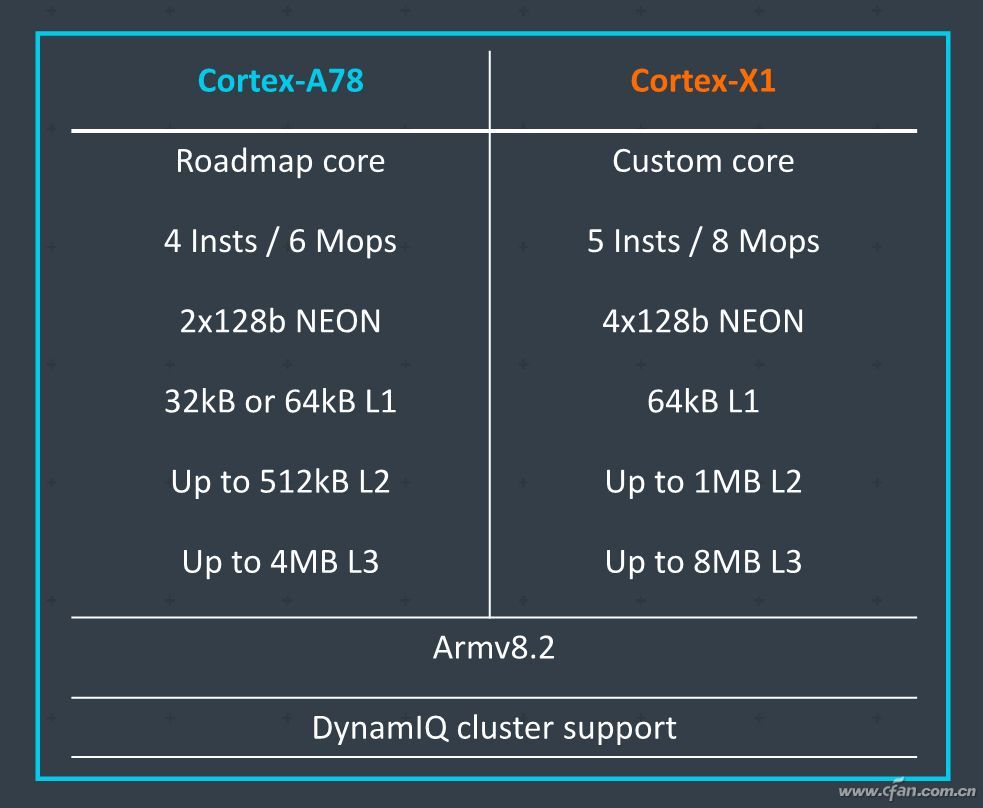

如果Cortex-A78的定位是“大核”,那Cortex-X1就相当于“超大核”,它在架构设计上与Cortex-A78如出一辙,但几乎在每个地方都进行了扩展。

比如,Cortex-X1的解码带宽从Cortex-A78的4路提升到5路,增加了25%;NEON浮点从2条128b提升到了4条128b,相当于浮点性能翻倍;缓存方面,Cortex-X1的L1缓存为64KB,L2缓存1MB,L3缓存最高可达8MB,是Cortex-A78的两倍。

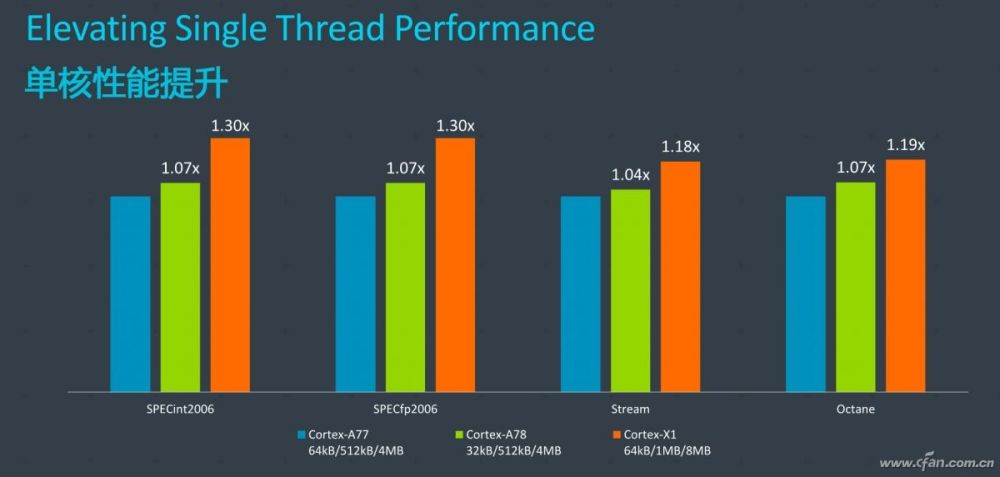

根据ARM的官方资料显示,在主频相同时(也就是IPC性能),Cortex-X1的峰值性能较Cortex-A77提高了30%,比最新的Cortex-A78也有着22%的性能优势,机器学习能力则是Cortex-A77和A78的两倍。

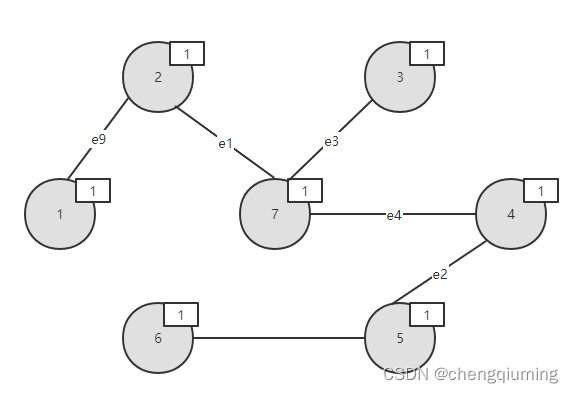

按照规划,芯片商未来可以选择1个Cortex-X1“超核”+3个Cortex-A78“大核”+4个Cortex-A55“小核”组成的三丛集DynamIQ集群,以实现性能和功耗的完美平衡。

唯一可惜的,就是Cortex-X1内核会占用更大的封装面积。

在理论性能方面,4个Cortex-A78核心在搭配4MB L3缓存时,其性能比前代Cortex-A77可提升20%,同时核心面积降低15%;而1个Cortex-X1+3个Cortex-A78核心在搭配8MB L3缓存时,虽然核心面积会增加15%,但峰值性能提升了30%。

看到这里,大家应该知道ARM为什么将Cortex-A78的L1指令缓存改为32KB或64KB可选项目了吧?选择32KB L1指令缓存后,节省下来的封装空间可以留给Cortex-X1,后者强大的性能足以弥补Cortex-A78缓存的部分缺失。至于为什么Cortex-X1的IPC性能比Cortex-A78增加22%,但1+3+4的组合却只比4+4多提升了10%的性能,是因为Cortex-X1只有单独的1颗应战,被其他3颗Cortex-A78平均了性能。

同属超核 性能不一

需要注意的是,ARM对Cortex-X1的定义是“可定制”移动平台,芯片商可以根据预算和需求向ARM提出要求,然后ARM再根据不同的应用场景调整Cortex-X1各个模块的规格设计。

因此,哪怕高通骁龙、三星Exynos、联发科天玑的下一代超旗舰SoC都用上了Cortex-X1内核,但它们之间也会因每时钟周期指令解码数量、L0-BTB容量、宏操作缓存容量、乱序窗口数量、每时钟周期指令发射数量和缓存容量等细节参数的不同,而呈现出不同的性能。都是Cortex-X1核心,而且主频相同,但在性能层面可能依旧存在一定的差异。

换句话说,舍得花钱,或者能通过SoC结构优化,解决Cortex-X1满载温度和功耗偏高问题的芯片性能肯定会更强一些,为了打出Cortex-X1噱头但没有对其进行深度挖掘的芯片性能就会差一些。