在layout中的注意事项

时序匹配要求:

1. 地址、命令、控制线严格参照“时钟线CLK/CLK#”的长度;

2. DQ<0-7>、数据掩码DM0严格参考“数据选通DQS0/DQS0#”的长度;

3. DQ<8-15>、数据掩码DM1严格参考“数据选通DQS1/DQS1#”的长度;

4. DQ<16-23>、数据掩码DM2严格参考“数据选通DQS2/DQS2#”的长度;

5. DQ<24-31>、数据掩码DM3严格参考“数据选通DQS3/DQS3#”的长度;

6. DQ<0-3>参考“时钟线”的长度,误差可适当放大。

设计注意:

1. 差分线控制特征阻抗100欧姆:差分时钟和DQS差分,严格按照差分信号处理,严格等长,同一对差分之间的误差控制在5mil;

2. 其余信号控制特性阻抗50欧姆;

3. 每11根数据线尽量走在同一层,等长误差控制在100mil:

(DQ0~DQ7,DQM0,DQS0_N,DQS0_P)

(DQ8~DQ15,DQM1,DQS1_N,DQS1_P)

(DQ16~DQ23,DQM2,DQS2_N,DQS2_P)

(DQ24~DQ31,DQM3,DQS3_N,DQS3_P)

4. 差分时钟线和地址、命令信号全部设为一组,误差控制在+/-200mil

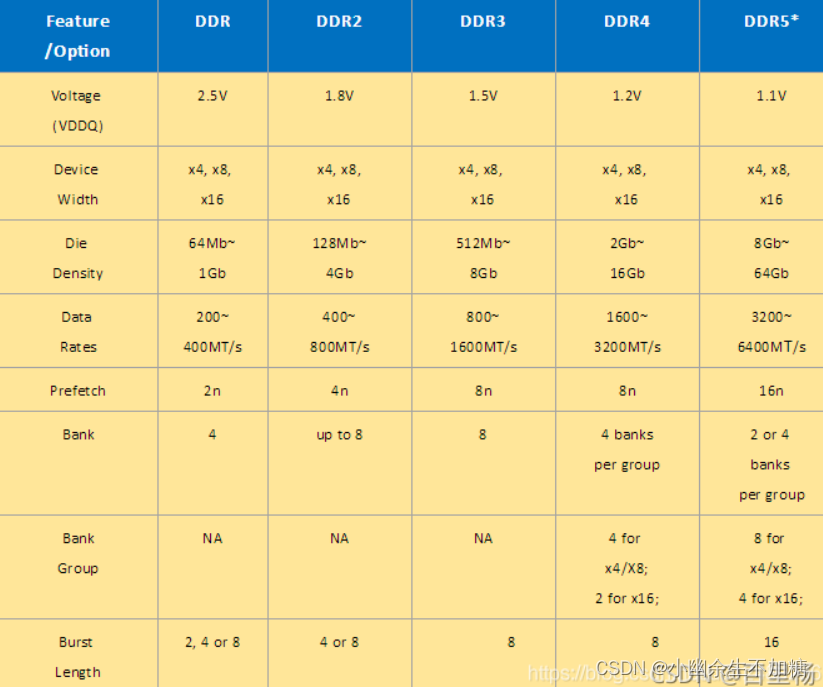

内存容量的计算

容量(bit)= Bank数 * 行数 * 列数 *位宽

以容量为1Gbit的EM68C16CWQD为例

位宽16bit

13根地址线,行地址A0-A12,列地址A0-A9

3根Bank控制线

2^3(bank)x 2^13(Row) x 2^10 (Column) x 2^4(16bit) = 2^30 = 1Gbits