vivado

2024/10/9 9:14:31时序分析之setup/hold时钟path requirement解疑

目录

一、前言

二、时钟边沿选取

2.1 setup和hold

2.2 path requirement

2.3 同频率同相位

2.4 同频率不同相

2.5 倍频或分频关系

2.5 异步时钟

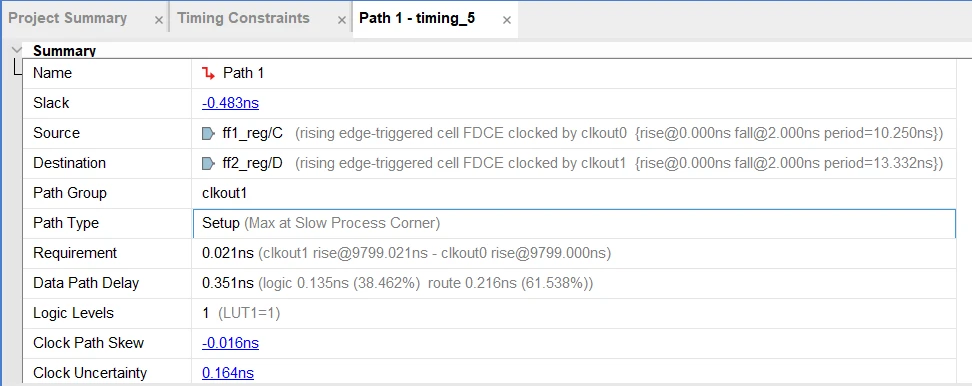

2.6 无公共周期 一、前言 在时序报告中,任选一条时序分析结果查看路径详细延时,会看到在source pa…

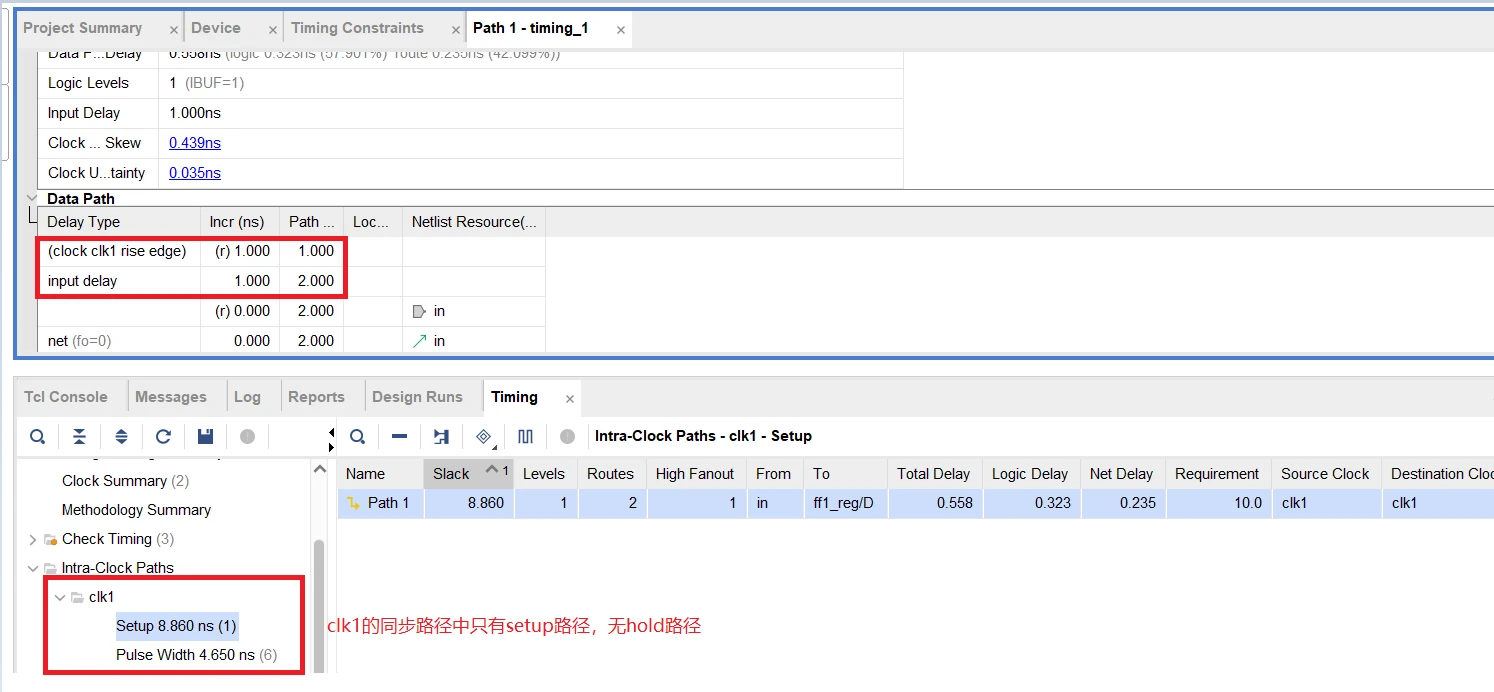

时序约束进阶四:set_input_delay和set_output_delay详解

目录

一、前言

二、set_input_delay/set_output_delay

2.1 延时约束

2.2 约束设置界面

2.3 示例工程

2.4 Delay Value

2.5 Delay value is relative to clock edge

2.6 Delay value already includes latencies of the specified clock edge

2.7 Rise/Fall

2.8 Max/M…

Vivado时序报告之CDC详解大全

目录

一、前言

二、Report CDC

2.1 Report CDC

2.2 配置界面

2.3 CDC报告

2.3.1 General Information

2.3.2 Summary

2.3.3 CDC Details

2.4 Waiver

2.4.1 设置Waiver

2.4.2 报告查看

2.4.3 去除Waiver设置

三、工程设计

四、参考资料 一、前言 前面已经针对…

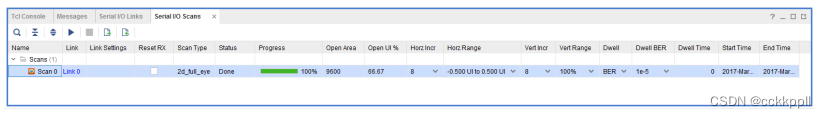

vivado 使用“链路 (Links)”窗口查看和更改链路设置

使用“链路 (Links) ”窗口查看和更改链路设置 创建链路后 , 就会将其添加到“ Links ”视图 ( 请参阅下图 ) 中 , 该视图是更改链路设置和查看状态的主要方法 , 也是最佳方法。 “ Links ”窗口中的每一行都对应 1 …

Verilog语法+:和-:有什么用?

Verilog语法:和-:主要用于位选择,可以让代码更简洁。

一、位选择基础

在Verilog中,位选择可以通过直接索引来实现,例如:

reg [7:0] data;

wire select_a;

wire [2:0] select_b; assign select_a data[3];

assign select_b …

vivado Aurora 8B/10B IP核(1)

Aurora 8B/10B IP 支持 Kintex -7, Virtex -7 FPGA GTP 和 GTH 收发器,Artix -7 FPGA GTP 收发器, Zynq -7000 GTP and GTP 收发器。Aurora 8B/10B IP core 可以工作于单工或者全双工模式。IP CODE的使用也非常简单,支持 AMBA总线的 AXI4-Stream 协议。…

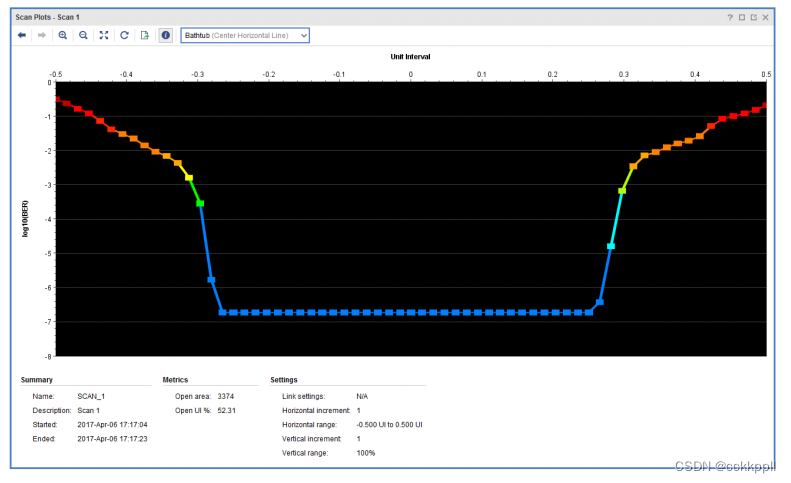

vivado 创建和运行链路清扫

创建和运行链路清扫 要分析给定链路的裕度 , 利用不同 MGT 设置来多次运行链路扫描是很有效的。这样有助于判定最佳设置。 Vivado Serial I/O Analyzer 功能支持您定义、运行、保存和重新调用链路清扫 , 链路清扫是由多次链路扫描集合而成的。 每条…

vivado 物理约束KEEP_HIERARCHY

KEEP_HIERARCHY Applied To Cells Constraint Values • TRUE • FALSE • YES • NO UCF Example INST u1 KEEP_HIERARCHY TRUE; XDC Example set_property DONT_TOUCH true [get_cells u1] IOB Applied To Cells Constraint Values IOB_XnYn UCF Examp…

将IP添加到基础设计

将IP添加到基础设计 本节介绍将AXI IP添加到设计中。 添加低速外设(AXI4 Lite) 1.将等效IP添加到框图中。例如,对于AXI GPIO: a.右键单击方框图中的任意位置,然后选择“添加IP”。 b.搜索并双击AXI GPIO以添加IP。 2.双…

FPGA与Matlab图像处理之直方图均衡化

文章目录 一、什么是直方图?二、什么是直方图均衡化?三、Matlab实现直方图均衡化的步骤第一步: 彩色图像转成灰度图像第二步:提取亮度通道的直方图第三步:累计亮度通道的像素值频率第四步: 映射到新的灰度值 四、Veri…

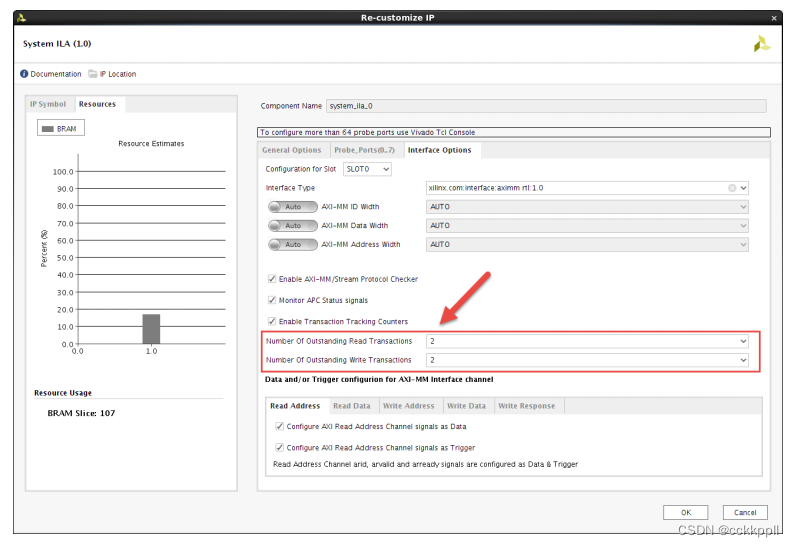

vivado 在硬件管理器中调试 AXI 接口

在硬件管理器中调试 AXI 接口 IP integrator 中的 System ILA IP 支持您在 FPGA 上对设计执行系统内调试。在 Versal 器件上 , System ILA 核已被废 弃。现在 , 在含 AXIS 接口的标准 ILA 中支持接口调试。如需监控 IP integrator 块设计中的…

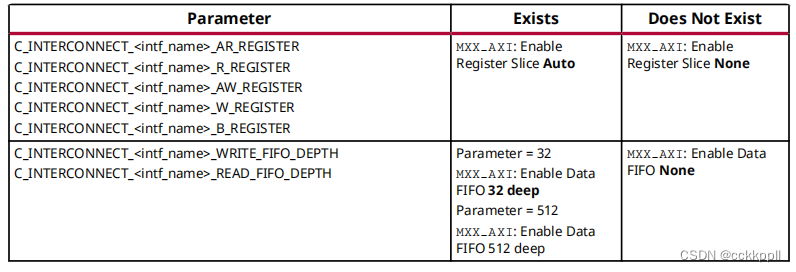

设置AXI主寄存器切片和AXI数据FIFO

设置AXI主寄存器切片和AXI数据FIFO 1.打开MHS文件,并为每个AXI主机设置启用寄存器切片/启用数据FIFO 基于在下表中搜索MHS。 进行搜索时,将<intf_name>替换为相关的BUS_INTERFACE 名称例如,BUS_INTERFACE M_AXI_MM2S的<intf_name>…

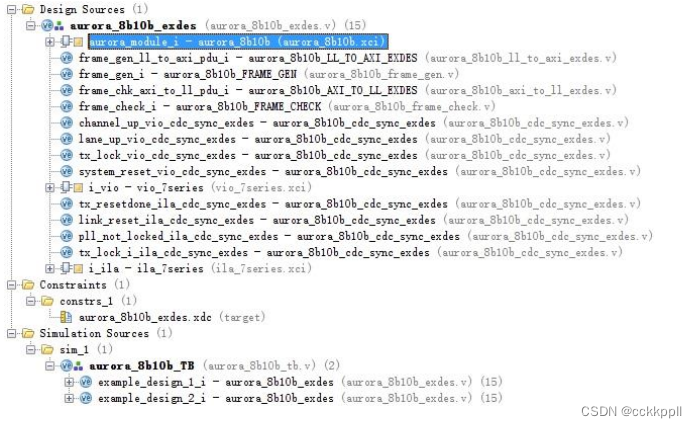

vivado Aurora 8B/10B IP核(12)- Setp By Step搭建FPGA工程

Step1:任意创建一个新的空的工程(创建工程的具体工程如果还不清楚的看我们教程第一季部分), 并且进入IP CORE列表 右击Customize ip Step2:配置 IP CORE-Core options Step3:配置 IP CORE-GT Selections Step4:配置 IP CORE-Shared Logic 为 …

【xilinx】解决vivado中 I/O 时钟布局器错误

典型时钟

AMD 设备上的典型时钟电路结构如下:

输入端口 (IBUF ) → BUFG → FDCE/C

如果使用 MMCM 或 PLL 修改时钟,则其结构如下:

输入端口 (IBUF) → BUFG → MMCM/PLL → BUFG → FDCE/C

对于 GT 时钟,其结构如下…

详解BMP图片格式以及关于Verilog图像处理的仿真环境搭建

文章目录 一、BMP位图简介二、BMP格式分析2.1 如何用十六进制打开BMP图片2.2 头文件格式2.3 信息头格式2.4 调色板格式2.5 位图数据格式2.6 位图对齐方式三、Verilog图像处理的仿真环境搭建3.1 Verilog文件操作指令3.1.1 条件编译 (`` `ifdef``、 `` `else``、`` `endif``)3.1.…

VIVADO IP核之FIR抽取器多相滤波仿真

VIVADO IP核之FIR抽取器多相滤波仿真(含有与MATLAB仿真数据的对比) 目录

前言

一、滤波器系数生成

二、用MATLAB生成仿真数据

三、VIVADO FIR抽取多相滤波器使用

四、VIVADO FIR抽取多相滤波器仿真

五、VIVADO工程下载

总结 前言 关于FIR低通滤波…