前言

在前一篇博文(ARM GICv3中断控制器)中, 介绍了GIC的一些基本概念,本文主要分析了linux kernel中GIC v3中断控制器的代码(drivers/irqchip/irq-gic-v3.c)

linux kernel版本是linux 4.19.29, 体系结构是arm64.

GICv3 DTS设备描述

首先,在讨论GICv3驱动代码分析前,先看下GICv3在DTS里是怎么定义的。

一个gicv3定义的例子

gic: interrupt-controller@2c010000 {compatible = "arm,gic-v3"; #interrupt-cells = <4>; #address-cells = <2>;#size-cells = <2>;ranges;interrupt-controller;redistributor-stride = <0x0 0x40000>; // 256kB stride#redistributor-regions = <2>;reg = <0x0 0x2c010000 0 0x10000>, // GICD<0x0 0x2d000000 0 0x800000>, // GICR 1: CPUs 0-31<0x0 0x2e000000 0 0x800000>; // GICR 2: CPUs 32-63<0x0 0x2c040000 0 0x2000>, // GICC<0x0 0x2c060000 0 0x2000>, // GICH<0x0 0x2c080000 0 0x2000>; // GICVinterrupts = <1 9 4>;gic-its@2c200000 {compatible = "arm,gic-v3-its";msi-controller;#msi-cells = <1>;reg = <0x0 0x2c200000 0 0x20000>;};gic-its@2c400000 {compatible = "arm,gic-v3-its";msi-controller;#msi-cells = <1>;reg = <0x0 0x2c400000 0 0x20000>;};};- compatible: 用于匹配GICv3驱动

- #interrupt-cells: 这是一个中断控制器节点的属性。它声明了该中断控制器的中断指示符(-interrupts)中 cell 的个数

- #address-cells , #size-cells, ranges:用于寻址, #address-cells表示reg中address元素的个数,#size-cells用来表示length元素的个数

- interrupt-controller: 表示该节点是一个中断控制器

- redistributor-stride: 一个GICR的大小

- #redistributor-regions: GICR域个数。

- reg :GIC的物理基地址,分别对应GICD,GICR,GICC…

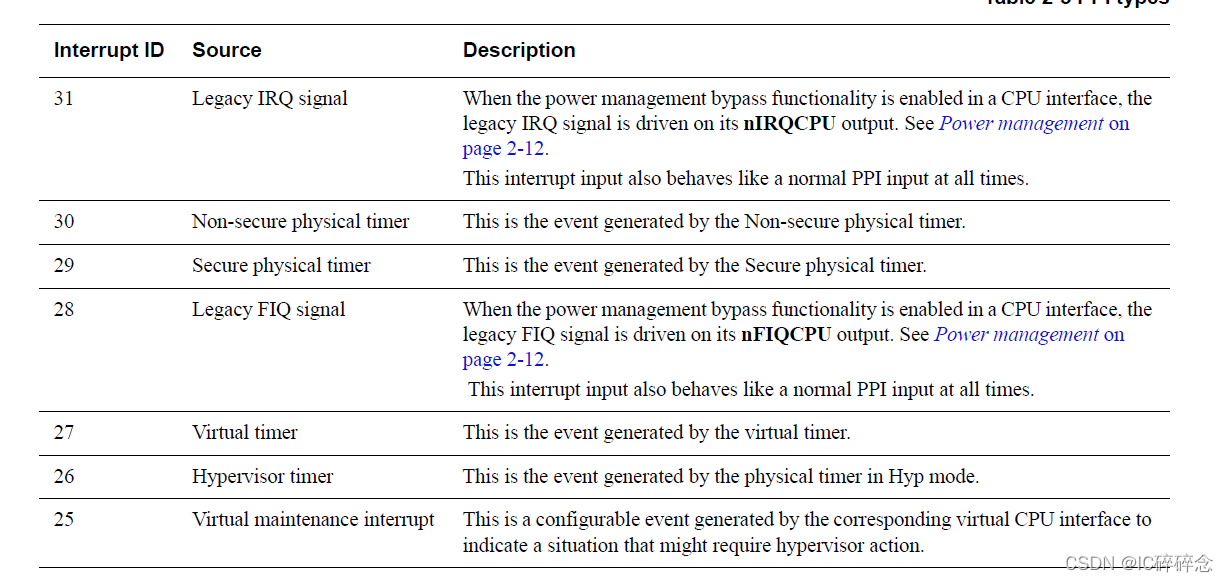

- interrupts: 分别代表中断类型,中断号,中断类型, PPI中断亲和, 保留字段。

a为0表示SPI,1表示PPI;b表示中断号(注意SPI/PPI的中断号范围);c为1表示沿中断,4表示电平中断。 - msi-controller: 表示节点是MSI控制器

GICv3 初始化流程

1. irq chip driver声明

IRQCHIP_DECLARE(gic_v3, "arm,gic-v3", gic_of_init);

定义IRQCHIP_DECLARE之后,相应的内容会保存到__irqchip_of_table里边。

#define IRQCHIP_DECLARE(name, compat, fn) OF_DECLARE_2(irqchip, name, compat, fn)#define OF_DECLARE_2(table, name, compat, fn) \ _OF_DECLARE(table, name, compat, fn, of_init_fn_2)#define _OF_DECLARE(table, name, compat, fn, fn_type) \ static const struct of_device_id __of_table_##name \ __used __section(__##table##_of_table) \ = { .compatible = compat, \ .data = (fn == (fn_type)NULL) ? fn : fn }

__irqchip_of_table在vmlinux.lds文件里边被放到了__irqchip_begin和__irqchip_of_end之间

#ifdef CONFIG_IRQCHIP#define IRQCHIP_OF_MATCH_TABLE() \. = ALIGN(8); \VMLINUX_SYMBOL(__irqchip_begin) = .; \*(__irqchip_of_table) \*(__irqchip_of_end)

#endif

__irqchip_begin和__irqchip_of_end的内容被drivers/irqchip/irqchip.c文件读出并根据其在device tree里边的内容进行初始化。

2. gic_of_init流程

static int __init gic_of_init(struct device_node *node, struct device_node *parent)

{void __iomem *dist_base;struct redist_region *rdist_regs;u64 redist_stride;u32 nr_redist_regions;int err, i;dist_base = of_iomap(node, 0); ------------- (1)if (!dist_base) {pr_err("%pOF: unable to map gic dist registers\n", node);return -ENXIO;}err = gic_validate_dist_version(dist_base); --------------- (2)if (err) {pr_err("%pOF: no distributor detected, giving up\n", node);goto out_unmap_dist;}if (of_property_read_u32(node, "#redistributor-regions", &nr_redist_regions)) ------- (3)nr_redist_regions = 1;rdist_regs = kcalloc(nr_redist_regions, sizeof(*rdist_regs),GFP_KERNEL);if (!rdist_regs) {err = -ENOMEM;goto out_unmap_dist;}for (i = 0; i < nr_redist_regions; i++) { --------- (4)struct resource res;int ret;ret = of_address_to_resource(node, 1 + i, &res);rdist_regs[i].redist_base = of_iomap(node, 1 + i);if (ret || !rdist_regs[i].redist_base) {pr_err("%pOF: couldn't map region %d\n", node, i);err = -ENODEV;goto out_unmap_rdist;}rdist_regs[i].phys_base = res.start; }if (of_property_read_u64(node, "redistributor-stride", &redist_stride)) ----------- (5)redist_stride = 0;err = gic_init_bases(dist_base, rdist_regs, nr_redist_regions,redist_stride, &node->fwnode); ------------- (6)if (err)goto out_unmap_rdist;gic_populate_ppi_partitions(node); -------------- (7)if (static_branch_likely(&supports_deactivate_key))gic_of_setup_kvm_info(node); return 0;out_unmap_rdist:for (i = 0; i < nr_redist_regions; i++)if (rdist_regs[i].redist_base)iounmap(rdist_regs[i].redist_base);kfree(rdist_regs);

out_unmap_dist:iounmap(dist_base);return err;

}(1)映射GICD的寄存器地址空间。 通过设备结点直接进行设备内存区间的 ioremap(),index是内存段的索引。若设备结点的reg属性有多段,可通过index标示要ioremap的是哪一段,只有1段的情况, index为0。采用Device Tree后,大量的设备驱动通过of_iomap()进行映射,而不再通过传统的ioremap。

(2) 验证GICD的版本是否为GICv3 or GICv4。 主要通过读GICD_PIDR2寄存器bit[7:4]. 0x1代表GICv1, 0x2代表GICv2…以此类推。

(3) 通过DTS读取redistributor-regions的值。redistributor-regions代表GICR独立的区域数量(地址连续)。

假设一个64核的arm64 服务器,redistributor-regions=2, 那么64个核可以用2个连续的GICR连续空间表示。

(4) 为一个GICR域 分配基地址。

(5) 通过DTS读取redistributor-stride的值. redistributor-stride代表GICR域中每一个GICR的大小,正常情况下一个CPU对应一个GICR(redistributor-stride必须是64KB的倍数)

(6) 主要处理流程,下面介绍。

(7) 可以设置一组PPI的亲和性。

3. gic_init_bases流程

static int __init gic_init_bases(void __iomem *dist_base,struct redist_region *rdist_regs,u32 nr_redist_regions,u64 redist_stride,struct fwnode_handle *handle)

{u32 typer;int gic_irqs;int err;gic_data.fwnode = handle; gic_data.dist_base = dist_base;gic_data.redist_regions = rdist_regs;gic_data.nr_redist_regions = nr_redist_regions;gic_data.redist_stride = redist_stride;/** Find out how many interrupts are supported.* The GIC only supports up to 1020 interrupt sources (SGI+PPI+SPI)*/typer = readl_relaxed(gic_data.dist_base + GICD_TYPER); ------------- (1)gic_data.rdists.gicd_typer = typer;gic_irqs = GICD_TYPER_IRQS(typer);if (gic_irqs > 1020)gic_irqs = 1020;gic_data.irq_nr = gic_irqs;gic_data.domain = irq_domain_create_tree(handle, &gic_irq_domain_ops,&gic_data); -------------- (2)irq_domain_update_bus_token(gic_data.domain, DOMAIN_BUS_WIRED); ------------- (3)gic_data.rdists.rdist = alloc_percpu(typeof(*gic_data.rdists.rdist));gic_data.rdists.has_vlpis = true;gic_data.rdists.has_direct_lpi = true;if (WARN_ON(!gic_data.domain) || WARN_ON(!gic_data.rdists.rdist)) {err = -ENOMEM;goto out_free;}gic_data.has_rss = !!(typer & GICD_TYPER_RSS); ------------ (4)pr_info("Distributor has %sRange Selector support\n",gic_data.has_rss ? "" : "no ");if (typer & GICD_TYPER_MBIS) { err = mbi_init(handle, gic_data.domain); ------------ (5)if (err)pr_err("Failed to initialize MBIs\n");}set_handle_irq(gic_handle_irq); ------------------- (6)gic_update_vlpi_properties(); ------------------- (7)if (IS_ENABLED(CONFIG_ARM_GIC_V3_ITS) && gic_dist_supports_lpis())its_init(handle, &gic_data.rdists, gic_data.domain); ------------- (8)gic_smp_init(); ----------(9)gic_dist_init(); ----------(10)gic_cpu_init(); ----------(11)gic_cpu_pm_init(); ----------(12)return 0;out_free:if (gic_data.domain)irq_domain_remove(gic_data.domain);free_percpu(gic_data.rdists.rdist);return err;

}

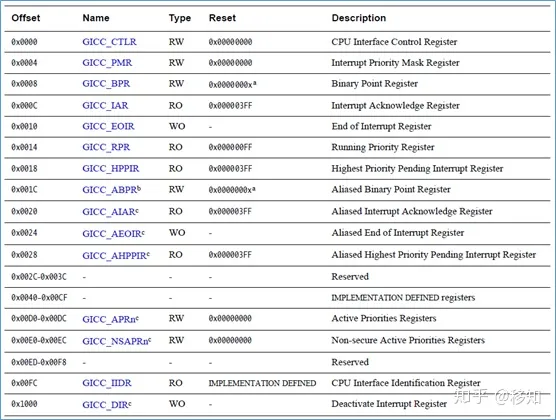

(1) 确认支持SPI 中断号最大的值为多少,GICv3最多支持1020个中断(SPI+SGI+SPI).GICD_TYPER寄存器bit[4:0], 如果该字段的值为N,则最大SPI INTID为32(N + 1)-1。 例如,0x00011指定最大SPI INTID为127。

(2) 向系统中注册一个irq domain的数据结构. irq_domain主要作用是将硬件中断号映射到IRQ number。 可以参考[Linux内核笔记之中断映射]

(3) 主要作用是给irq_find_host()函数使用,找到对应的irq_domain。 这里使用 DOMAIN_BUS_WIRED,主要作用就是区分其他domain, 如MSI。

(4) 判断GICD 是否支持rss, rss(Range Selector Support)表示SGI中断亲和性的范围 GICD_TYPER寄存器bit[26], 如果该字段为0,表示中断路由(IRI) 支持affinity 0-15的SGI,如果该字段为1, 表示支持affinity 0 - 255的SGI

(5) 判断是否支持通过写GICD寄存器生成消息中断。GICD_TYPER寄存器bit[16]

(6) 设定arch相关的irq handler。gic_irq_handle是内核gic中断处理的入口函数, 可以参考系列文章 [Linux 内核笔记之高层中断处理]

(7) 更新vlpi相关配置。gic虚拟化相关。

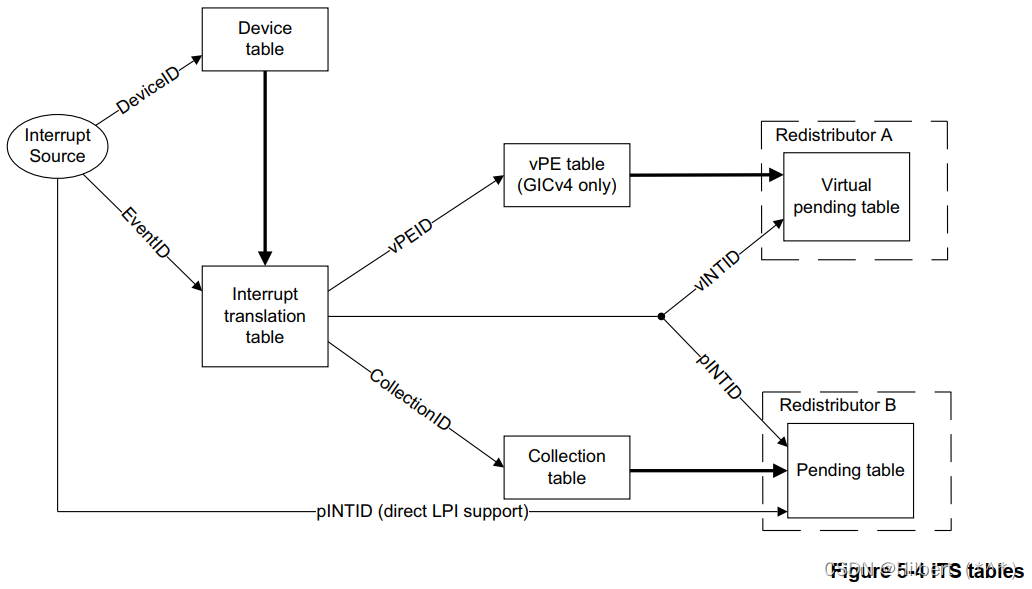

(8) 初始化ITS。 Interrupt Translation Service, 用来解析LPI中断。 初始化之前需要先判断GIC是否支持LPI,该功能在ARM里是可选的。可以参考系列文章[ARM GICv3 ITS介绍及代码分析]。

(9) 该函数主要包含两个作用。 1.设置核间通信函数。当一个CPU core上的软件控制行为需要传递到其他的CPU上的时候,就会调用这个callback函数(例如在某一个CPU上运行的进程调用了系统调用进行reboot)。对于GIC v3,这个callback定义为gic_raise_softirq. 2. 设置CPU 上下线流程中和GIC相关的状态机

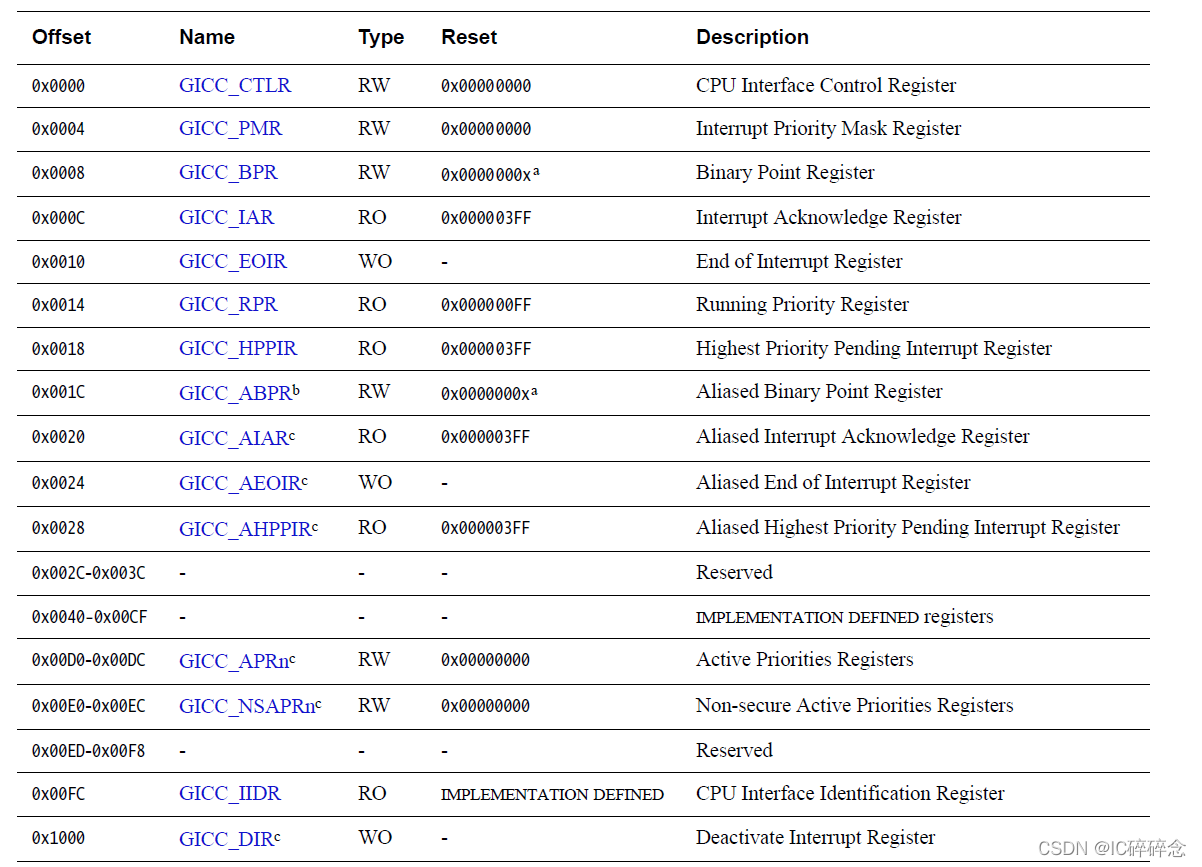

(10) 初始化GICD。

(11) 初始化CPU interface.

(12) 初始化GIC电源管理。

参考资料

IHI0069D_gic_architecture_specification