原文来自前辈:http://www.lujun.org.cn/?p=3861

真的很优秀的文章

ARM的cpu,特别是cortex-A系列的CPU,目前都是多core的cpu,因此对于多core的cpu的中断管理,就不能像单core那样简单去管理,由此arm定义了GICv2架构,来支持多核cpu的中断管理。

一、gicv2架构

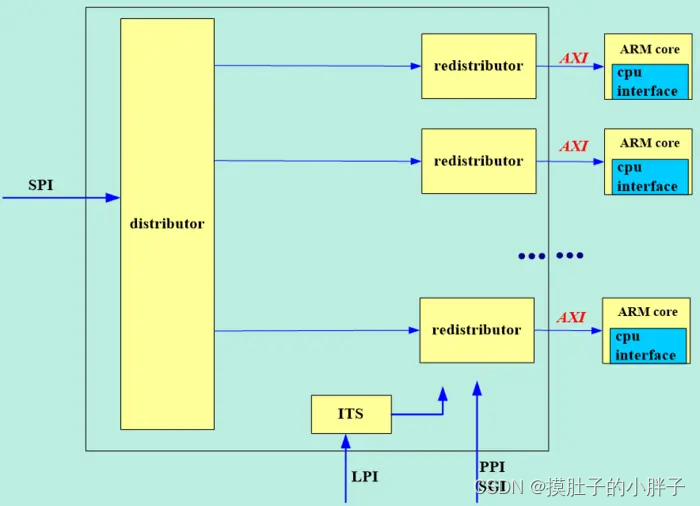

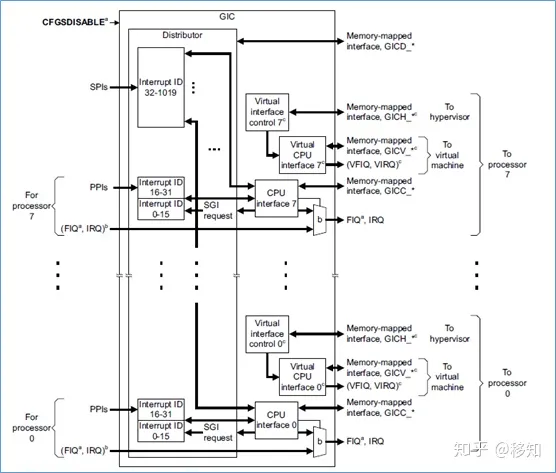

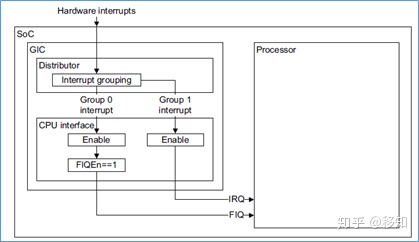

GICv2,支持最大8个core。其框图如下图所示:

在gicv2中,gic由两个大模块组成:

-

distributor:实现中断分发,对于PPI,SGI是各个core独有的中断,不参与目的core的仲裁,SPI,是所有core共享的,根据配置决定中断发往的core。最后选择最高优先级中断发送给cpu interface。寄存器使用 GICD_ 作为前缀。一个gic中,只有一个GICD。

-

cpu interface:将GICD发送的中断信息,通过IRQ,FIQ管脚,传输给core。寄存器使用 GICC_ 作为前缀。 每一个core,有一个cpu interface。

-

virtual cpu interface:将GICD发送的虚拟中断信息,通过VIRQ,VFIQ管脚,传输给core。每一个core,有一个virtual cpu interface。而在这virtual cpu interface中,又包含以下两个组件:

-

virtual interface control:寄存器使用 GICH_ 作为前缀

-

virtual cpu interface:寄存器使用 GICV_ 作为前缀

图中的virtual interface,是用于支持虚拟中断,本系列不讨论虚拟中断。

GICv2支持中断旁路模式,也就是gic外部的FIQ,IRQ直接接到core的FIQ,IRQ上,相当于gic是不使能的。也就是CFGSDISABLE是有效的,将GIC给无效掉。

gicv2,定义了自己的一些寄存器,这些寄存器,都是使用memory-mapped的方式去访问的,也就是在soc中,会留有一片空间,给gic。 cpu通过访问这部分空间,来对gic进行操作。 寄存器,分为以下:

- GICD_*: distributor的寄存器

- GICH_*: 虚拟interface的控制寄存器

- GICV_*:虚拟interface的控制寄存器

- GICC_*: 虚拟cpu interface的寄存器

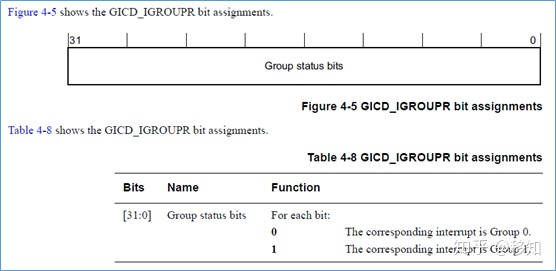

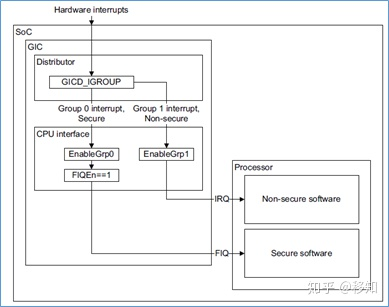

二、中断分组

givc2,将中断,分成了group0和group1。使用寄存器GICD_IGROUPRn来对每个中断,设置组。

-

group0:安全中断,由nFIQ驱动

-

group1:非安全中断,由nIRQ驱动

三、中断号

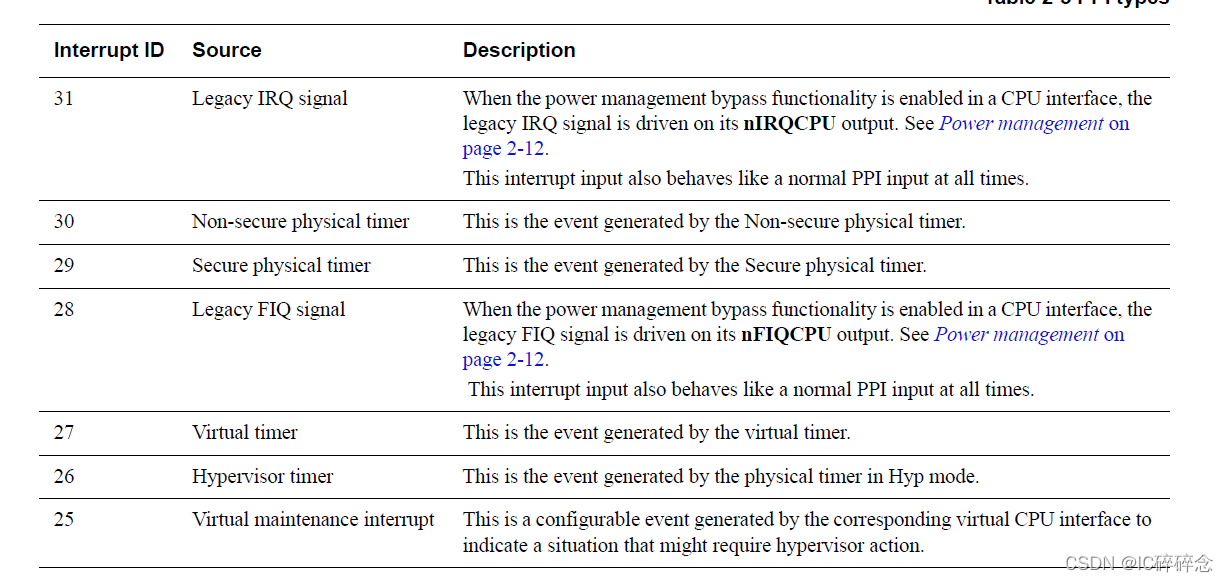

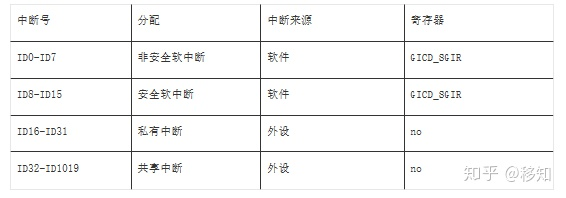

gicv2,支持最大1020个中断。其中断号分配如下:

四、gic结构

gic主要包括以下两个组件:

-

distributor

-

cpu interface

1、distributor

中断分发器,用来收集所有的中断来源,并且为每个中断源设置中断优先级,中断分组,中断目的core。当有中断产生时,将当前最高优先级中断,发送给对应的cpu interface。 distributor对中断提供以下的功能:

+ 全局中断使能

+ 每个中断的使能

+ 中断的优先级

+ 中断的分组

+ 中断的目的core

+ 中断触发方式

+ 对于SGI中断,**传输中断到指定的core**

+ 每个中断的状态管理

+ 提供软件,可以修改中断的pending状态

2、cpu interface

cpu interface,将GICD发送的中断信息,通过IRQ,FIQ管脚,发送给连接到该cpu接口的core。 cpu interface提供了一下的功能:

+ 将中断请求发送给cpu

+ 对中断进行认可(acknowledging an interrupt)

+ 中断完成识别(indicating completion of an interrupt)

+ 设置中断优先级屏蔽

+ 定义中断抢占策略

+ 决定当前处于pending状态最高优先级中断

五、中断认可

中断认可,是指cpu响应该中断。**此时中断状态从pending状态,变为active状态。**通过访问GICC_IAR寄存器,来对中断进行认可。

- GICC_IAR: 认可group0的中断

- GICC_AIAR: 认可group1的中断

六、中断完成

中断完成,是指cpu处理完中断。此时中断状态从active状态,变为inactive状态。gic中,对中断完成,定义了以下两个stage:

-

优先级重置(priority drop):将当前中断屏蔽的最高优先级进行重置,以便能够响应低优先级中断。group0中断,通过写GICC_EOIR寄存器,来实现优先级重置,group1中断,通过写 GICC_AEOIR 寄存器,来实现优先级重置。(将waiting的转为pending-active)

-

中断无效(interrupt deactivation):将中断的状态,设置为inactive状态。通过写 GICC_DIR 寄存器,来实现中断无效。

这里为什么要对中断完成,定义2个stage,其实是有考虑的。对于中断来说,我们是希望中断处理程序越短越好,但是有些中断处理程序,就是比较长,在这种情况下,就会使其他中断得到响应的实际变长,从而影响实时性。

比如当前cpu在响应优先级为4的中断A,但是这个中断A的中断处理程序比较长,此时如果有优先级为5的中断B到来,那么cpu是不会响应这个中断的。

在软件上,会将中断处理程序分为两部分,分为上半部分,和下半部分。

-

在上半部分,完成中断最紧急的任务,然后就可以通知GIC,降低当前的中断处理优先级,以便其他中断能够得到响应。(这个时候完成关键的事情,就可以挂起5了,给别人点声音,安慰一下,我要完事了。)

-

在下半部分,处理该中断的其他事情。

在这种机制下,低优先级的中断,不用等待高优先级的中断,完全执行完中断处理程序后,就可以被cpu所响应,提高实时性。(就是高优先级的完事了,低优先级已经处在pending状态,就可以立马 转为active)

为了实现上述机制,就将中断完成分成了2步。

还是刚刚的例子,cpu在响应优先级为4的中断A,当中断A的上半部分完成后,通知GIC,优先级重置(drop priority),GIC将当前的最高优先级中断重置,重置到响应中断A之前的优先级,比如优先级6,那么此时优先级为5的中断B,就可以被cpu响应。(这里我总感觉有点奇怪,重置到响应中断A之前的优先级,比如优先级6,这句话怎么把优先级给变化了,这个优先级不是配好了?这里我想也不用特别的纠结!主要是体会中断完成,分为两步。完事了先重置优先级,把备胎准备好,在把现在的休了,就很快的换下一个,可谓渣男!!!)

最后中断A的下半部分完成后,通知GIC,将该中断A的状态,设置为inactive状态,此时中断A就真正的完成了。 当然,也可以不将中断完成分成2步,就1步。通过控制 GICC_CTLR寄存器的EOImode比特,来决定是否将中断完成分成2步。

(linux系统属于这种数值越小优先级越高,数值越大优先级越低的系统)

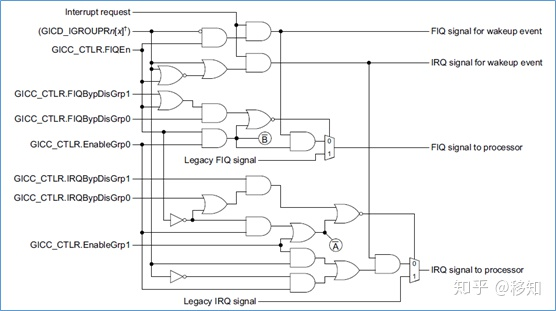

七、bypass功能

gicv2支持bypass功能,这样gic就不起作用了,core的中断管脚,直接由soc的其他部门信号驱动。 如下图所示,通过控制 GICC_CLTR 寄存器的一些比特位,来实现bypass功能。不过这个功能一般不使用,不然何必要在arm的soc中,加入gic呢?

八、中断处理流程

中断处理流程,包含了以下几步:

- GIC决定每个中断的使能状态,不使能的中断,是不能发送中断的

- 如果某个中断的中断源有效,GIC将该中断的状态设置为pending状态,然后判断该中断的目标core

- 对于每一个core,GIC将当前处于pending状态的优先级最高的中断,发送给该core的cpu interface

- cpu interface接收GIC发送的中断请求,判断优先级是否满足要求,如果满足,就将中断通过nFIQ或nIRQ管脚,发送给core。

- core响应该中断,通过读取 GICC_IAR 寄存器,来认可该中断。读取该寄存器,如果是软中断,返回源处理器ID,否则返回中断号。

- 当core认可该中断后,GIC将该中断的状态,修改为active状态

- 当core完成该中断后,通过写 EOIR (end of interrupt register)来实现优先级重置,写 GICC_DIR 寄存器,来无效该中断

九、中断使能和禁止

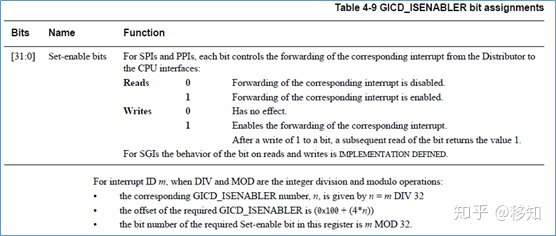

通过设置GICD_ISENABLERn寄存器,来使中断使能,通过设置GICD_ICENABLERn寄存器,来使中断禁止。 这两个寄存器,都是bit有效的寄存器,也就是一个bit,关联一个中断。 比如对于GICD_ISENABLER寄存器,描述如下:

十、中断pending

通过设置GICD_ISPENDRn或GICD_ICPENDRn寄存器,可以读取和修改中断的pending状态。这两个寄存器,也是bit有效的寄存器,一个bit,关联一个中断。

十一、中断active

通过设置GICD_ISACTIVERn或GICD_ICACTIVERn寄存器,可以读取和修改中断的active状态。这两个寄存器,也是bit有效的寄存器,一个bit,关联一个中断。

十二、产生软中断

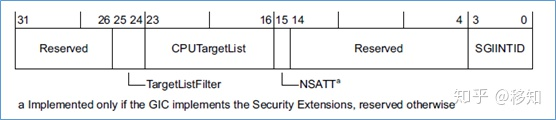

通过写 GICD_SGIR 寄存器,来产生软中断。软中断,可以指定产生中断,发往执行的core,也可以发送多个core。 对于软中断,这个是软件产生的中断。比如软件,想给执行自己的core,发送一个中断,就可以通过软中断来产生。或者软件,想起其他的core,发送一个中断,也可以通过软中断来产生。 寄存器如下:

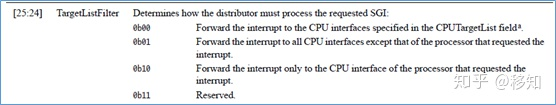

1、TargetListFileter 对于TargetListFileter:决定distributor将软中断,如何发送给cpu interface。

0b00:按照CPUTargetList的指定,来发送软中断

0b01:按照CPUTargetList的指定,来发送软中断,但是不能发送给自己

0b10:软中断,只能发送给自己

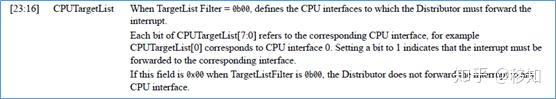

2、CPUTargetList 描述如下:

对于多core的系统,会给每个core一个编号。gicv2支持最多8个core,因此core的编号就是0-7,刚好8个bit,可以表示。 这样的CPUTargetList,就和8个cpu相对应。第0bit,表示core0,第7bit,表示core7。 如果想给core1,core2,core7发送软中断,那么此时这个位域要填入0x84。

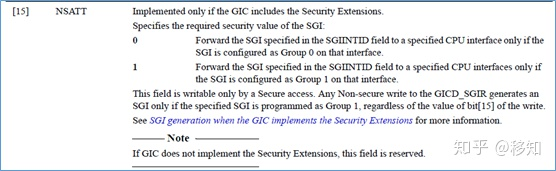

3、NSATT 描述如下:

这个用来支持安全扩展,在gicv2中,将中断进行了分组

- group0:安全中断

- group1:非安全中断

这个bit,用来表示发送的软中断,是安全中断,还是非安全中断。而且这个bit,只有core处于安全状态的时候,才能写。如果core是处于非安全状态,那么这个bit被忽略,也就是只能发非安全的软中断。

4、SGIINTID 发送的软中断的中断号。

十三、中断优先级

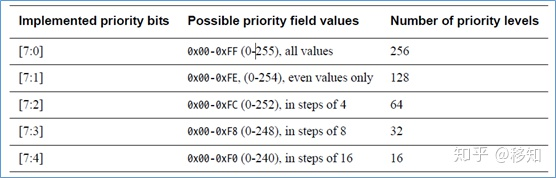

gicv2,支持最小16个,最大256个中断优先级,如下图所示:

如果实现的中断优先级小于256个,那么最低的几个bit,是为0的。 通过设置GICD_IPRIORITYRn寄存器,来设置中断的优先级。这个寄存器是字节有效的,也就是一个字节,对应一个中断的优先级。优先级数值越小,那么这个中断的优先级越高。 高优先级的中断,是可以抢占低优先级的中断。

十四、gic使用例子

下图是gic的使用例子:

外部的中断,连接到gic。由distributor进行中断分组。中断请求,由distributor发送给cpu interface,cpu interface再发送给处理器。 对于支持安全扩展,其应用如下:

安全中断,处于group0,非安全中断处于group1。

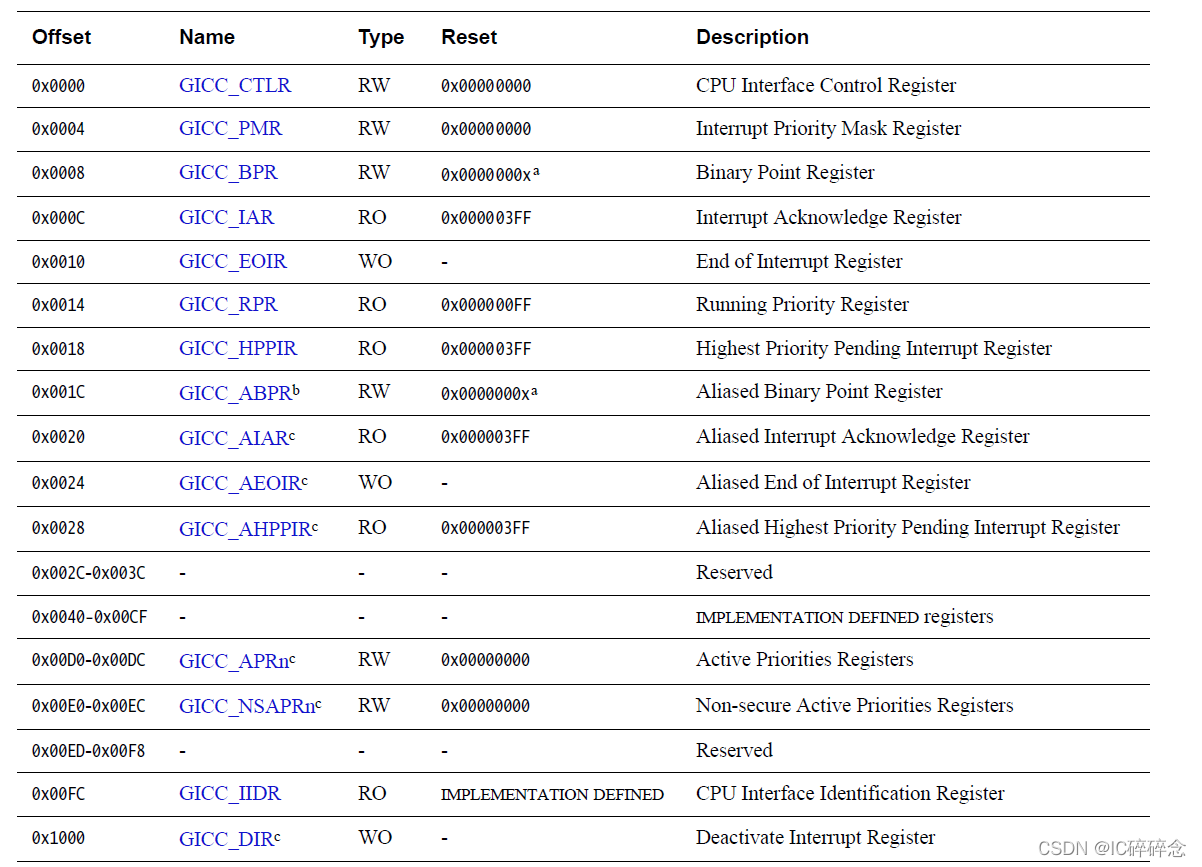

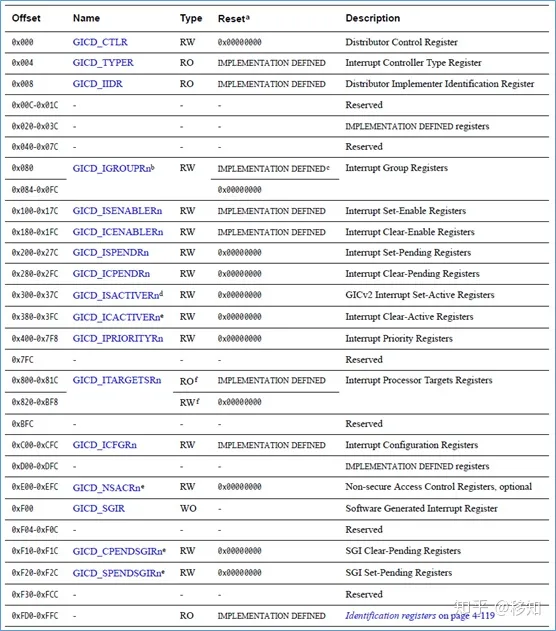

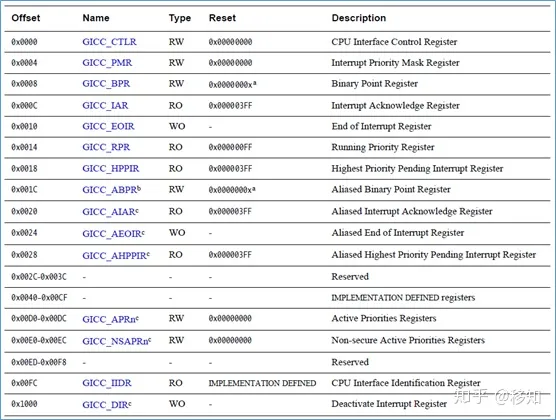

十五、gic寄存器

gic寄存器,分为两部分,一部分是distributor的寄存器,另一部分是cpu interface的寄存器。

两部分的寄存器,均是通过memory-mapped的方式来访问(有点影子寄存器)。 下图是distributor的寄存器:

下图是cpu interface的寄存器:

十六、总结

以上就是GICv2的介绍,更多的内容,需要查看gicv2的文档。

gicv2比较简单,最多只能支持8个core,超过了8个core,那么就不能使用gicv2了。

不过这也不是大问题,对于手机的arm处理器来说,最多也就8个core。

但是对于服务器,桌面级的arm处理器,那么就可能会超过8个core,此时gicv2就不适用了,所以ARM后面又加入GICv3,v4架构。

GICv2的寄存器,都是通过memory-mapped的方式访问。

但是中断在一个soc系统中,是经常会产生的,那么处理器就会经常的读取gic的寄存器,而使用memory-mapped的方式去访问,就会影响中断响应速度。

在之后的GICv3,v3中,就加入了使用系统寄存器来进行访问,加快中断处理。 GICv2只是一个gic的架构,其实现的对应的IP是gic400。

(Memory mapped I/O就是把磁盘上的file映射到内存上,当我们从内存上fetch byte时,对应的file就被读取。)

(内存映射(mmap)是一种内存映射文件的方法,即将一个文件或者其他对象映射到进程的地址空间,实现文件磁盘地址和应用程序进程虚拟地址空间中一段虚拟地址的一一映射关系。实现这样的映射关系后,进程就可以采用指针的方式读写操作这一段内存,而系统会自动回写藏页面到对应的文件磁盘上。应用程序处理映射部分如同访问主存。)

(帮助理解一下memory-mapped的含义,不断的去读取内存,猜测就是将gic的寄存器映射到了内存中,gicv3改成了访问寄存器,我们知道寄存器的读取速度比内存快多了。)