GIC400 Register

gic寄存器

gic寄存器,分为两部分,一部分是distributor的寄存器,另一部分是cpu interface的寄存器。

两部分的寄存器,均是通过memory-mapped的方式来访问。

Distribution

-

Distributor Control Register GICD_CTLR enable or disable distribution,global interrupt enable

在disable 期间,register工作正常,GICV2可以通过操作寄存器配置int的pending或active状态

-

Interrupt Controller Type Register, GICD_TYPER

• whether the GIC implements the Security Extensions

• the maximum number of interrupt IDs that the GIC supports

• the number of CPU interfaces implemented

• if the GIC implements the Security Extensions, the maximum number of implemented Lockable Shared Peripheral Interrupts (LSPIs).

-

Distributor Implementer Identification Register, GICD_IIDR

Provides information about the implementer and revision of the Distributor.

-

Interrupt Group Registers, GICD_IGROUPRn

Typically, the reset value of all GICD_IGROUPR registers is zero, so that all interrupts are Group 0 unless reprogrammed as Group 1 by Secure accesses to the appropriate GICD_IGROUPR registers.

-

Interrupt Set-Enable Registers, GICD_ISENABLERn

Disabling an interrupt only disables the forwarding of the interrupt from the Distributor to any CPU interface. It does not prevent the interrupt from changing state, for example becoming pending, or active and pending if it is already active.

- Interrupt Clear-Enable Registers, GICD_ICENABLERn

Writing a 1 to an GICD_ICENABLERn bit only disables the forwarding of the corresponding interrupt from the Distributor to any CPU interface. It does not prevent the interrupt from changing state, for example becoming pending, or active and pending if it is already active.

-

Interrupt Set-Pending Registers, GICD_ISPENDRn

-

Interrupt Clear-Pending Registers, GICD_ICPENDRn

- Interrupt Set-Active Registers, GICD_ISACTIVERn

- Interrupt Clear-Active Registers**, GICD_ICACTIVERn**

- Interrupt Priority Registers, GICD_IPRIORITYRn

- These registers are byte-accessible

- The GICD_IPRIORITYRs provide an 8-bit priority field for each interrupt supported by the

GIC. This field stores the priority of the corresponding interrupt. 256 - A GIC might implement fewer than eight priority bits, but must implement at least bits [7:4]

of each field. - The number of implemented GICD_IPRIORITYRs is (8*(GICD_TYPER.ITLinesNumber+1)).

- The lower the value, the greater the priority of the corresponding interrupt.

-

Interrupt Processor Targets Registers, GICD_ITARGETSRn

- The GICD_ITARGETSRs provide an 8-bit CPU targets field for each interrupt supported by the GIC.

- These registers are byte-accessible.

- Has no effect on any active interrupt. This means that removing a CPU interface from a targets list does not cancel an active state for that interrupt on that CPU interface.Has an effect on any pending interrupts.

- The registers that contain the SGI and PPI interrupts are read-only and the value is the CPU number of the current access

- GICD_ITARGETSR0 to GICD_ITARGETSR7 are read-only, and each field returns a value that corresponds only to the processor reading the register.

-

Interrupt Configuration Registers, GICD_ICFGRn

- The GICD_ICFGRs provide a 2-bit Int_config field for each interrupt supported by the GIC.

- Before changing the value of a programmable Int_config field, software must disable the

corresponding interrupt, - The number of implemented GICD_ICFGRs is (2*(GICD_TYPER.ITLinesNumber+1)).

- SGI is level_sensitive

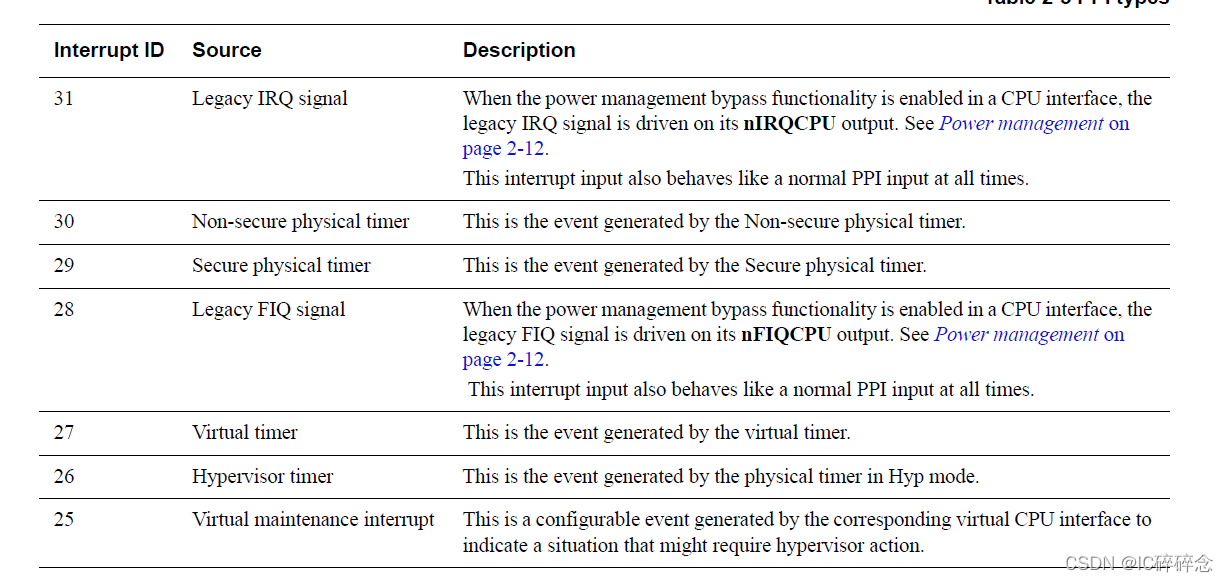

- Private Peripheral Interrupt Status Register, GICD_PPISR

- Enables a processor to access the status of the PPI inputs on the Distributor.

- A processor can only read the status of its own PPI and cannot read the status of PPIs for other processors

-

Shared Peripheral Interrupt Status Registers, GICD_SPISRn

Enables a processor to access the status of the IRQS inputs on the Distributor.

-

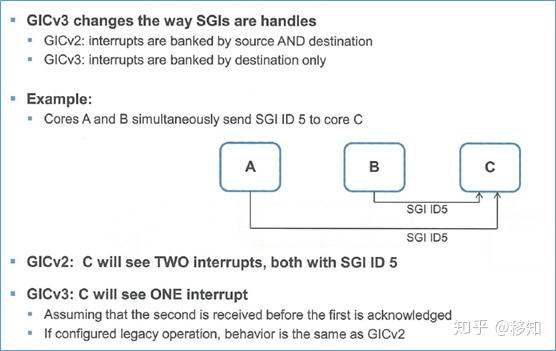

Software Generated Interrupt Register, GICD_SGIR

Controls the generation of SGIs.

...

-

SGI Clear-Pending Registers, GICD_CPENDSGIRn

The GICD_CPENDSGIRs provide a clear-pending bit for each supported SGI and source processor combination

-

SGI Set-Pending Registers, GICD_SPENDSGIRn

The GICD_SPENDSGIRn registers provide a set-pending bit for each supported SGI and source processor combination.

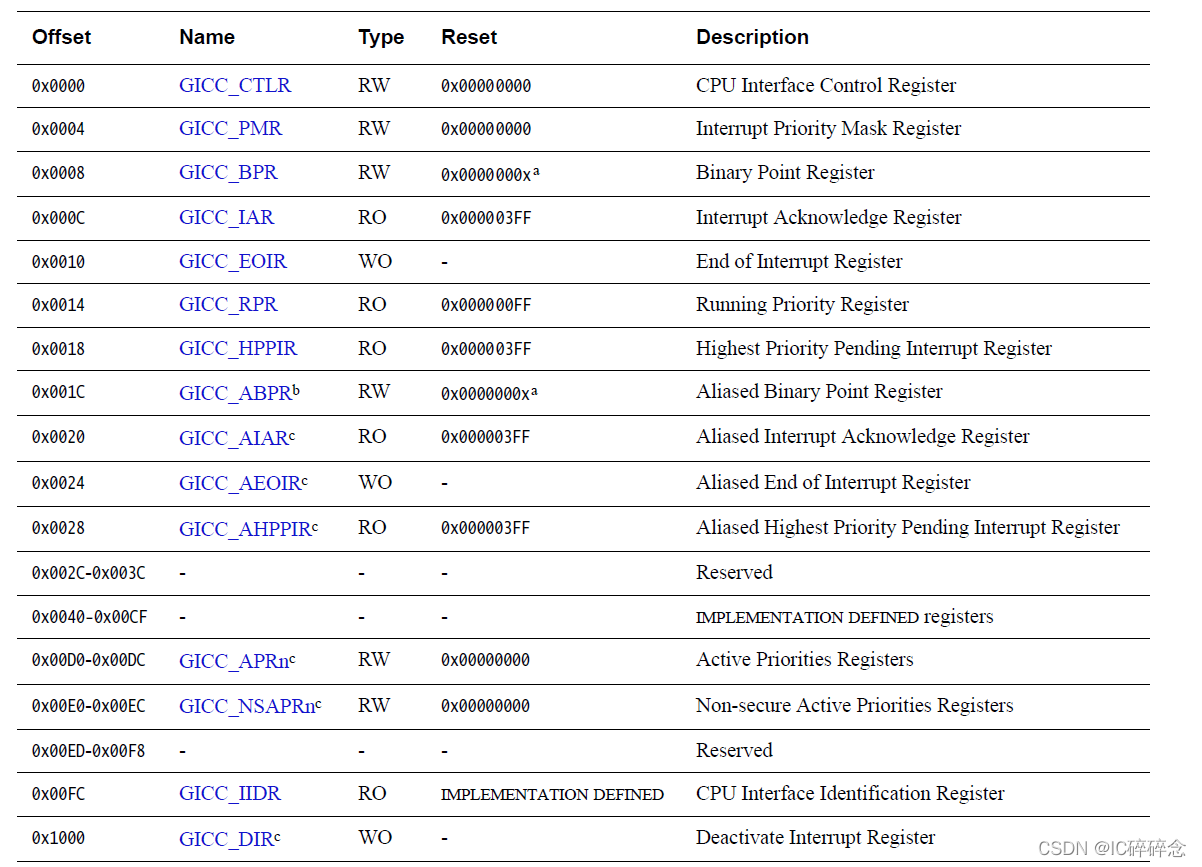

CPU interface

GICC_CTLR(0x0000):CPU Interface Control,控制中断是否传给CPU核,控制中断是IRQ还是FIQ

GICC_PMR(0x0004):Priority Mask,控制优先级门限,低于门限的中断不会转发到CPU

GICC_BPR(0x0008):Binary Point Register,是将优先级分成2部分:Group priority 、Subpriority,只使用优先级的Group priority部分,忽略Subpriority部分

详解:比如GIC-400的默认值是2,则优先级的[7:3]作为Group priority ,[2:0]作为Subpriority,则总共可生成32个优先级,与GICD_IPRIORITYRn保持一致

GICC_IAR(0x000C):Interrupt Acknowledge,只读,可以查看当前pending的最高优先级中断

GICC_EOIR(0x0010):End of Interrupt,只写,中断处理完成后需要写该寄存器

GICC_RPR(0x0014):Running Priority,只读,当前处理中断的优先级

GICC_HPPIR(0x0018):Highest Priority Pending ,只读,处于active状态的中断里优先级最高的

GICC_IIDR(0x00FC):ID寄存器,GIC-400的值是0x0202143B

GICC_DIR(0x1000):Deactivate Interrupt ,只写,移除中断的Active状态

GICC_IIDR(0x00FC):ID寄存器,GIC-400的值是0x0202143B

GICC_DIR(0x1000):Deactivate Interrupt ,只写,移除中断的Active状态

GICC_APRn 为在电源管理中保存和恢复状态提供支持 。

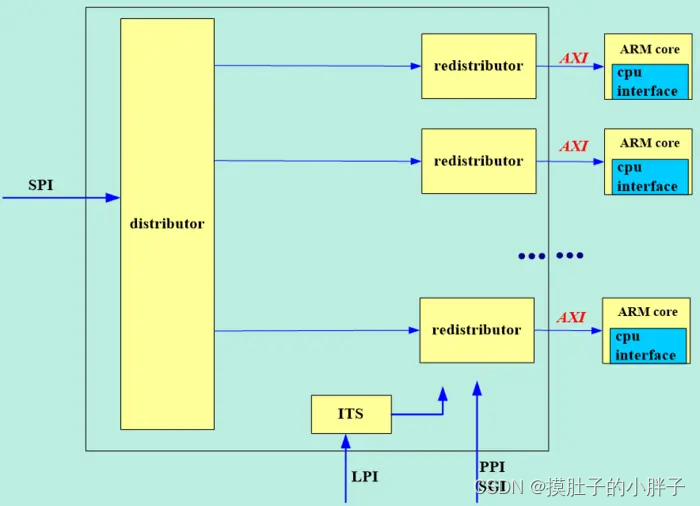

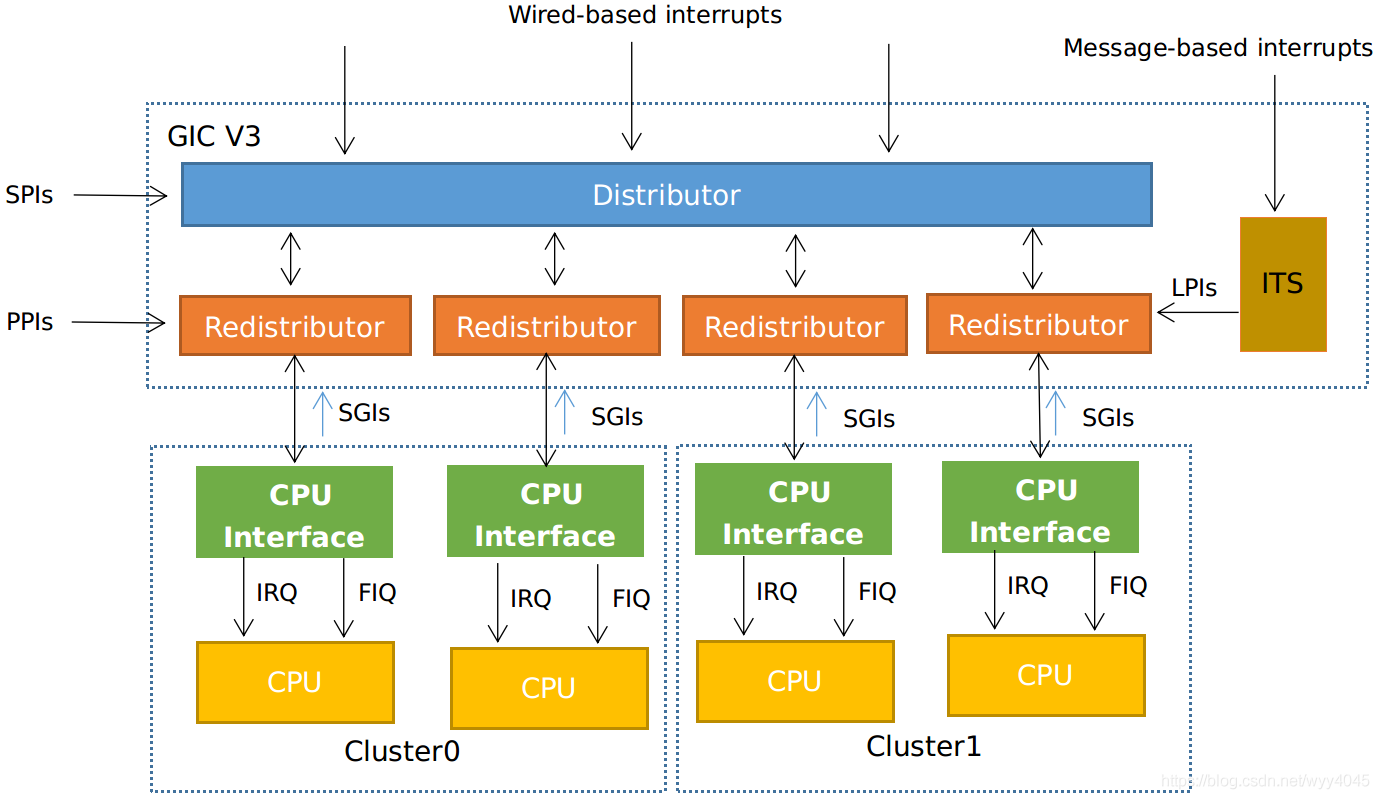

![[gic]-ARM gicv3/gicv4的详细介绍-2020/08](http://assets.processon.com/chart_image/604719347d9c082c92e419de.png)