目录

一、前言

二、BLACK_BOX

2.1 属性说明

2.2 工程代码

2.3 结果

一、前言

在调试中,有时不需要知道一个模块或实例的具体实现,或者需要使其对外属于不可见,只知道它的输入输出,即像一个黑盒,此时可以对模块设置BLACK_BOX属性。

二、BLACK_BOX

2.1 属性说明

Verilog设计可以包含由综合工具、方案文本编辑器,或其他的设计输入机制生成的EDIF文件,这些模块也必须被实例化连接到工程中。我们可以通过对模块设置BLACK_BOX属性,通过对模块实例化的每个实例都具有BLACK_BOX属性。

2.2 工程代码

将BLACK_BOX模块设计BLACK_BOX属性,在模块sum中进行调用

(* BLACK_BOX *)module BLOCK_BOX(in1,in2,out );

input in1,in2;

output out;

assign out=in1+in2;

endmodule

module sum(a,b,sum);

input a,b;

output sum;

BLOCK_BOX test(.in1(a),.in2(b),.out(sum));

endmodule

2.3 结果

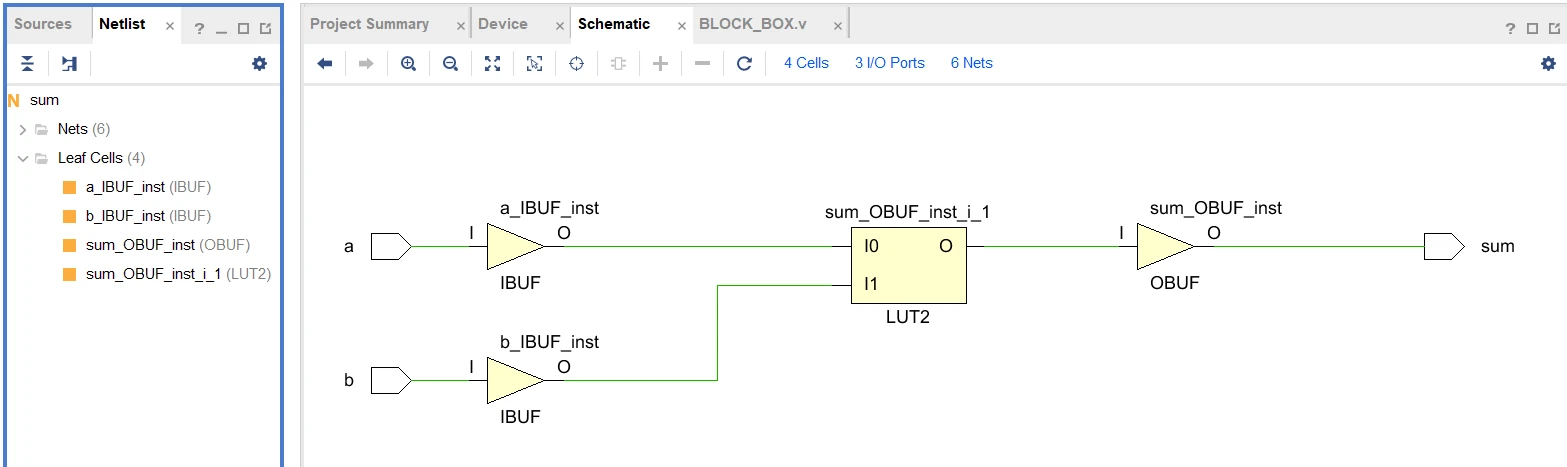

查看综合后的网表图,实例化对象test为一个黑盒,只能看出输入输出,无法知道具体实现,左侧网表列表中也是作为一个Inst存在。

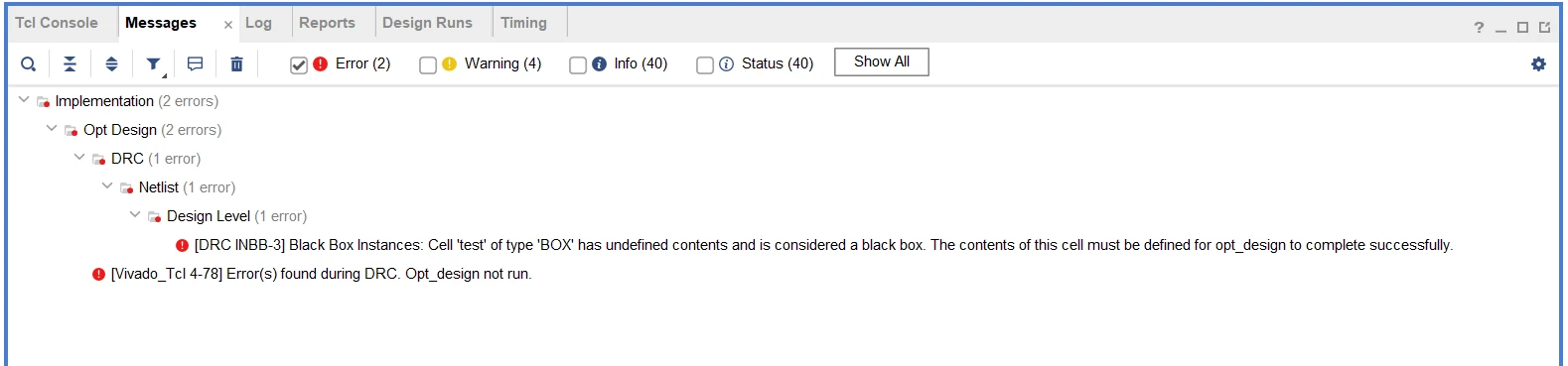

运行Implement时会报DRC错误,因为作为一个黑盒时是无法知道其内部实现,因此无法Implement。

当把属性black_box去掉时,综合网表如下图,此时Schematic直接显示实现方法,