一、LAN8720A----简介

LAN8720A 是低功耗的 10/100M 以太网 PHY 层芯片,I/0 引脚电压符合EEE802.3-2005 标准,支持通过 RMI 接口与以太网 MAC 层通信,内置 10-BASE-T/100BASE-TX 全双工传输模块,支持 10Mbps 和 100Mbps。

LAN8720A 可以通过自协商的方式与目的主机最佳的连接方式(速度和双工模式),支持 HPAuto-MDIX 自动翻转功能,无需更换网线即可将连接更改为直连或交又连接。

LAN8720A 的主要特点如下:

- 高性能的 10/100M 以太网传输模块

- 支持 RMII 接口以减少引脚数

- 支持全双工和半双工模式

- 两个状态 LED 输出

- 可以使用 25M 晶振以降低成本

- 支持自协商模式

- 支持 HP Auto-MDIX 自动翻转功能

- 支持 SMI 串行管理接口

- 支持 MAC 接口

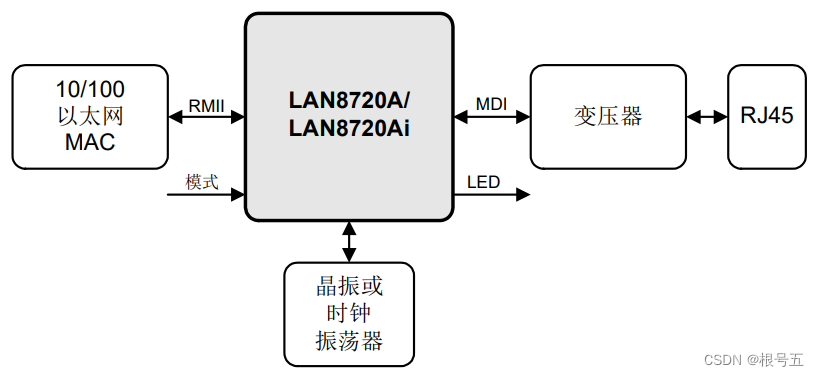

LAN8720A----系统框图

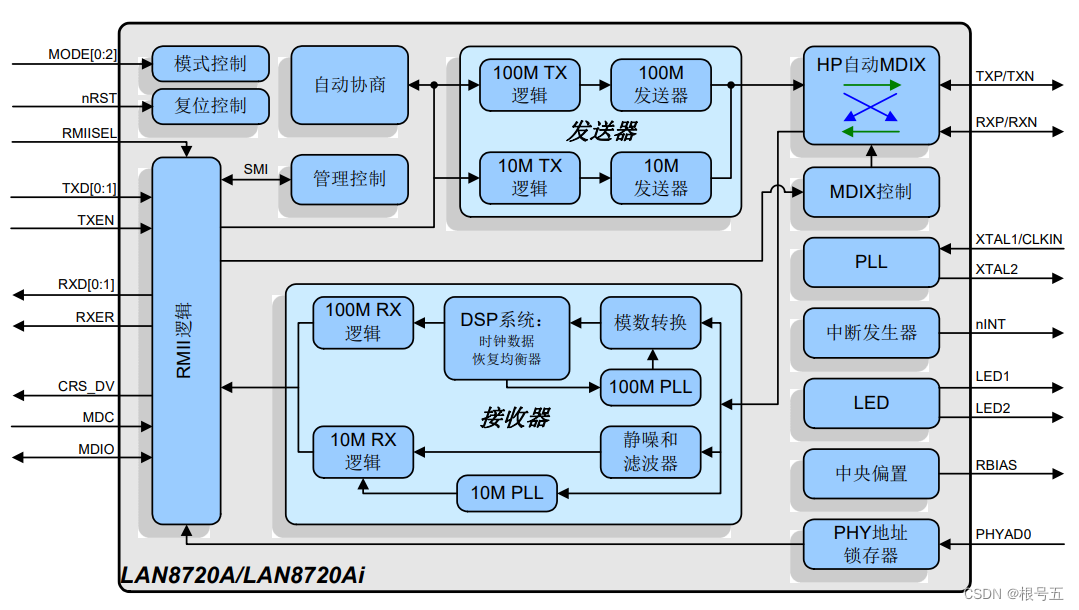

LAN8720A----内部架构

二、LAN8720A----引脚说明

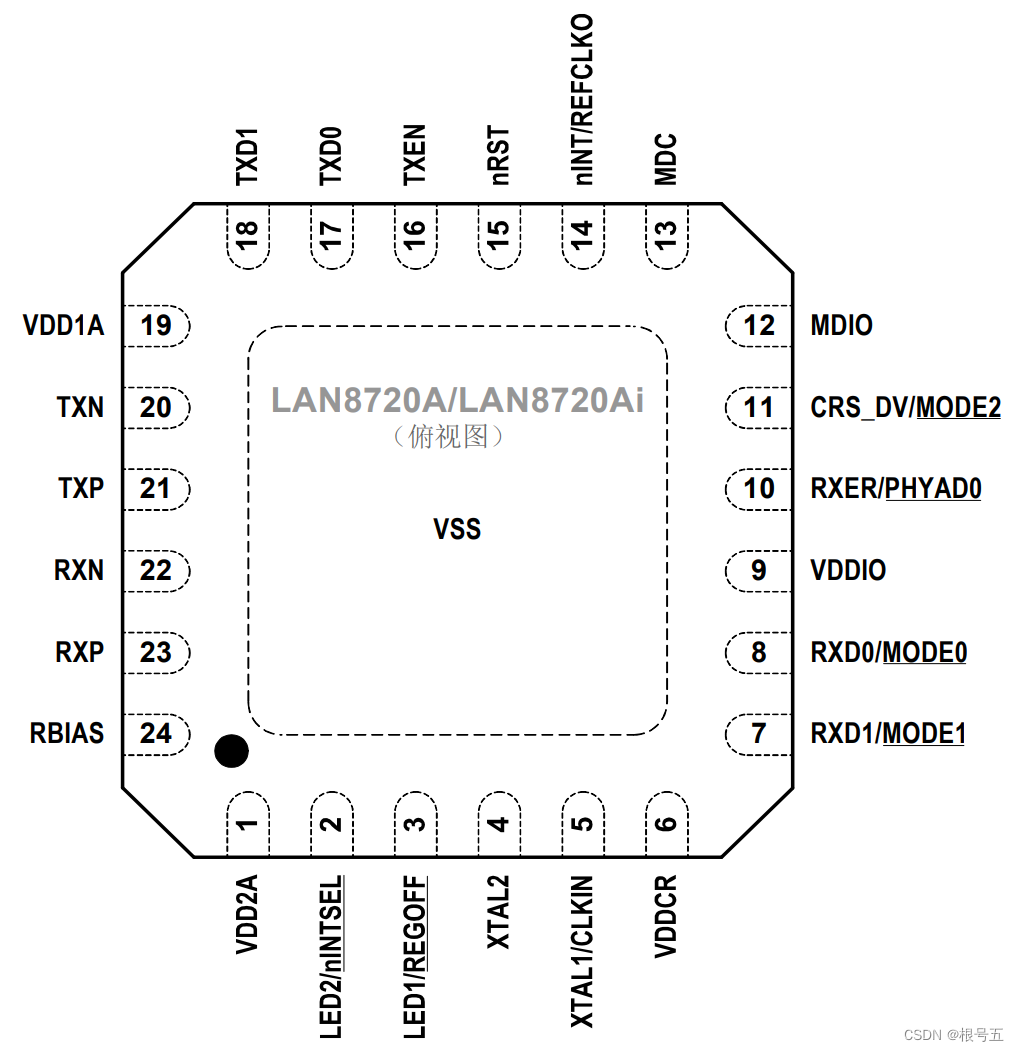

LAN8720A----引脚图

LAN8720A----引脚说明表

| 引脚编号 | 符号 | 名称 | 说明 |

|---|---|---|---|

| 1 | VDD2A | +3.3V通道2模拟端口电源 | 通道2和内部稳压器的+3.3V模拟端口电源 |

| 2 | LED2 | 链路速度LED指示 | 当工作速度为100 Mbps时,该引脚将驱动为有效状态。 当工作速度为10 Mbps时,或者线路隔离期间,该引脚处于无效状态。 |

| nINTSEL | 14引脚(nINT/REFCLKO) 功能选择配置引脚 | 当引脚 悬空或拉高至 VDD2A 时(默认),REF_CLK输入模式,nINT/REFCLKO是低电平有效的中断输出。 当引脚拉低接地时,REF_CLK输出模式,nINT/REFCLKO是REF_CLK的时钟源。 | |

| 3 | LED1 | 链路活动LED指示 | 该引脚在检测到有效链路时,驱动为有效状态,在检测到活动时闪烁。 |

| REGOFF | 稳压器关闭配置脚 | 该配置脚用于禁止内部1.2V稳压器。禁止稳压器时,必须向VDDCR提供外部1.2V电压。 当REGOFF通过外部电阻拉高至VDD2A时,禁止内部稳压器。 当REGOFF悬空或拉低时,使能内部稳压器 (默认)。 | |

| 4 | XTAL2 | 外部晶振输出 | 外部晶振输出 |

| 5 | XTAL1 | 外部晶振输入 | 外部晶振输入 |

| CLKIN | 外部时钟输入 | 单端时钟振荡器输入。 注:使用单端时钟振荡器时,不得连接XTAL2。 | |

| 6 | VDDCR | +1.2V数字内核电源 | 除非通过REGOFF 配置脚配置为稳压器关闭模式,否则由片上稳压器供电。 注: 应在该引脚上使用并联接地的1 μF和470 pF 去耦电容。 |

| 7 | RXD1 | 接收数据1 | 收发器在接收路上的通道1。 |

| MODE1 | PHY工作模式1配置脚 | 该配置脚搭配MODE0和MODE2用于设置默认PHY 模式。 | |

| 8 | RXD0 | 接收数据0 | 收发器在接收路上的通道0。 |

| MODE0 | PHY工作模式0配置脚 | 该配置脚搭配MODE1和MODE2用于设置默认PHY模式。 | |

| 9 | VDDIO | +1.6V到+3.6V可变I/O电源 | +1.6V到+3.6V可变I/O电源 |

| 10 | RXER | 接收错误 | 该信号置为有效时表示在当前从收发器传输的帧中检测到错误。 |

| PHYAD0 | PHY地址0配置脚 | 该配置脚用于设置收发器的SMI地址。 | |

| 11 | CRS_DV | 载波侦听/接收数据有效 | 该信号置为有效时表示接收介质处于非空闲状态。当接收到10BASE-T数据包时,CRS_DV置为有效,但RXD[1:0]保持低电平,直到接收到SFD字节(10101011)为止。 注: 根据RMII标准,在10BASE-T半双工模式 下,发送的数据不环回到接收数据引脚。 |

| MODE2 | PHY工作模式2配置脚 | 该配置脚搭配MODE0和MODE1用于设置默认PHY模式。 | |

| 12 | MDIO | SMI数据输入/输出 | 串行管理接口数据输入/输出 |

| 13 | MDC | SMI时钟 | 串行管理接口时钟 |

| 14 | nINT | 中断输出 | 低电平有效中断输出。放置一个上拉至VDDIO的外部电阻 |

| REFCLKO | 参考时钟输出 | REFCLKO可通过nINTSEL配置脚来选择。 此可选50MHz时钟输出源于25MHz晶体振荡器。 | |

| 15 | nRST | 外部复位 | 系统复位。该信号低电平有效。 |

| 16 | TXEN | 发送使能 | 指示TXD[1:0]上存在有效的发送数据。 |

| 17 | TXD0 | 发送数据0 | MAC使用该信号将数据发送到收发器。 |

| 18 | TXD1 | 发送数据1 | MAC使用该信号将数据发送到收发器。 |

| 19 | VDD1A | +3.3V通道1模拟端口电源 | 通道1的+3.3V模拟端口电源 |

| 20 | TXN | 以太网TX/RX负通道1 | 发送/接收负通道1 |

| 21 | TXP | 以太网TX/RX正通道1 | 发送/接收正通道1 |

| 22 | RXN | 以太网TX/RX负通道2 | 发送/接收负通道2 |

| 23 | RXP | 以太网TX/RX正通道2 | 发送/接收正通道2 |

| 24 | RBIAS | 外部1%偏置电阻输入 | 该引脚需要通过12.1 kΩ(1%)电阻接地。 |

三、LAN8720A----电路原理图

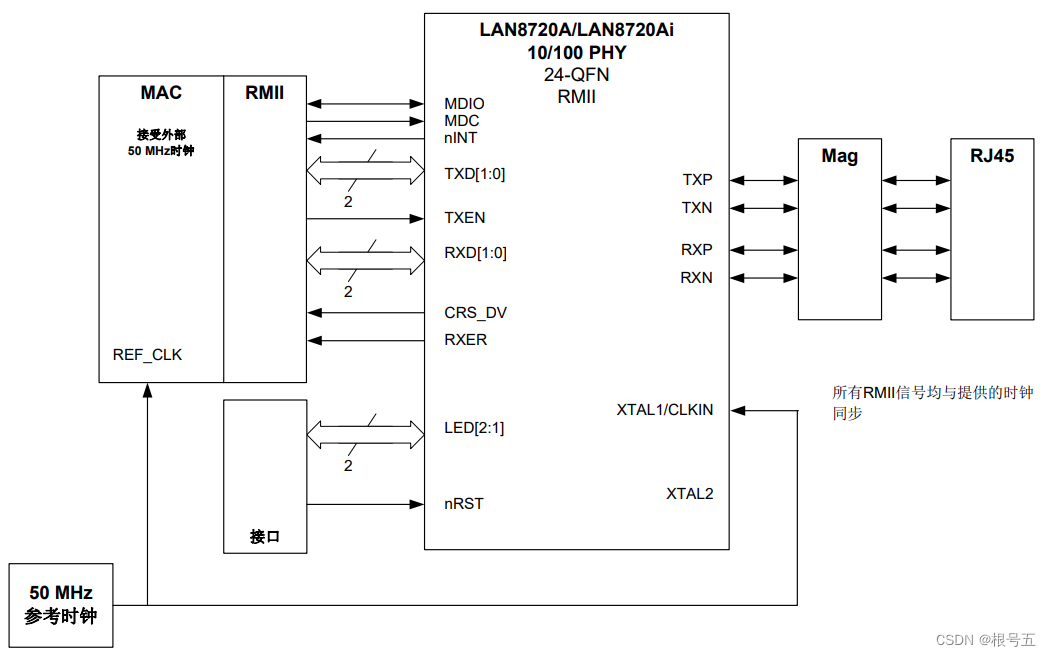

1. REF_CLK输入模式

在REF_CLK输入模式下,50 MHz REF_CLK在XTAL1/CLKIN引脚上进行驱动。

使用该模式时,必须在器件外部为 REF_CLK提供50 MHz时钟源,该时钟被驱动到MAC和PHY。

为REF_CLK提供外部50 MHz时钟源,具体如下图:

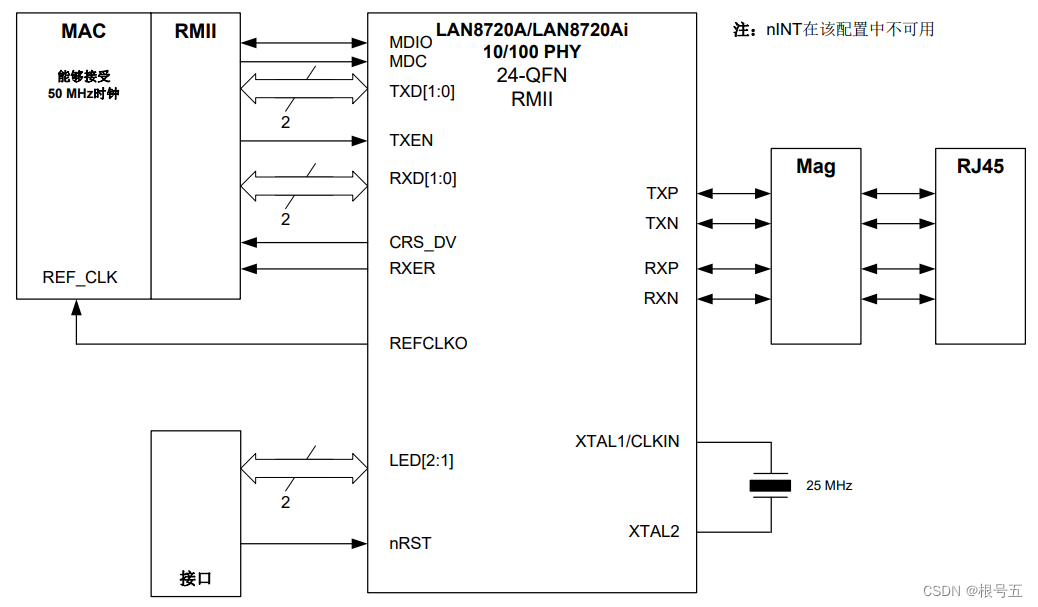

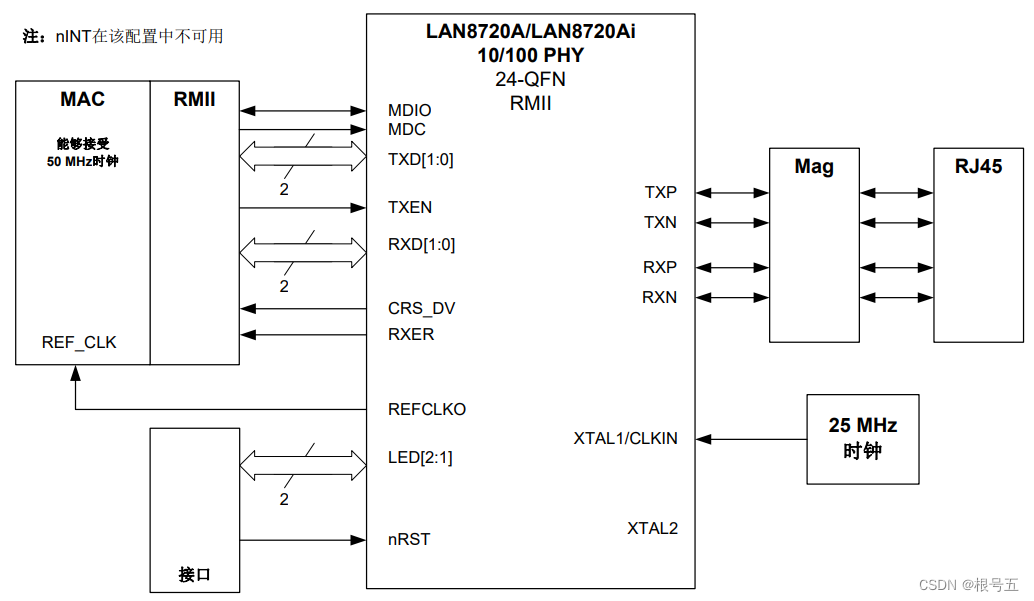

2. REF_CLK输出模式

为降低BOM成本,该器件配备通过低成本25 MHz基频晶振来生成RMII REF_CLK信号的功能。

与通常需要50 MHz的3次谐波晶振相比,这类晶振价格更低廉。MAC必须支持外部时钟才能使用该功能。

通过25 MHz晶振生成REF_CLK,具体如下图:

通过外部25 MHz时钟源生成REF_CLK,具体如下图:

未完,待续。。。。。