1.1.1 ARM的商业模式

ARM(Advance RISC(Reduced Instruction set Computer) Machine 高级精简指令集机器)公司自身不制造处理器硬件,而是设计处理器,并将其设计授权给商业合作伙伴,使他们将其用于制作自己的SOC(System-on-Chip片上系统)。

ARM公司定义体系结构--授权商依其制作ARM处理器--授权商将处理用于其他机器

ARM体系结构定义文件:ARM公司提供;

ARM处理器定义文件:授权商提供;

ARM器件:授权商提供;

1.1.2 ARM体系结构

1.RICS and CICS(Complex Instruction Set Computer 复杂指令集)

RISC 和CISC 是目前设计制造微处理器的两种典型技术,虽然它们都是试图在体系结构、操作运行、软件硬件、编译时间和运行时间等诸多因素中做出某种平衡,以求达到高效的目的,但采用的方法不同,因此,在很多方面差异很大,它们主要有:

(1) 指令系统:RISC 设计者把主要精力放在那些经常使用的指令上,尽量使它们具有简单高效的特色。对不常用的功能,常通过组合指令来完成。因此,在RISC 机器上实现特殊功能时,效率可能较低。但可以利用流水技术和超标量技术加以改进和弥补。而CISC 计算机的指令系统比较丰富,有专用指令来完成特定的功能。因此,处理特殊任务效率较高。

(2) 存储器操作:RISC 对存储器操作有限制,使控制简单化;而CISC 机器的存储器操作指令多,操作直接。

(3) 程序:RISC 汇编语言程序一般需要较大的内存空间,实现特殊功能时程序复杂,不易设计;而CISC 汇编语言程序编程相对简单,科学计算及复杂操作的程序设计相对容易,效率较高。

(4) 中断:RISC 机器在一条指令执行的适当地方可以响应中断;而CISC 机器是在一条指令执行结束后响应中断。

(5) CPU:RISC CPU 包含有较少的单元电路,因而面积小、功耗低;而CISC CPU 包含有丰富的电路单元,因而功能强、面积大、功耗大。

(6) 设计周期:RISC 微处理器结构简单,布局紧凑,设计周期短,且易于采用最新技术;CISC 微处理器结构复杂,设计周期长。

(7) 用户使用:RISC 微处理器结构简单,指令规整,性能容易把握,易学易用;CISC微处理器结构复杂,功能强大,实现特殊功能容易。

(8) 应用范围:由于RISC 指令系统的确定与特定的应用领域有关,故RISC 机器更适合于专用机;而CISC 机器则更适合于通用机。

常用的精简指令集微处理器包括DECAlpha、ARC、ARM、AVR、MIPS、PA-RISC、PowerArchitecture(包括PowerPC)和SPARC等。

复杂指令集微处理器是英特尔生产的x86系列(也就是IA-32架构)CPU及其兼容CPU,如AMD、VIA的。即使是现在新起的X86-64(也被称为AMD64)都是属于CISC的范畴。

流水线技术:流水线(pipeline)技术是指在程序执行时多条指令重叠进行操作的一种准并行处理实现技术。流水线是Intel首次在486芯片中开始使用的。流水线的工作方式就象工业生产上的装配流水线。在CPU中由5—6个不同功能的电路单元组成一条指令处理流水线,然后将一条X86指令分成5—6步后再由这些电路单元分别执行,这样就能实现在一个CPU时钟周期完成一条指令,因此提高CPU的运算速度。经典奔腾每条整数流水线都分为四级流水,即取指令、译码、执行、写回结果,浮点流水又分为八级流水。

2.ARM体系结构版本

ARMv7之前,每一版本架构相同,只是处理器的实现不同,但ARMv7为不同市场应用定义了不同的架构。

A:定义了支持VMSA的多模式、高性能微处理器架构,支持ARM和Thumb2变种的ThumbEE指令集;

R:定义了支持PMSA的多模式实时微处理器架构,用于要求时间确定性和低中断延时的系统,支持ARM和Thumb2指令;

M:定义了低中断延时的微处理器架构,可由高级编程语言直接访问中断处理器。实现了变种了的PMSA,具有不同的例外事件处理模式,只支持Thumb2指令集;

Ps:

MMU:Memory Management Unit 存储器管理模块;

VMSA:Virtual Memory System Architecture虚拟存储系统结构;

MPU:Memory Protection Unit 存储器保护单元;

PMSA:Protected Memory System Architecture 保护存储系统结构;

3、指令集

ARM体系采用两种指令集:ARM指令集和Thumb指令集;

关系:Thumb指令集是ARM指令集的子集;

ARM指令集:32位指令集,效率高,存储空间大;

Thumb指令集:16位指令集,效率低,存储空间小;

Thumb指令集:Thumb-1和Thumb-2,Thumb-2在1的基础上进行了扩展,增加了32位的指令集,功能基本与ARM指令集相同,而且省去了ARM指令集与Thumb指令集之间的切换时间,所以基于ARMv7-M架构的Cortex-M3F和Cortex-M4F仅使用Thumb-2指令集;

4、存储模式

32位处理器是指一次能处理32位数据的处理器;

ARM存储器采用单一的地址空间,范围为2^32字节(4GB)或2^30(32bit)字,或2^31半字(16bit);

存储器访问模式特点:

A、非对齐的内存访问;

B、可限制访问指定的存储器空间;

C、可将指令的虚拟地址映射为物理地址;

D、可进行字和半字的转换;

E、可选择防止无序的存储器访问;

F、可以控制内存;

G、多个处理器可同步访问共享存储器;

Ps:对齐的内存访问:

虚拟地址映射为物理地址:

5、调试

从ARMv6开始

侵入式调试:允许修改处理器状态,此时处理器处于停止工作状态,主要用于运行控制调试;

非侵入式调试:不中断执行流程不修改处理器状态,运行观察数和程序流程;

ARM体系提供的调试功能有:

A、指令集数据跟踪;

B、程序计数器采样;

C、性能观测;

1.1.3 ARM微处理器

Cortex-M4F微处理器实现了ARMv7-M体系结构;Cortex-A9实现ARMv7-A体系结构;

1.2 ARM Cortex-M4F微处理器

1.2.1特点

Cortex-M4F是基于ARMv7-M架构的32位处理器,用于满足简单高效的控制和信号处理功能混合的应用市场。

特点:

A、为满足封装管脚小、存储容量小、功耗低而设计的高性能低成本内核;

B、只采用Thumb-2指令集,避免了与ARM指令集间的切换开销;

C、通过硬件实现信号处理功能,如遵循IEEE754协议的FPU(floating-point unit单精度浮点运算单元);

D、采用三级流水线的哈佛结构,地址与数据总线分离;

E、三条AHB-Lite(Advanced High-Performance Bus-Lite精简高级高性能总线),分别用于地址、数据和系统,两条APB(Advanced Peripheral Bus高级外设总线)用于外设;

F、可选的存储保护单元MPU为操作系统提供特权操作模式,用于安全要求高的应用;

G、与处理器内核紧密集成的嵌套向量中断控制器NVIC(Nested Vectored Interrupt Controller)使得中断延迟很低,对时间苛刻的应用提供可确定的、高性能的中断处理;

H、位带操作(bit-band)可以在存储器映射的特定区域(SRAM和外设空间)使用地址别名访问对应的位带区域每个位,内存利用最大化,外设控制更高效;

I、支持非对齐的数据访问,数据放入内存更有效;

J、优化的单周期访问Flash,程序代码、数据访问更迅速;

K、支持睡眠和深度睡眠,功耗更低;

串行调试和跟踪接口通过较少的引脚即可实现调试、跟踪和代码分析,提供全方位断点和跟踪能力;

1.2.3 Cortex-M4F微处理器的编程模型

编程模型是指处理器的运行模式。包括:

主模式(Thread mode):执行应用软件的基本模式,复位后进入;

中断模式(Handler mode):处理异常的模式,所有异常在该模式下执行,执行完后返回主模式;

特权模式:执行所有指令,访问所有资源;

非特权模式:执行有限指令和访问有限资源;

主模式可选择特权或者非特权模式,中断模式只执行非特权模式;

1.2.4 Cortex-M4F内核寄存器

(1)13个32位的通用寄存器R0-R12,通用寄存器中R8-R12只能被32位指令访问,不能被16位指令访问;

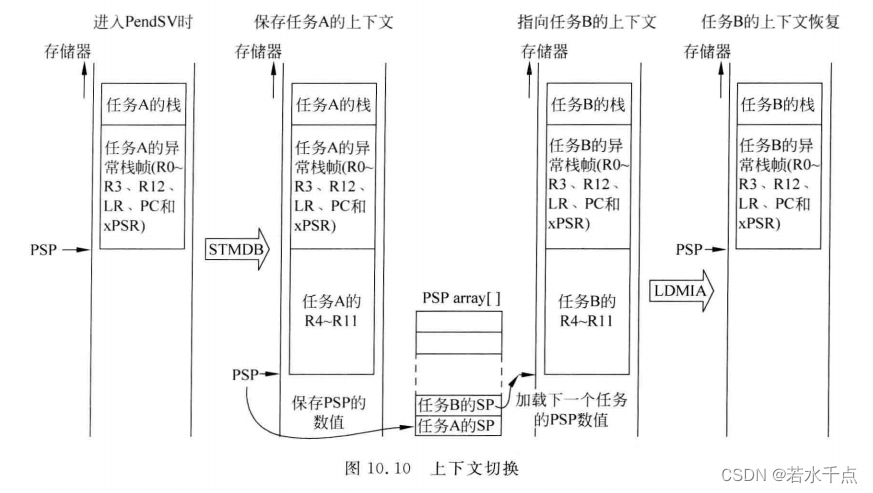

(2)堆栈指针寄存器SP(Stack Pointer)PR13,在线程模式下,SP的功能取决于控制寄存器CONTROL的ASP位,当该位置位时,SP为PSP(Process Stack Pointer)进程堆栈指针寄存器,当该位置零时,SP为MSP(Main Stack Pointer)主堆栈指针寄存器,其中MSP只能在特权模式下被访问,而PSP可在特权、非特权模式下访问;

(3)链接寄存器LR(Link Register)R14,用于接收程序计数器PC的跳转指令(BL、BLX)的程序返回地址,也可用于存储子程序、函数调用、中断等的返回信息,其他时间可做一般寄存器;

(4)程序计数器PC(Program Counter)R15,用于保存当前程序地址;

(5)五个特殊用途寄存器:程序状态寄存器PSR(Program Status Register)用于保存当前程序的执行状态信息,控制寄存器CONTROL用于指定堆栈指针寄存器以及线程模式下的中断特权等,三个中断屏蔽寄存器——优先级屏蔽寄存器PRIMASK用于阻止具有可配置优先级的中断被激活、故障屏蔽寄存器FAUKTMASK用于阻止除NMI外的所有中断被激活、基本优先级屏蔽寄存器BASEPRI用于阻止所有优先级小于或等于设定值的中断被激活;

1.2.5 Cortex-M4F存储器映射

4GB分为8个区;

1.存储器空间的8个区域

代码区(code):大小为0.5g,存放程序代码,指令通过ICode总线访问,数据通过DCode总线访问;

内部SRAM区:大小为0.5G,存放数据,指令和数据均通过系统总线(System Bus)访问;

内核外设区(Peripheral):大小为0.5G,指令和数据均通过系统总线访问;

外部RAM区(External RAM):大小为1G,指令和数据均通过系统总线访问;

外部设备区(External Device):大小为1G,指令和数据均通过系统总线访问;

PPB内部总线区(Private Peripheral Bus-Internal):大小为256KB,通过内部PPB总线访问,为不可执行区域;

PPB外部总线区(Private Peripheral Bus-External):大小为768KB,通过内部PPB总线访问,为不可执行区域;

系统区(System):大小为511M,器件制造商的系统外设区,不可执行区域;

2、位带空间(Bit-band region)和位带别名空间(Bit-band alias)

位带功能将减少读-修改-写的时间,将以字为单位的位带别名空间映射到以位为单位的位带空间,将位带别名空间的某个字的最低位写入0或1,相应的位带空间的位置0或1,读取位带别名空间的某个字,读取结果的最低位代表位带空间最低位的值;

1.2.7 Cortex-M4F的异常处理

1、特点

出现异常,产生中断,处理器状态自动存储到堆栈中,并在中断服务程序ISR(Interrupt Service Routine)结束时自动从堆栈中恢复。NVIC取出中断向量和保存状态是同时进行的,提高了进入中断的效率。处理器还具有末尾连锁功能(tail-chaining),即当两个相邻中断发生时,前一个中断处理结束后,无需退出恢复,而是直接执行下一个中断,减少了中断响应时间;

2、异常类型

10钟异常和96个中断。

3、异常优先级

可编程的优先级可通过NVIC的中断优先寄存器PRIn来设置。分抢占优先级和子优先级两组;优先级最高为-3,可设置的优先级为0-7,默认为0,优先级相同,向量号小的先执行;更高级别的异常发生时,正在处理的异常将被其抢占;

4、异常状态

待用:没有发生异常;

悬挂:有一个异常等待处理器处理;

激活:有一个异常正在被处理器处理;

激活并悬挂:有一个异常正在被处理器处理,但是又有一个同样的异常被悬挂;

5、异常处理器

(1)中断服务程序ISR;

(2)故障处理器:四种故障;

(3)系统处理器:10钟异常,包括4种故障异常。