#include <iostream>

using namespace std;

class Adder

{

private:int num;

public:Adder(int n=0);//有参构造函数,其中参数默认值为0Adder(const Adder &adder);//拷贝构造函数~Adder();//析构函数void setNum(int n);//公有函数,用于设置数值域int getNum() const;//公有函数,用于返回数值域Adder operator+(Adder &a);//重载+运算符Adder& operator++(void);//前置++运算符重载const Adder operator++(int);//后置++运算符重载void show() const;//显示

};

Adder::Adder(int n)//有参构造函数的实现

{num=n;cout<<"Adder Constructor run"<<endl;

}

Adder::Adder(const Adder &adder)//拷贝构造函数的实现

{num = adder.num;cout<<"Adder CopyConstructor run"<<endl;

}

Adder::~Adder()//析构函数的实现

{cout<<"Adder Destructor run"<<endl;

}

void Adder::setNum(int n)

{num=n;

}

int Adder::getNum()const

{return num;

}

Adder Adder::operator+(Adder &a)//重载+运算符

{this->num = this->num + a.num;return (Adder(getNum()));

}

Adder& Adder::operator++(void)//前置重载++运算符

{num++;return *this;

}

const Adder Adder::operator++(int)//后置重载++运算符

{Adder ad=*this;++(*this);return ad;

}

void Adder::show()const

{cout<<"Adder("<<num<<")"<<endl;

}

//主函数

int main(void){int x;Adder a1,a2(a1);cin>>x;(a1++).show();a1.show();a2.setNum(x);(++a2).show();a2.show();(a1+a2).show();return 0;

}

C++设计并实现加法器类Adder

news/2025/1/24 22:39:48/

相关文章

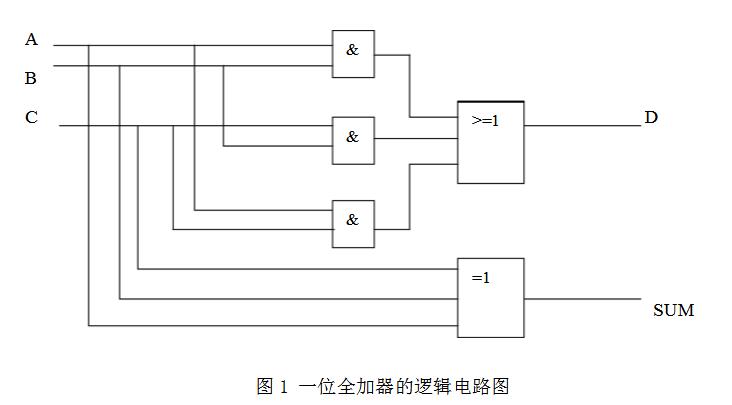

carry-lookahead adder 超前进位加法器

关于Carry-lookahead Adder(CLA) 超前进位加法器:

首先,不超前是什么,不超前就是按顺序,从低位到高位的加。高位要等低位先做,低位做完把结果给高位,高位再接着做。这就是由全加器(Full adder&…

超前进位加法器(Carry-Lookahead Adder,CLA)

传统加法器在多比特位宽的情况下,相加会有较多的门延迟,每高一位比特的相加都需要低一级相加并提供进位后,再进行本比特的加法运算,多位宽在高速情况下容易造成时序问题,无法在一个时钟内完成相应运算,故而…

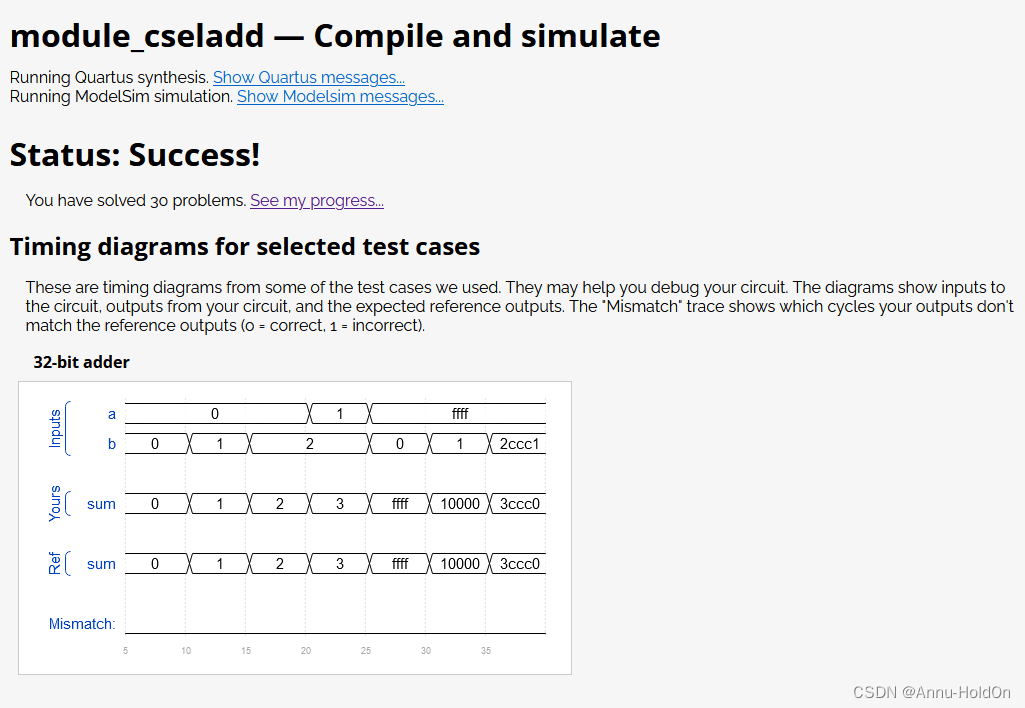

Generate for-loop:100_bit binary adder 2(Adder100i)

项目场景:

Create a 100-bit binary ripple-carry adder by instantiating 100 full adders. The adder adds two 100-bit numbers and a carry-in to produce a 100-bit sum and carry out. To encourage you to actually instantiate full adders, also output t…

HDL—Verilog Language—Modules:Hierarchy—Carry-select adder

这个部分就开始考虑到加速的一些东西了

之前几个写的不论是1位加法器还是16位的加法器,实际上都是1位的,可以观察到,如果前面cout没有给出进位的数据,后面是没法开始运算的,所以前面的加法器就会很慢,延迟…

Verilog专题(八)有符号的加法器signed adder设计

前言 对于verilog的学习,这里推荐一个比较好的实践网站HDLBits:https://hdlbits.01xz.net/wiki/Main_Page 本系列记录一些我觉得有价值的题目,希望通过这些题目可以对verilog更加熟练。 有符号的加法器signed adder设计 题目: 假设…

HDLBits 刷题笔记28:Adder-subtractor (Module addsub)

题目描述:https://hdlbits.01xz.net/wiki/Module_addsub An adder-subtractor can be built from an adder by optionally negating one of the inputs, which is equivalent to inverting the input then adding 1. The net result is a circuit that can do two o…

adder-subtractor 32位加减器

a-b相当于a加上(b的补码)也就是a加上(b取反再加1) 可以运用2个16位加法器构建32位加减器 add16接口如下: module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

32位adder-su…

full adder

Question:

Come up with logic that counts number of ‘1’s in a 7 bit wide vector. You can only use combinational logic.

Answer:

Following is one of the ways to come up with such logic.

Input vector is 7 bit wide. To sum up 7 bits we need 3 bits of bina…