a-b相当于a加上(b的补码)也就是a加上(b取反再加1)

可以运用2个16位加法器构建32位加减器

add16接口如下:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

32位adder-subtractor代码:

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire cout;

wire [31:0]c;

add16 a1(a[15:0],c[15:0],sub,sum[15:0],cout);

add16 a2(a[31:16],c[31:16],cout,sum[31:16]);

assign c=b^{32{sub}};

endmodule

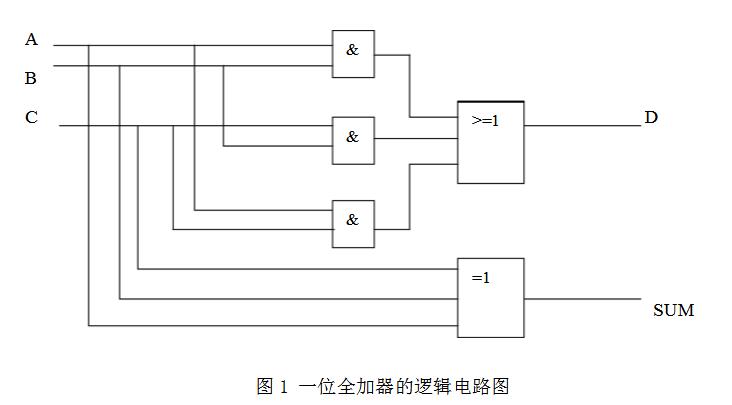

该题和该图来自HDLbits Module addsub。