我的错,人神共愤,天理难容……

简报

众所周知,74ls283是和74ls151还有74ls138一样应用广泛的电子元器件,其本体共有1+4+4+4+1+1+1=16根引脚,鉴于电源和接地引脚仍旧“没有用处”,我们再次对其进行忽略。下面笔者将利用Verilog HDL在Vavido环境下对其功能进行实现。

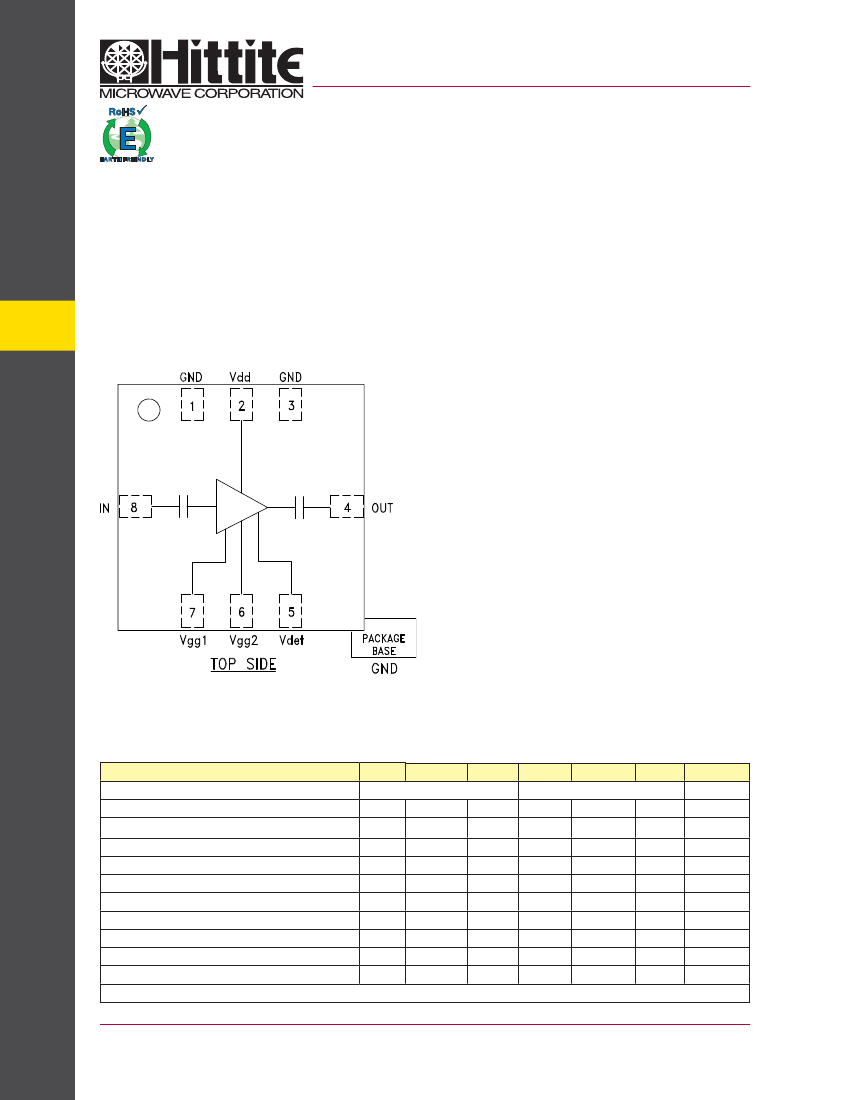

引脚

74ls283的逻辑符号共有14根引脚,其中1根为从低位进位数据输入端,4根为加数A数据输入端,4根为加数B数据输入端,4根为四位结果输出端,1根为向高位进位数据输出端。下面为详细介绍。

- 从低位进位数据输入端:共1根,是从上一个加法器或者其他的乱七八糟的什么东西引入的一个,对加数进行某些处理的数据的入口。总之只有一个口,顶多给得到的结果的低位加上一个1(毕竟数字信号只有1和0,他想加个2端口也不够…)

- 加数A数据输入端:共4根,具体功能同字面意思[doge]

- 加数B数据输入端:同上[doge]

- 结果输出端:共4根,具体功能同字面意思。注意:由于结果输出端一共4根,所以 4位数A + 4位数B 得到的结果中,五位数的最高位(第五位)无法作为结果输出,而是被转移至向高位进位数据输出端。

- 向高位进位数据输出端:共1根,是从这个加法器向下一个加法器或者其他的乱七八糟的什么东西传输进位数据的端口。

代码

说实话,笔者在写代码时犯了几个十分严重的错误…将在小结里面进行深刻的反思…

module x74x283(input [3:0] A,input [3:0] B,input c0,output [3:0] S,output c4);assign {c4,S}={1'b0,A}+{1'b0,B}+c0;endmodule

下面为在Vivado环境下的仿真文件代码。鉴于74ls283的特殊用途,笔者选择了几个个人认为能够全面证明功能的数字进行仿真操作。可能会有缺漏,如有意见或建议,恳请不吝赐教。

module SIM;reg [3:0] A;reg [3:0] B;reg c0;wire [3:0] S;wire c4;x74x283 u1(A,B,c0,S,c4);initial beginA=4'b0;B=4'b0;c0=0;#100;A=4'b1010; B=4'b0101; c0=0;#100;A=4'b1010; B=4'b0101; c0=1; #100;A=4'b1011; B=4'b0101; c0=0;#100;A=4'b1011; B=4'b0101; c0=1;#100;A=4'b1011; B=4'b1101; c0=0; end

endmodule

加法器…仿真文件真的没什么好说的…

仿真效果

根据波形图,我们可以发现代码可以实现两个四位二进制数字与来自低位的进位相加,并正确产生结果和对高位的进位,即可实现74ls283功能,符合预期。

小结

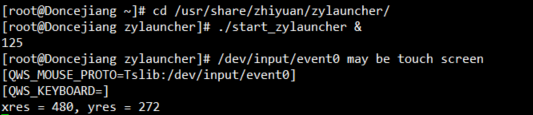

说出来各位观众老爷们可能不信,笔者写这段代码写了一个多小时…不是因为它难,也不是因为笔者一边写一边和女朋友聊天(笔者也没有女朋友…)而是因为今天脑子突然抽了一根大筋,先是受到进位影响用循环语句给他一位一位地进行加法运算,导致代码冗长(如图1),后面又在写仿真文件进行端口连接的时候顺序出错(如图二),之后的时间全浪费在找出这个问题上面了…真的是人神共愤,天理难容…各位看官一定要引以为戒…

图一

图二