目录

- 一、逻辑代数运算符号

- 与、或、非

- 与非、或非、与或非

- 异或、同或

- 二、门电路

- MOS管的结构

- MOS管的四种类型

- CMOS反相器

- 用 MOS 管搭出二输入与非门、或非门

- OD门

- CMOS传输门

- 三态输出的CMOS门电路

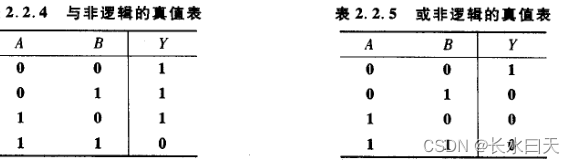

数电的基础知识隔时间太久全忘光了,前几天面试被问麻了,回过头来再看一下。

一、逻辑代数运算符号

(数字电子技术基础P21)

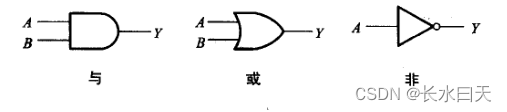

与、或、非

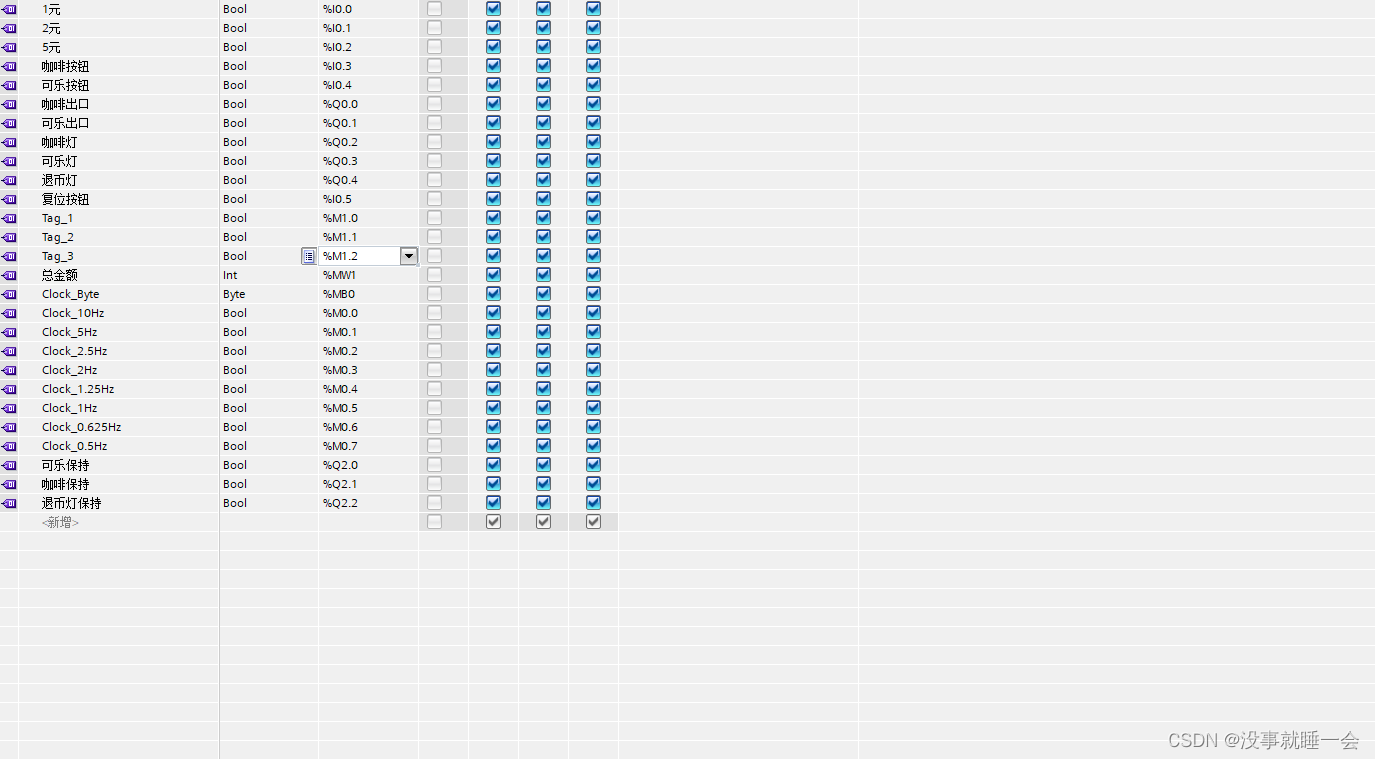

真值表如下:

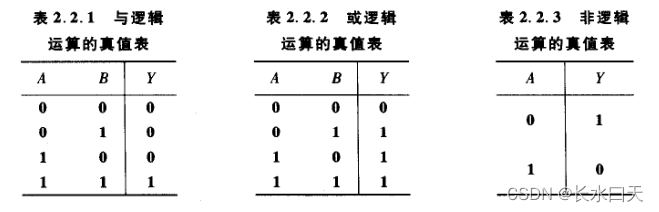

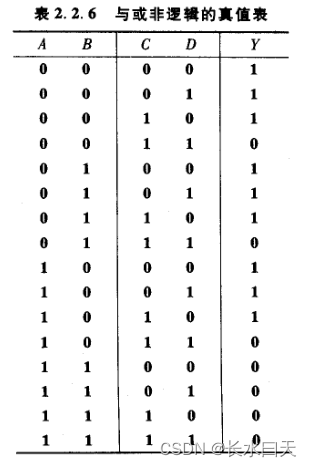

与非、或非、与或非

真值表如下:

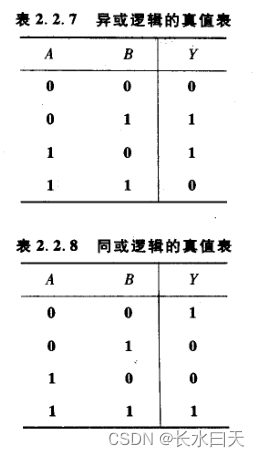

异或、同或

异或逻辑与同或逻辑的真值表如下:

二、门电路

(数字电子技术基础第三章)

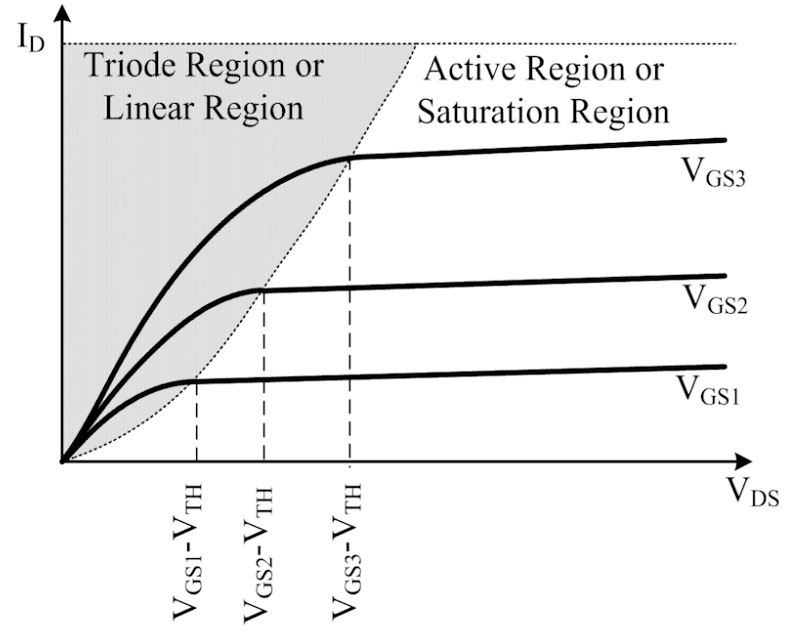

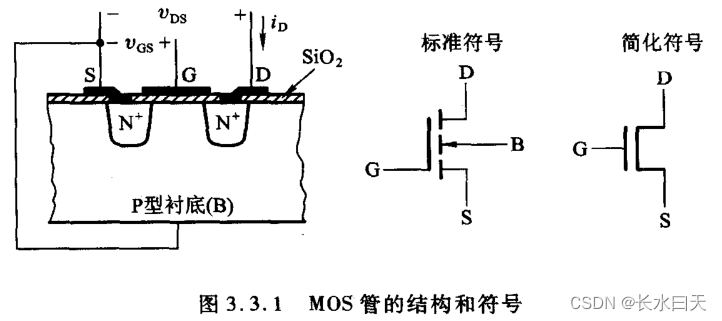

MOS管的结构

如图所示是MOS管的结构示意图和符号,在P型半导体衬底上制作两个高掺杂浓度的N型区,形成MOS管的源极S和漏极D。第三个电极称为栅极G,通常用金属铝或多晶硅制作。栅极和衬底之间被二氧化硅绝缘层隔开。

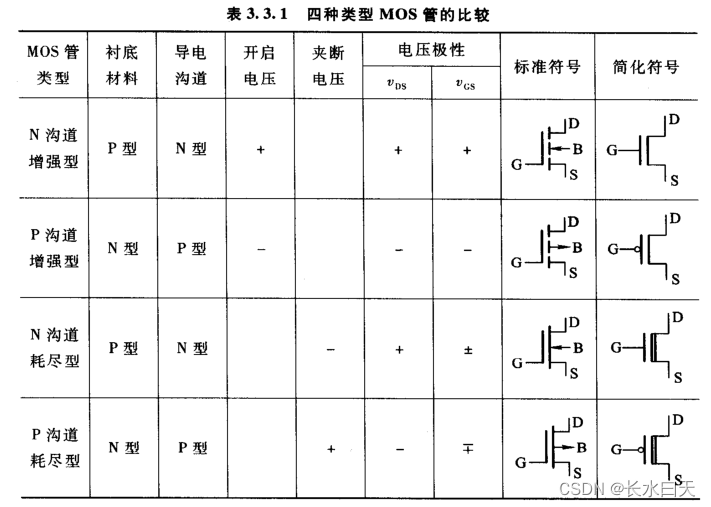

MOS管的四种类型

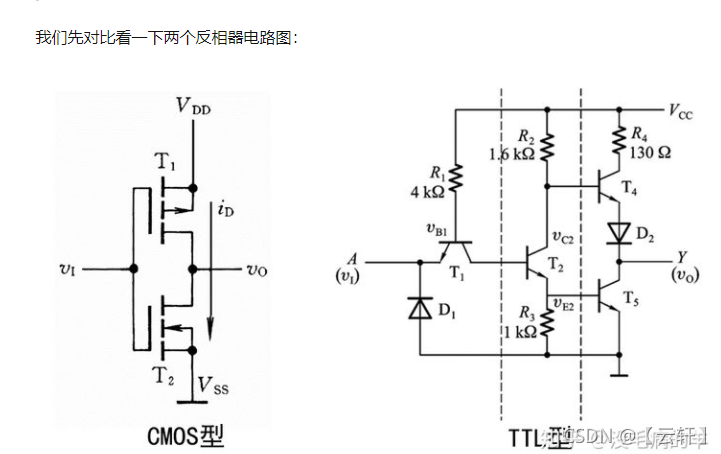

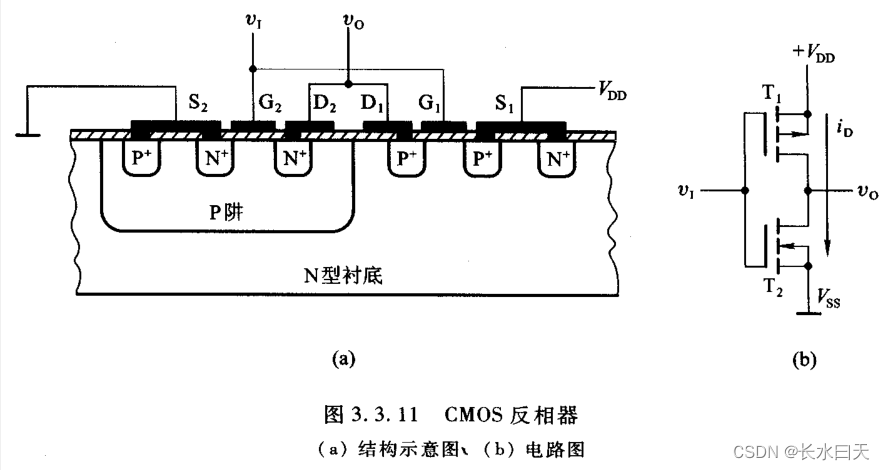

CMOS反相器

CMOS反相器的电路结构与电路图如下所示,其中T1是P沟道增强型MOS管,T2是N沟道增强型MOS管。

特点:

- 无论输出高、低电平,均有一管导通。

- T1、T2必有一个截止,功耗低。

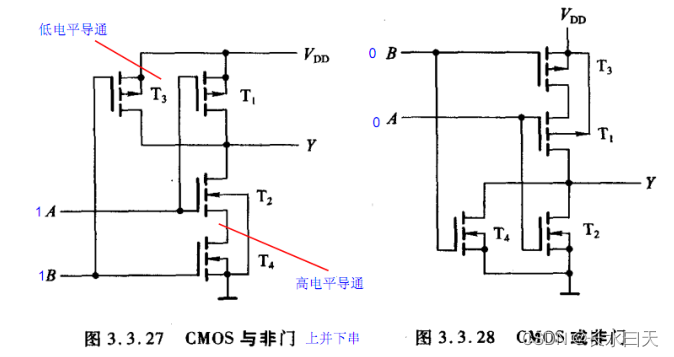

用 MOS 管搭出二输入与非门、或非门

与非门:上面两个 PMOS 并联,下面两个 NMOS 串联。

或非门:上面两个 PMOS 串联,下面两个 NMOS 并联。

(与非门:上并下串 或非门:上串下并)

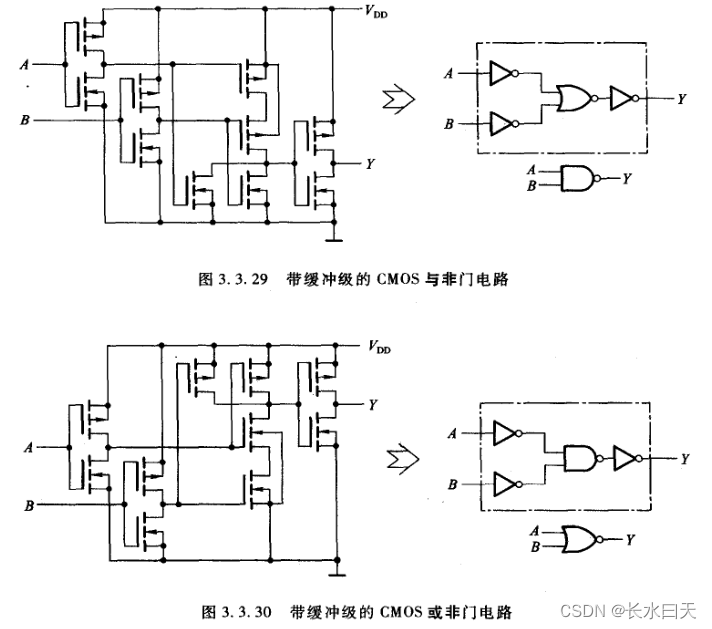

在CMOS电路中可以增加缓冲级,即在门电路的每个输入端、输出端各增设一级反相器。

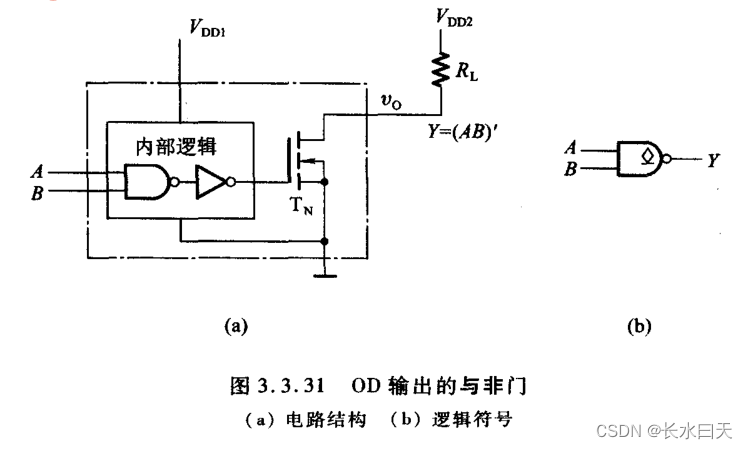

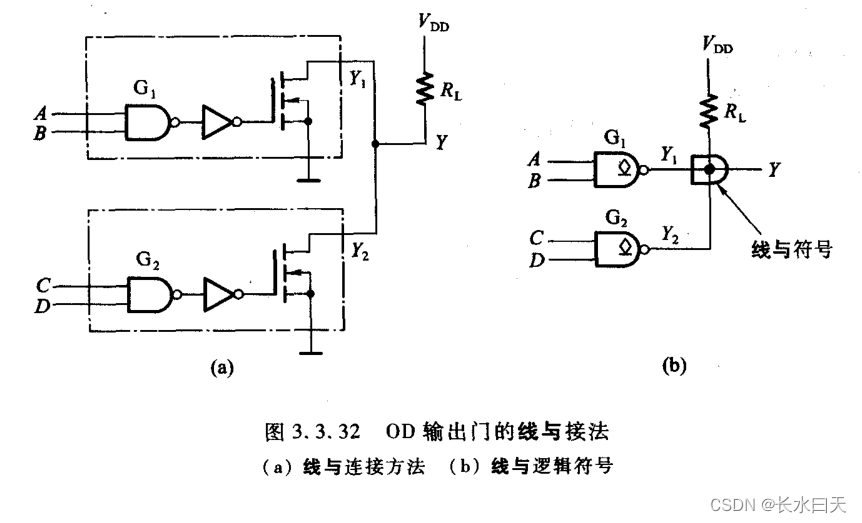

OD门

在CMOS电路中,为了满足输出电平变换、吸收大负载电流以及实现线与连接等需要,有时将输出级电路结构改为一个漏级开路输出的MOS管,构成漏级开路输出门电路,简称OD门。

- OD门工作时必须将输出端经上拉电阻RL接到电源上。

- 将几个OD门的输出端直接相连,可以实现线与逻辑。比如下图中的例子,用两个OD输出与非门接成线与逻辑,从而形成一个与或非电路。

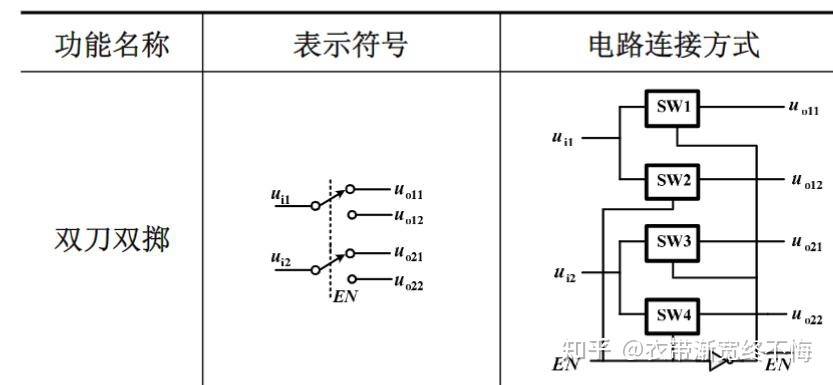

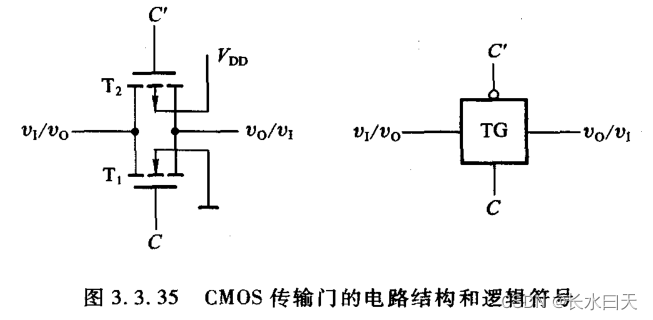

CMOS传输门

利用P沟道MOS管和N沟道MOS管的互补性可以接成如下图所示的CMOS传输门。

T1是N沟道增强型MOS管,T2是P沟道增强型MOS管。因为T1和T2的源级和栅极在结构上是完全对称的,所以栅极的引出端画在栅极的中间。T1和T2的源极和漏级分别相连作为传输门的输入端和输出端。

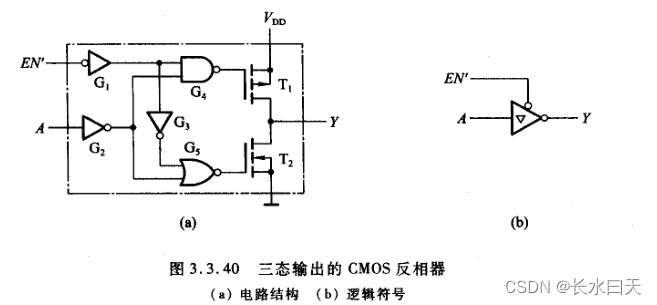

三态输出的CMOS门电路

三态输出门电路的输出除了有高、低电平这两个状态以外,还有第三个状态——高阻态。下图是三态输出反相器的电路结构图。因为这种电路结构总是接在集成电路的输出端,所以也将这种电路称为输出缓冲器。

EN’为三态控制端。EN’=1时,不管A的状态如何,G4输出高电平而G5输出低电平,T1和T2同时截止,输出呈现高阻态。