点击蓝字

关注我们

5G的快速普及使得网络吞吐量快速增长,电脑技术的不断更新迭代也让网络攻击变得越来越频繁。为了应对业界对网络带宽和网络安全越来越高的要求,英特尔®在最新的第三代Xeon® Scalable 处理器中加入Intel® Advanced Vector Extensions 512 (Intel® AVX-512) 指令集,以此来获得单系统1Tbps的IPsec加密处理能力。

本文将逐步展示如何使用第三代Xeon® Scalable 处理器和Fd.io VPP开源网络协议栈软件来达到1Tbps的IPsec加解密吞吐量,希望对用户改进其IPsec应用吞吐能力有所帮助。

总览

本文有意作为用户复现1 Terabit/sec IPsec AES-GCM-128隧道加解密的零丢包(丢包率<0.0001%)吞吐量测试的参照文档,将逐步介绍各软件和硬件配置步骤。

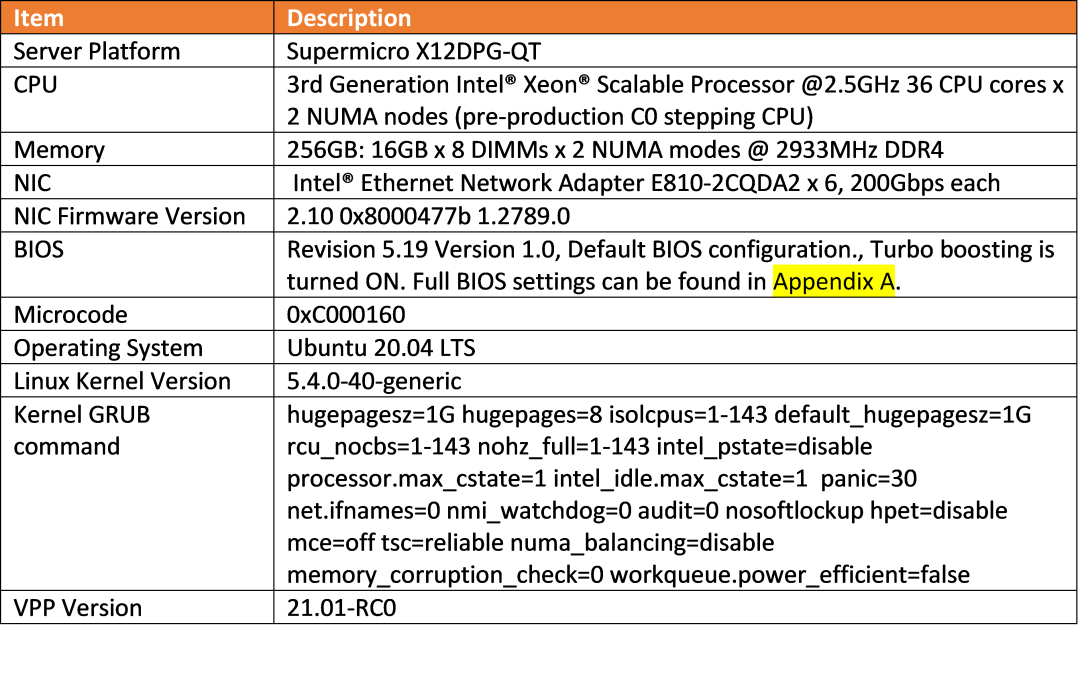

在测试中我们使用2台DUT,每台上装有Supermicro的X12DPG-QT双Numa node主板,每Numa node上载有

第三代Intel® Xeon® Scalable 处理器一枚,并将其频率恒定在2.5GHz;

8条16GB的DDR4内存,频率为2933MHz。

3块Intel® E810-2CQDA2 以太网卡,每个网卡载有2个100Gbps 网口。

软件上我们均采用开源Ubuntu Linux 20.04LTS 和Fd.io VPP 21.01。Fd.io VPP具有完整且高性能的IPsec数据面功能,并能自动使能AVX512指令集来加速AES对称密码运算。

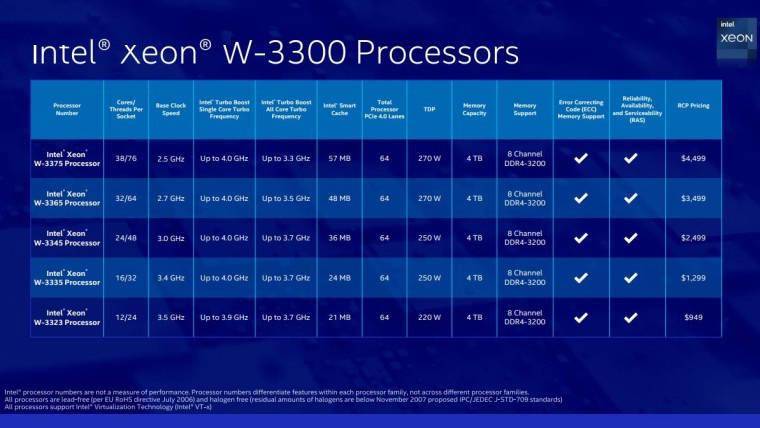

具体系统配置如下

系统配置[1]

技术背景

第三代Intel® Xeon® Scalable 处理器

最新的第三代Intel® Xeon® Scalable 处理器集成了多项技术来增强网络流加密的性能:

VPMADD2 – 向量乘法和加法指令

vAES – 向量Intel® AES-NI 指令

vCLMULQDQ – 向量 carry-less 乘法指令

SHA-NI – 新SHA指令

更详细的关于第三代Generation Intel® Xeon® Scalable 处理器的介绍请移步:

New Intel® AVX-512 instruction set support for accelerated processing of vectorized instructions

https://www.intel.com/content/www/us/en/architecture-and-technology/avx-512-overview.html

New Intel® Speed Select Technology (SST) power management technologies for increased power-aware performance

https://www.intel.com/content/www/us/en/architecture-and-technology/speed-select-technology-article.html

Intel® AVX-512 – Packet Processing with Intel® AVX-512 Instruction Set Solution Brief

https://networkbuilders.intel.com/solutionslibrary/intel-avx-512-packet-processing-with-intel-avx-512-instruction-setsolution-brief

Intel® AVX-512 – Instruction Set for Packet Processing Technology Guide

https://networkbuilders.intel.com/solutionslibrary/intel-avx-512-instruction-set-for-packet-processing-technology-guide

Intel® AVX-512 – Writing Packet Processing Software with Intel® AVX-512 Instruction Set Technology Guide

https://networkbuilders.intel.com/solutionslibrary/intel-avx-512-writing-packet-processing-software-with-intel-avx-512-instruction-set-technology-guide

Intel® Ethernet 810 系列网卡

Intel® Ethernet E810-2CQDA2 PCIe 4.0 网卡是转为优化网络工作流处理而生的双口100Gbps网卡。Intel® Ethernet 810 系列网卡的功能如下

智能Flow Direction: Receiver Side Scaling (RSS)

支持详尽的网络虚拟化协议

支持vSwitch

QoS: (802.1Qbb)

增强传输选择(802.1Qaz)

Differentiated Services Code Point (DSCP)

Dynamic Device Personalization (DDP)

关于更详细的Intel® Ethernet 810 系列网卡请移步

Ethernet Products:

https://ark.intel.com/content/www/us/en/ark/products/series/184846/intel-ethernet-networkadapter-e810-series.html

Intel® Ethernet Controller 800 Series – Dynamic Device Personalization (DDP) for Telecommunications Workloads Technology Guide:

https://networkbuilders.intel.com/solutionslibrary/intel-ethernet-controller-800-series-devicepersonalization-ddp-for-telecommunications-workloads-technology-guide

Intel® Ethernet Controller 700/800 Series – Dynamic Device Personalization Support for CNF with Kubernetes Technology Guide:

https://networkbuilders.intel.com/solutionslibrary/intel-ethernet-controller-700-series-dynamic-devicepersonalization-support-for-cnf-with-kubernetes-technology-guide

Intel® Multi-Buffer Crypto for IPsec Library

Intel® Multi-Buffer Crypto for IPsec Library是针对英特尔平台特殊优化的堆成加密算法库。通过一系列易用且详尽的API,用户的加密应用可自动根据系统平台获得最高的性能。同时,通过第三代Intel® Xeon® Scalable 处理器所提供的AVX512指令集优化,可获得最大4倍于上代CPU的加解密吞吐量。

更多关于Intel® Multi-Buffer Crypto for IPsec Library的介绍请移步

https://www.intel.com/content/dam/www/public/us/en/documents/white-papers/fast-multi-buffer-ipsecimplementations-ia-processors-paper.pdf

https://newsroom.intel.com/articles/crypto-acceleration-enabling-path-future-computing/#gs.n6t02b

https://github.com/intel/intel-ipsec-mb

测试系统部署

我们使用了12个100Gbps的IXIA® Packet Generator网口和两台DUT相连。每3个IXIA® 网口连接一个DUT的Numa Node上的3个网口。每个Numa Node上的剩余3个网口则和另一个DUT上的同Numa Node上的3个网口相连。每个网口配有5个RX Queue,由5个CPU Core来进行收包操作。因此,每Numa Node上我们总共使用了30个CPU核心。具体配置如下图

IXIA® 流配置

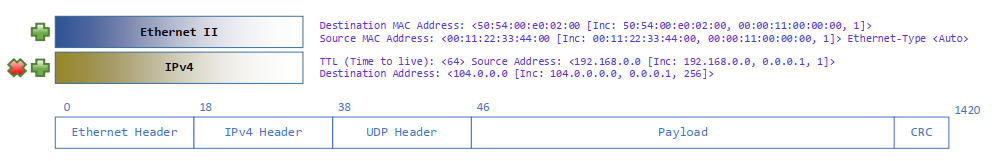

12个IXIA®口均向外发送明文IPv4包。每个IXIA®口均会发送与其他口独立的256条流。每条流长度1420字节,占宽等量,并具备独立的目的MAC及IP地址。通过Intel® E810的RSS功能,每个CPU核心将被分配到51.2条流。流配置范例如下图

VPP 配置

我们在每一个DUT上运行两个VPP进程,并在其上执行包接收,IPSEC加密或解密,及包发送指令。VPP上的startup.conf配置如下

cpu { main-core 0 corelist-workers 1-30 } dpdk { socket-mem 2048 no-tx-checksum-offload dev default{ num-tx-desc 512 num-rx-desc 512 } # Intel® E810 端口配置,应配置6个端口,此处仅显示 DUT0 socket 0的一个端口,其他省略 dev 0000:17:00.0 { workers 0,1,2,3,4 } no-multi-seg } memory { main-heap-size 2G } statseg { size 1G } |

VPP上的CLI命令如下

# 配置网卡端口,应配置6个,此处省略5个 set interface state HundredGigabitEthernet17/0/0 up set interface mtu 2024 HundredGigabitEthernet17/0/0 set interface mac address HundredGigabitEthernet17/0/0 00:22:33:44:55:0 set interface ip address HundredGigabitEthernet17/0/0 255.0.0.128/8 set int promiscuous on HundredGigabitEthernet17/0/0

# 创建一个软件隧道接口,以及2个IPSEC SA,此处应配置 6 * 256 = 1536个,省略1535个。 create ipsec tunnel local-ip 255.0.0.128 remote-ip 255.0.0.129 local-spi 255128 remote-spi 255129 local-crypto-key 2b7e151628aed2a6abf7158809cf4f3d remote-crypto-key 2b7e151628aed2a6abf7158809cf4f3d crypto-alg aes-gcm-128 integ-alg none salt 0x12345678 # 创建路由规则,将拥有 “104.0.0.0”目的IP地址的包路由到港创建的软件接口。 ip route add 104.0.0.0/32 via ipip0 set int state ipip0 up # 让软件接口共享硬件接口的IP地址 set int unnum ipip0 use HundredGigabitEthernet17/0/0 # 为加密的包创建一个新的ARP表项 set ip neighbor HundredGigabitEthernet17/0/0 255.0.0.129 3d:3f:12:11:00:11 # 配置解密后明文包的路由规则,目的地址“204.0.0.0”的包均路由去网卡端口 ip route add 204.0.0.0/32 via HundredGigabitEthernet18/0/0 255.0.1.129 3d:3f:12:11:00:aa |

测试结果

在测试环境配置完成并运行后,我们确认所有接收到的网络包都被两个DUT分别进行过IPSEC协议加密及解密,然后开始使用RFC 2544 零丢包测试方案对其进行速率测试。下图是IXIA® Networks应用测试结果的截图。

如图可见,系统总速率达到244.252Mpps或2.040Tbps。每个DUT分别达到了1.020Tbps的加密和解密速率。其中每个CPU核心完成2.544Mpps或21.081Gbps的加解密工作。

[1]: 设备和工作流配置请参看

www.Intel.com/PerformanceIndex. 测试结果因测试环境变化可能有所差异

[2]: 本文翻译自

https://networkbuilders.intel.com/solutionslibrary/3rd-generation-intel-xeon-scalable-processor-achieving-1-tbps-ipsec-with-intel-advanced-vector-extensions-512-technology-guide

原文作者:

Fan Zhang

Georgii Tkachuk

Aibhne Breathnach

Declan Doherty

Tomasz Kanteck

video分享

转载须知

DPDK与SPDK开源社区公众号文章转载声明

推荐阅读

同步异步你说了算:VPP 的异步Crypto框架

点击“阅读原文”试试吧