- 问题描述

9361-16i RAID卡在CBB侧两个PCIE SLOT识别不到,但在主板侧的PCIE X16 SLOT可以识别 。

- 排查过程

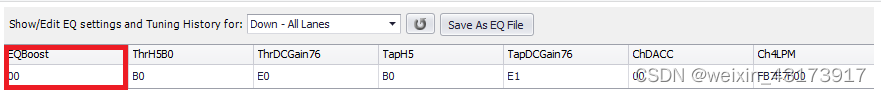

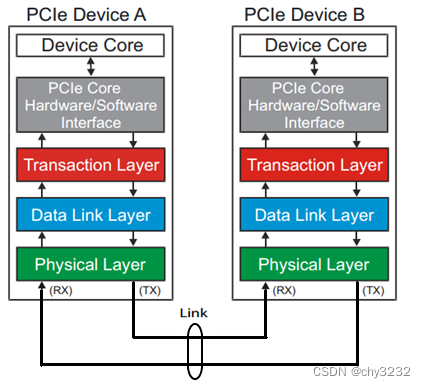

由于在主板侧可以识别,发现他们的不同之处在于100MHz时钟来源不同,主板侧直接从PCH引出,而CBB侧是通过一个clock buffer引出。联想到之前遇到过因为100MHz时钟类型不匹配导致PCIE不能link的问题,所以怀疑是这个100MHz时钟信号质量存在问题。

测量CBB侧和主板侧100MHz时钟信号,对比发现主板侧波形幅度在1V左右,CBB侧波形幅度在700mV左右,怀疑是因为时钟幅度达不到要求,于是尝试对clock buffer输出的信号增加上下拉调节其幅度,调整clock buffer的输出模式,以及直接把PCH输出的时钟引到卡上等方式,均不能解决问题。

经过上述过程,感觉可能跟时钟没有关系,于是想分析一下PCIE当前处于哪个状态,根据PCIE状态机运行过程,第一步应该是detect状态,使用单端探头测量PCIE信号发现存在周期性脉冲,说明此时处于detect状态,说明PCIE确实没有link,初始化未完成。

当前陷入无思路状态,后来偶然发现这张卡在主板侧和CBB侧上的指示灯状态有差异,在AC上电不开机状态下,在CBB侧卡的LED6处于常亮状态,而在主板侧卡的LED6不亮,在按下开机键后主板侧的卡LED6才会亮。说明在不开机时主板侧的卡没上电,而CBB侧的卡上有电。

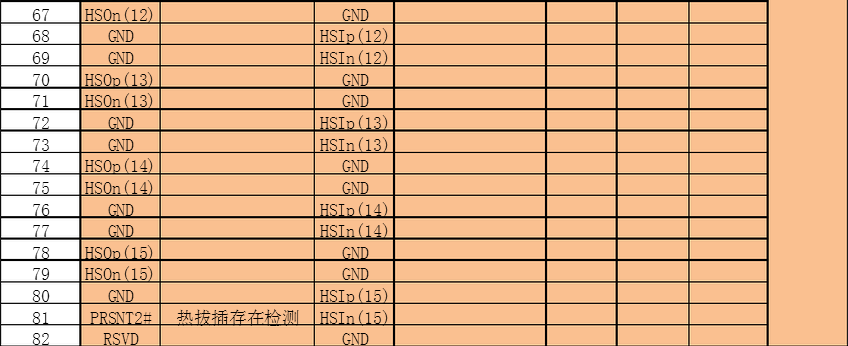

于是开始测量在不开机状态主板上SLOT和CBB上SLOT的上电区别,发现主板侧只有P3V3_AUX电,而在CBB侧有P3V3_AUX_CBB和P12V_CBB。正常状态下不开机时P12V_CBB不应该有的,实际上这个电是检测到了卡在位后就给了,而没有管有没有开机。于是修改CPLD控制这个电在监测到卡在位且开机后再给出,经过测试发现9361-16i可以识别到了。

所以该问题是卡的上电时序存在问题,但是PCIE Card SPEC上对时序要求如下,P3V3和P12V直接没有时序要求,为什么会导致9361-16i卡识别不到呢?

测量上电时序发现P12V_CBB与P3V3_AUX_CBB时序如下,P12V_CBB比P3V3_AUX_CBB先上电,这里不符合SPEC要求中P3V3_AUX先上电的要求。

- 更改方法

修改CPLD将P12V_CBB_EN信号改为在检测到卡在位且按开机后再给出。