一、pci-e接口的概念

PCI-E全称PCI-Express(peripheral component interconnect express),外部设备互连总线接口,由intel提出并推广,所连接的设备分配独享通道带宽,不共享总线带宽。

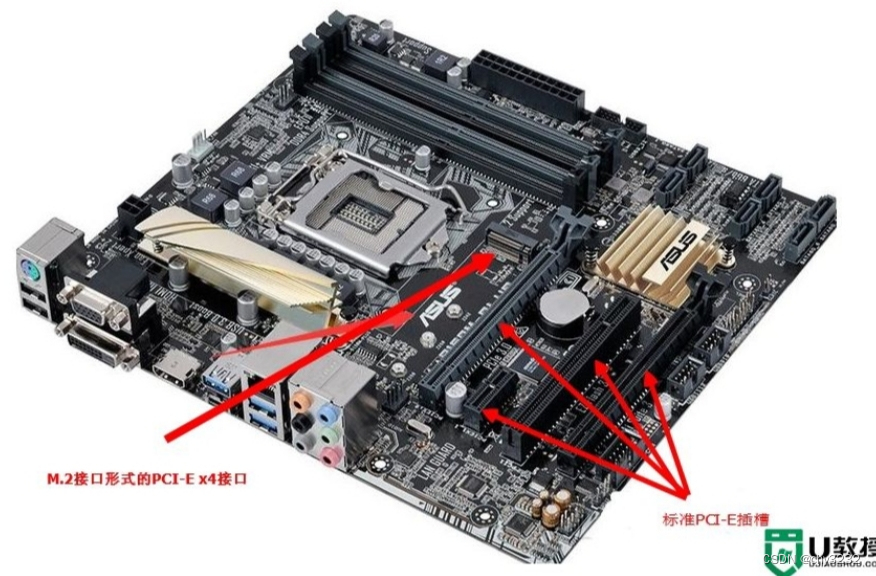

PCle有两种存在形式,M.2接口形式和PCle标准插槽。PCle可拓展性强,可以支持的设备有:显卡、固态硬盘(PCle接口形式)、无线网卡、有线网卡、声卡、视频采集卡、PCle转接M.2接口、PCle转接USB接口、PCle转接Tpye-C接口等。

二、pci-e接口的类型

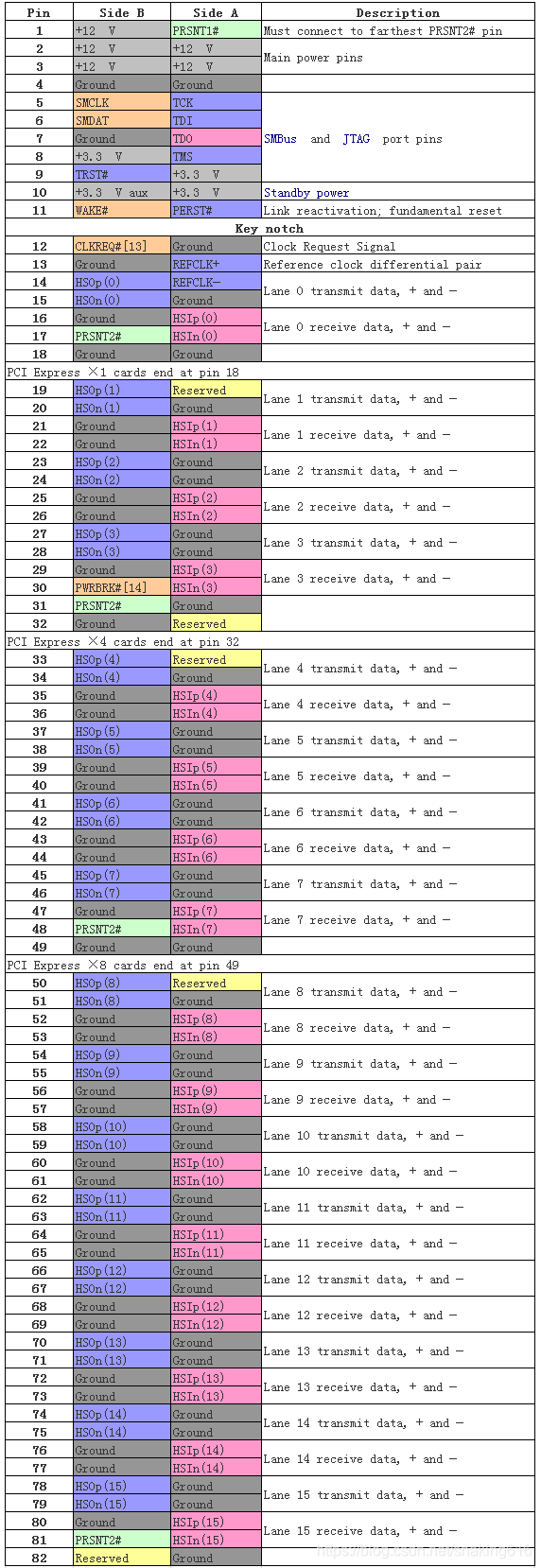

PCI-E插槽有x1,x2,x4,x8,x12,x16和×32共计7种版本,对应1/2/4/8/12/16/32通道。目前主板上主流的PCI-E插槽,基本就集中在PCI-Ex1/x4/x8/x16四种。

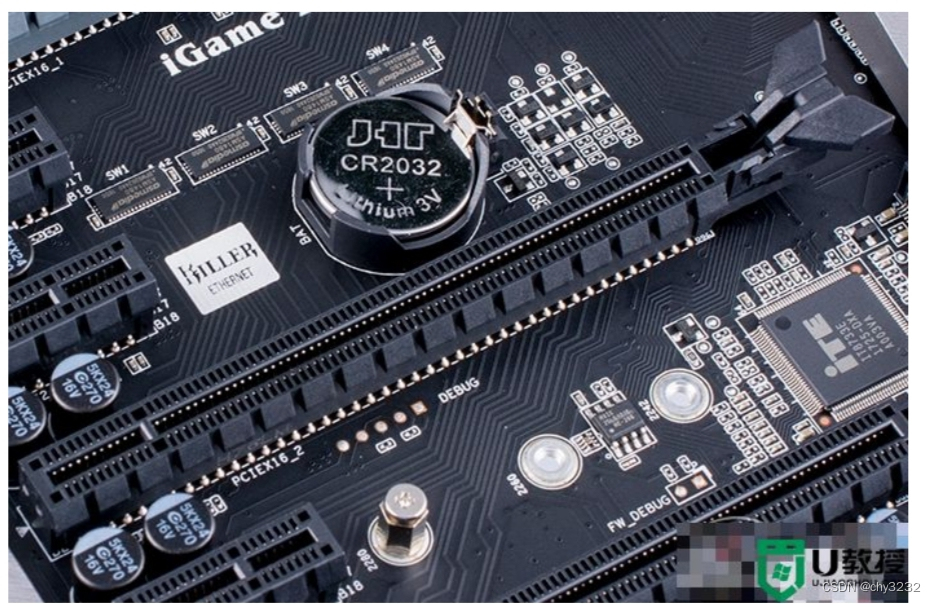

1)PCI-Ex16插槽

PCI-Ex16插槽全长89mm,常用于显卡。拥有164根针脚,分为前后两组,位于前面较短的插槽有22根针脚,主要用于供电,后面一组较长的插槽142根,主要用于数据传输。这样设计让PCI-Ex16插槽拥有了极佳的兼容性,可以向下兼容x1/x4/x8级别的设备,在加上其16通道所带来的高带宽,因此PCI-Ex16插槽可以说是PCI-E插槽在消费级领域中的完全体。

2)PCI-E x8插槽

PCI-Ex8插槽全长56mm,拥有98根针脚,相比于PCI-Ex16主要是数据针脚减少至76根,供电针脚并无变化。在主板上很少有真正的PCI-E x8插槽,它通常会以PCI-Ex16插槽的形式出现,但数据针脚只有一半是有效的,也就是说实际带宽只有真正的PCI-Ex16插槽的一半。

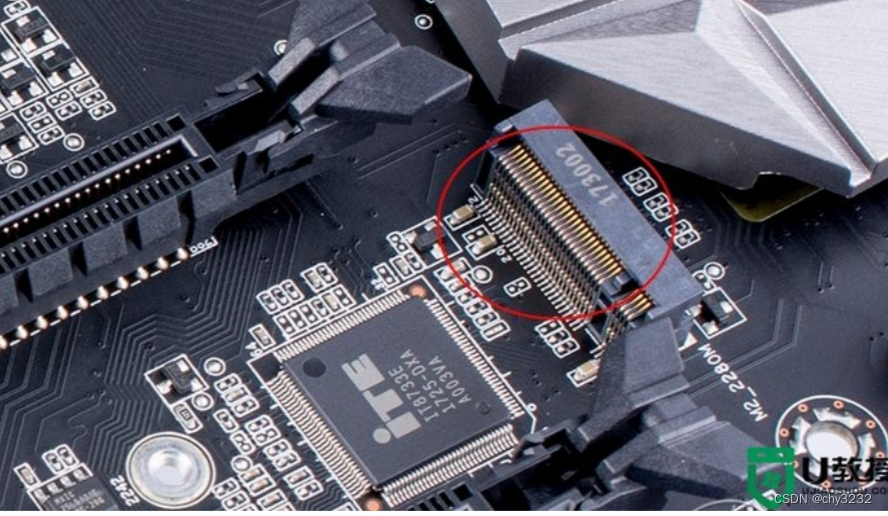

3)PCI-E x4插槽

PCI-Ex4插槽的长度为39mm,同样是在PCI-E×16插槽的基础上,以减少数据针脚的方式实现,主要用于PCI-E SSD,或者是通过PCI-E转接卡安装M.2 SSD等方面。下图是以m.2接口形式出现的PCI-Ex4插槽。

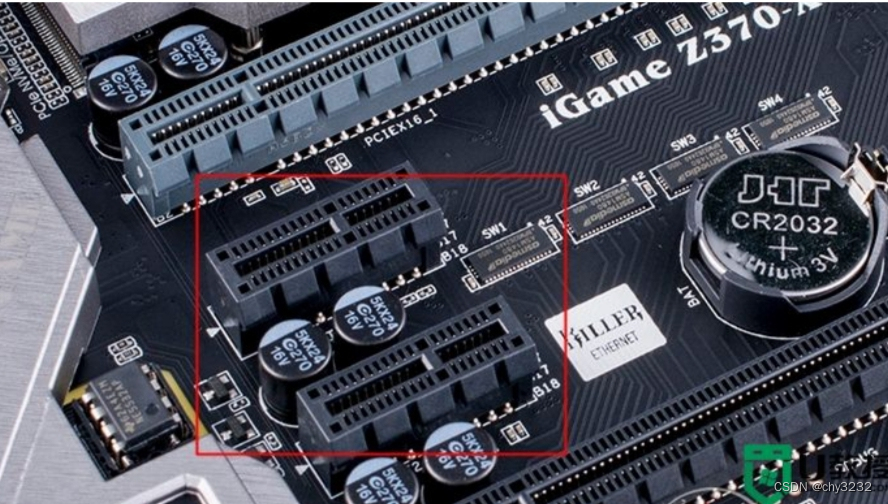

4)PCI-E x1插槽

PCI-Ex1插槽的长度是最短的,仅有25mm,相比PCI-Ex16插槽,其数据针脚是大幅度减少至14个。PCI-E x1插槽的带宽通常由主板芯片提供,面向的产品比较广泛,独立网卡、独立声卡、USB 3.0/3.1扩展卡等都会用到PCI-Ex1插槽,你甚至可以通过转接线给PCI-Ex1插槽装上显卡,用来挖矿或者实现多屏输出。

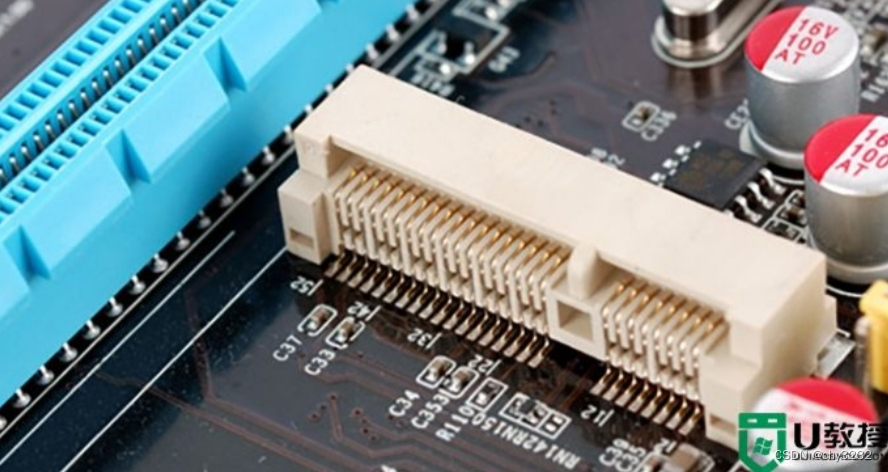

PCI-Ex1插槽还存在着另外一个形态,一般称为Mini PCI-E插槽,常见于Mini-ITX主板以及笔记本电脑上,多数用来扩展无线网卡,但由于其在物理结构上与mSATA插槽相同,因此也有不少主板会通过跳线或者BIOS设定让Mini PCI-E接口在PCI-E模式或者SATA模式中切换,以实现一口两用的效果。

三、pci-e接口的发展

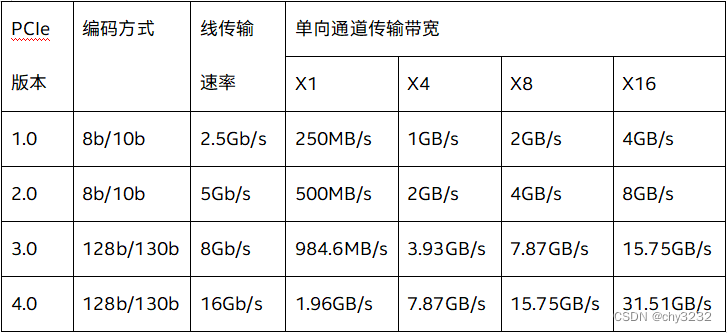

从速度上看:PCle几乎每一代翻一倍,以此来适应越来越快的处理器。

从连接上看:和在PCI总线上同时挂接多个10设备不同,PCle采用了点对点串行连接,物理上只能连接一个设备。

四、pci-e层次划分

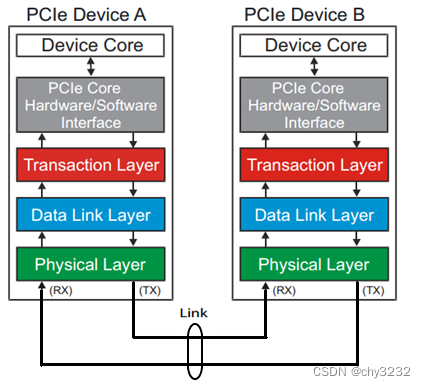

在PCle体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后再经过该设备的事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(PhysicalLayer),最终发送出去。而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达Device Core。

1)事务层

事务层定义了PCle总线使用总线事务,其中多数总线事务与PCI总线兼容。这些总线事务可以通过Switch等设备传送到其他PCle设备或者RC。RC也可以使用这些总线事务访问PCle设备。

事务层接收来自PCle设备核心层的数据,并将其封装为TLP(Transaction Layer Packet)后,发向数据链路层。此外事务层还可以从数据链路层中接收数据报文,然后转发至PCle设备的核心层。

2)数据链路层

数据链路层保证来自发送端事务层的报文可以可靠、完整地发送到接收端的数据链路层。来自事务层的报文在通过数据链路层时,将被添加Sequence Number前缀和CRC后缀。数据链路层使用ACK/NAK协议保证报文的可靠传递。

PCle总线的数据链路层还定义了多DLLP(Data Link Layer Packet),DLLP产生于数据链路层,终止于数据链路层。值得注意的是,TLP与DLLP并不相同,DLLP并不是由TLP加上Sequence Number前缀和CRC后缀组成的。

3)物理层

物理层是PCle总线的最底层,将PCle设备连接在一起。PCle总线的物理电气特性决定了PCle链路只能使用端到端的连接方式。PCle总线的物理层为PCle设备间的数据通信提供传送介质,为数据传送提供可靠的物理环境。

物理层是PCle体系结构最重要,也是最难以实现的组成部分。PCle总线的物理层定义了LTSSM(Link Training and Status State Machine)状态机,PCle链路使用该状态机管理链路状态,并进行链路训练、链路恢复和电源管理。