问题现象:

- EXXXX显卡直接插到主板上可以link up到Gen4

- 显卡+ Gen5 CI interposer卡无法link到Gen4,只能协商到Gen3

- 显卡+Gen5 CI interposer卡+Gen4延长线,可以协商到Gen4

- 如果使用15cm延长线,链路只能到Gen3

- 如果使用20cm延长线,链路能到Gen4

总结:不插interposer卡,Gen4 X16

插上interposer卡,Gen3 X16

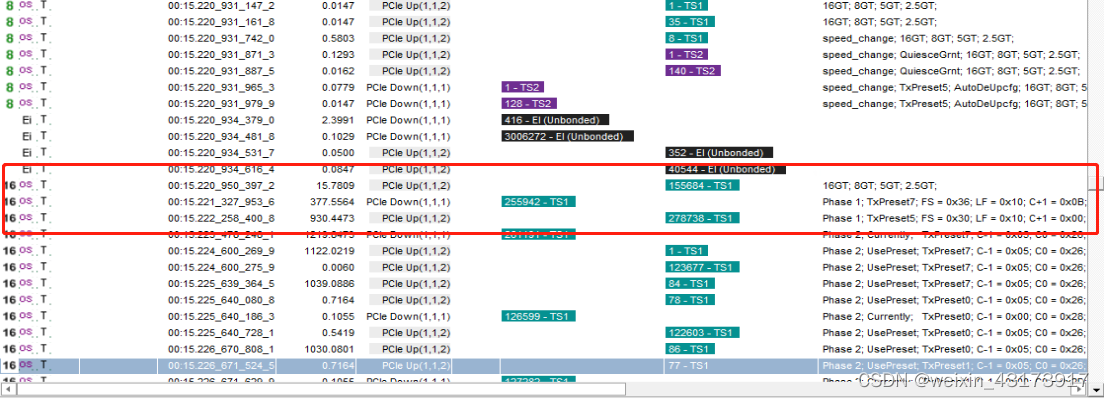

分析仪抓取数据对比:

- 正常协商过程

- 异常协商过程

Environment:

- VIAVI 11.0 /15.1.0 version

- Gen5分析仪+ CEM 5.0 CI interposer

- 主板是AMD+技嘉X570 UD

- 被测件Gen4X16

Debug处理过程:

- 延长线上面没有Redriver或者retimer芯片,延长线相当于CTLE功能,低通滤波器,同时也有损耗

- 从现象来看,Device没有收到Host发过来的Phase1 的TS1,导致超时24ms,退出了Recovery.EQ过程,按照PCIE协议,符合协议 HOST端再Phase1 超时24ms 进入EI Device端再Phase1超时12ms进入EI

3. Downstream进入了Phase1, 所以Downstream肯定是收到了upstream发过来的Phase 0的TS1,才进入了Phase 1,所以Host端是可以收到Device发过来的TS1的

The host side enters Phase 1 at 8.0 GT/s of the Recovery.Equalization state whereas DUT enters Phase 0 at 8.0 GT/s.

4. Device端在12ms之后就超时(这个超时在Host端24ms超时之前),所以device没有收到Host发过来的Phase1的TS1,最后进入EI状态

但是从分析仪是抓取到Host端发过来的Phase1的TS1,所以问题出在Interposer收到后往后的过程,同时Interposer卡和被测件有不同的ASIC能力,所以解包能力也是不同的

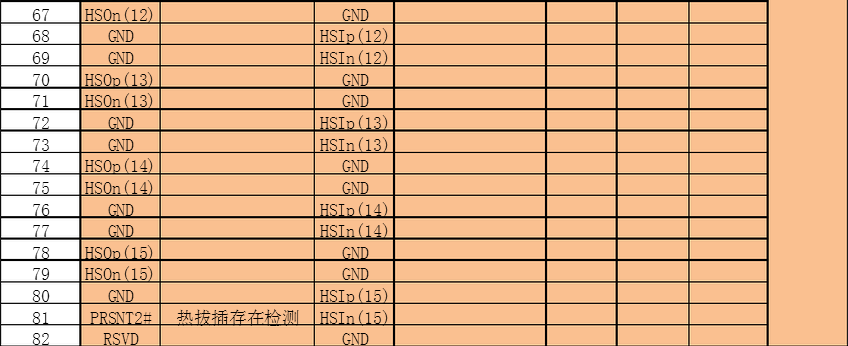

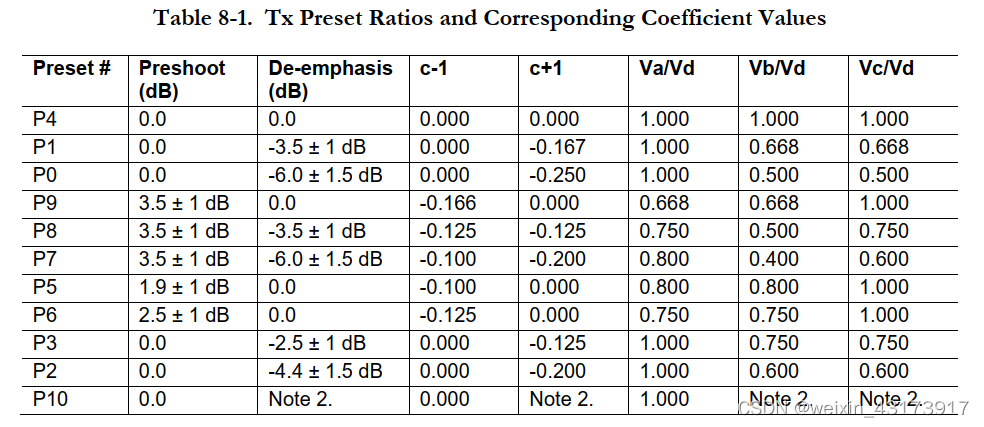

5. 从抓取的数据里面就找到,Phase 0/1 阶段Host在4.0速率默认使用Preset 7 进行数据发送

![]()

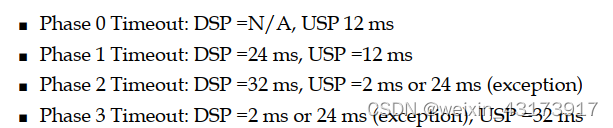

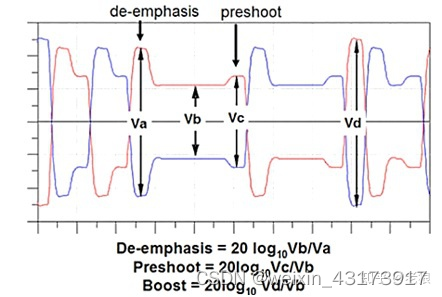

Preset 7如下图所示,Preshoot和De-emphasis是比较强的(这两个参数用于发送端)

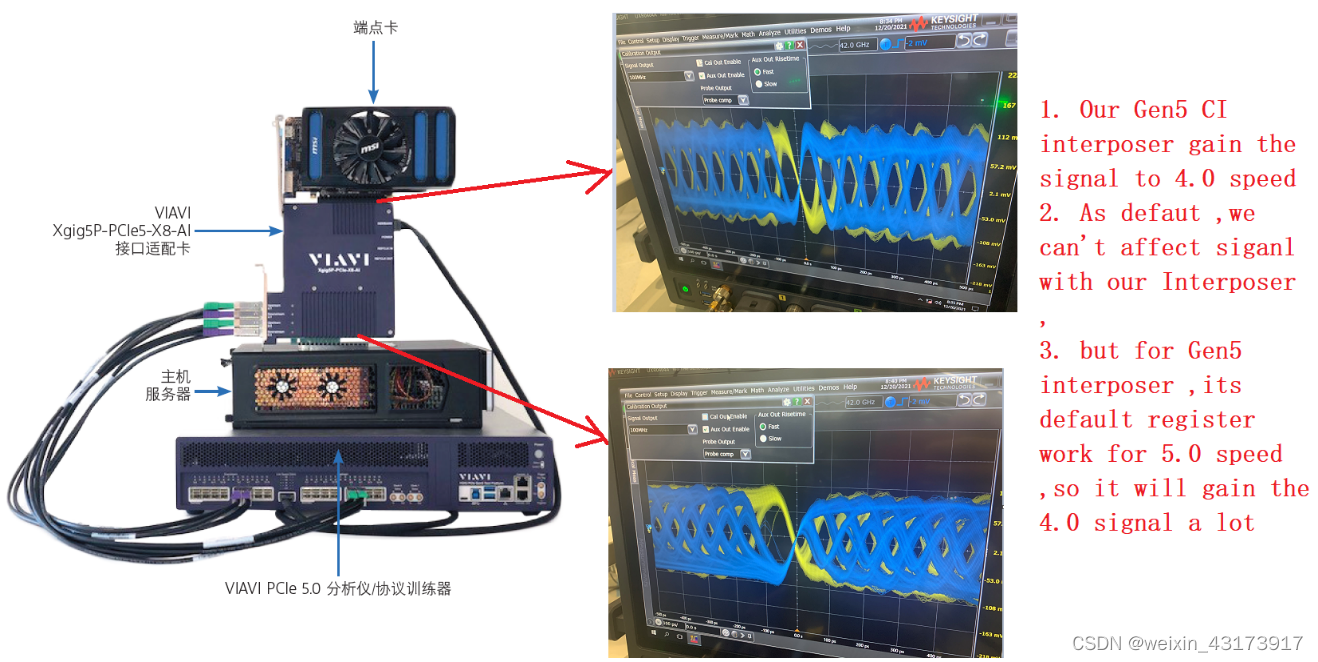

6. 在示波器和客户的帮助下,利用进入compliance Pattern测试0数据发送的波形,进行对比

1主板发出数据波形(没有经过5.0 CEM inter poser卡)

‘’

‘’

6.2 Interposer卡发出数据波形(经过5.0 CEM inter poser卡)

很明显,信号经过5.0 的Interposer卡之后,信号质量明显变好

6.3 理论上这种信号质量发送到被测件,是没有问题的,妥妥的解析

Note:大部分情况下我们说的CTLE其实是包含了放大器能力,默认CTLE只是去抑制低频来让眼图睁开没有放大能力

有一种可能,被测件也有CTLE和DFE能力(这两个是接收端调制),也就是Host发送出来的信号,经过了两次 CTLE和DFE的调制和增益,信号质量反而变差了(这个无法验证)

解决方案:

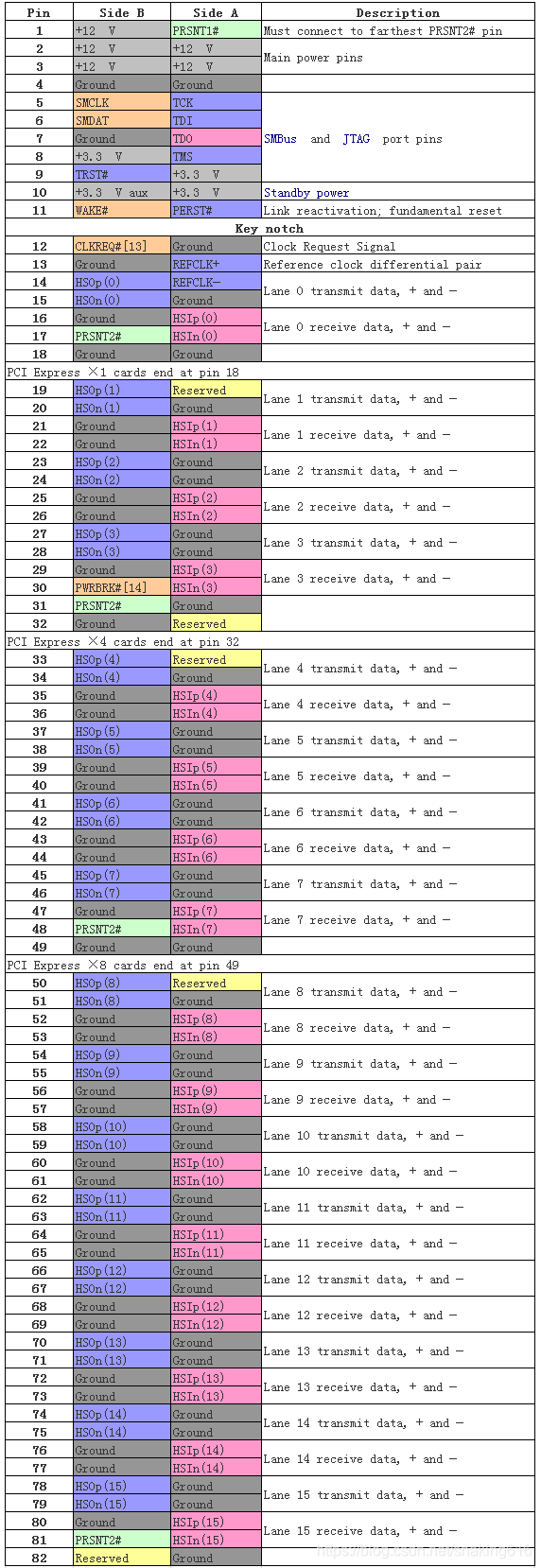

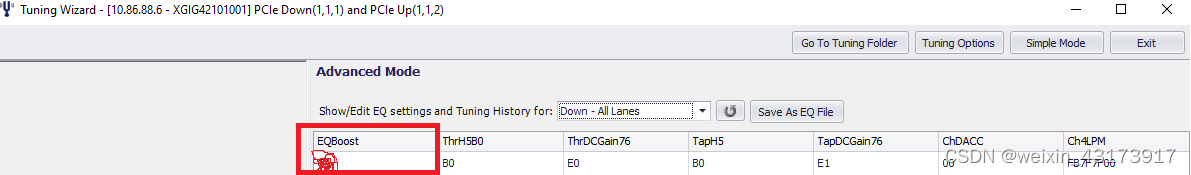

- 默认的CEM 5.0 Interposer卡的default值是给5.0 速率使用 ,EQBOOST增益(其实就是CTLE能力)会相对于4.0强,所以尝试降低Downstream端的CTLE增益强度进行调试(只有这个能调试)

- 打开Tuning Wizard,查看默认EQBOOST (downstream)(下图以4.0 interposr卡为例 ,5.0 CEM卡的downstream默认值是另外一个值)

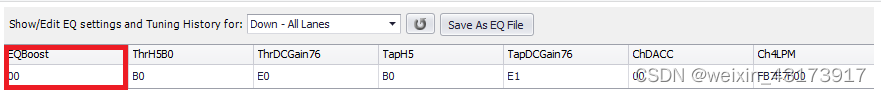

CEM 5.0的EQBoost对链路增益最明显,调试范围是 0x00-0x21 ,直接调试到0x00

- 重新cold reset 主板,直接可以链路协商到4.0,问题解决

- 保存Tuning file 配置,下次直接load使用

Summary:

- Interposer卡默认设置值,应该是不影响链路,但是因为CEM 5.0的默认值是设置为5.0 link使用,所以这个配置用于4.0的链路,会对链路信号产生增益而不是保持信号不变

- 同时测试环境也是比较特殊,

- Host发送端使用的是Preset 7, Preset7的信号调制能力是最强大的,使用Preset 4(最弱),可能也可以解决问题

- 被测设备的信号恢复能力很强

- 使用的分析仪的Interposer卡是 5.0 卡,增益比较强大

| AMD+ GIGABYTE X570UD | |

| no interposer,no pcie extended wire | link up to Gen4 |

| Gen5 chassis + Gen5 CI interposer | only link up to Gen3 |

| Gen5 chassis + Gen5 CI interposer +PCIE extended wire | link up to Gen4 |

| Gen5 chassis + Gen4 Type B interposer | link up to Gen4 |

总结来讲,基本推断是host发送到device的信号在过度增益(Interposer卡+device本身的增益)下,信号产生了问题,导致device端无法识别信号通过调低Interposer卡的增益来达到一个平衡点