我们都知道FPGA的IO被划分为多个BANK,起初我以为这么设计的目的只是为了适配FPGA与不同电平标准外设交互的需求,后来发现是我肤浅了。不同的BANK除了可以用来适配不同的电平标准,还可以用来适配不同的速率要求。比如视频流传输,随着技术的发展,视频的分辨率也是水涨船高,前些年1080P都算行业标杆,现如今不能支持4K、8K都不好意思说话。像传统的视频接口mipi、openLDI、cameraLink等,这些都是属于常规的LVDS电平标准(不需要Serdes专用接口)。

以1920x1080@60Hz为例,其像素时钟约为150Mhz(1920x1080x60x1.2,其中1.2为视频前后肩的损耗估算),并转串之后的额IO口传输频率约为1050Mbps(按照RGB888,4lane传输计算),性能与宽压范围往往是鱼与熊掌不可兼得,为了得到更高的传输性能,就必须得牺牲一定的电压输入范围,所以Xilinx将BANK分为两种(其实是3种,ultrascale器件中还有HD BANK):

HP BANK :High Performance 高性能

HR BANK : High Range 高电压范围。

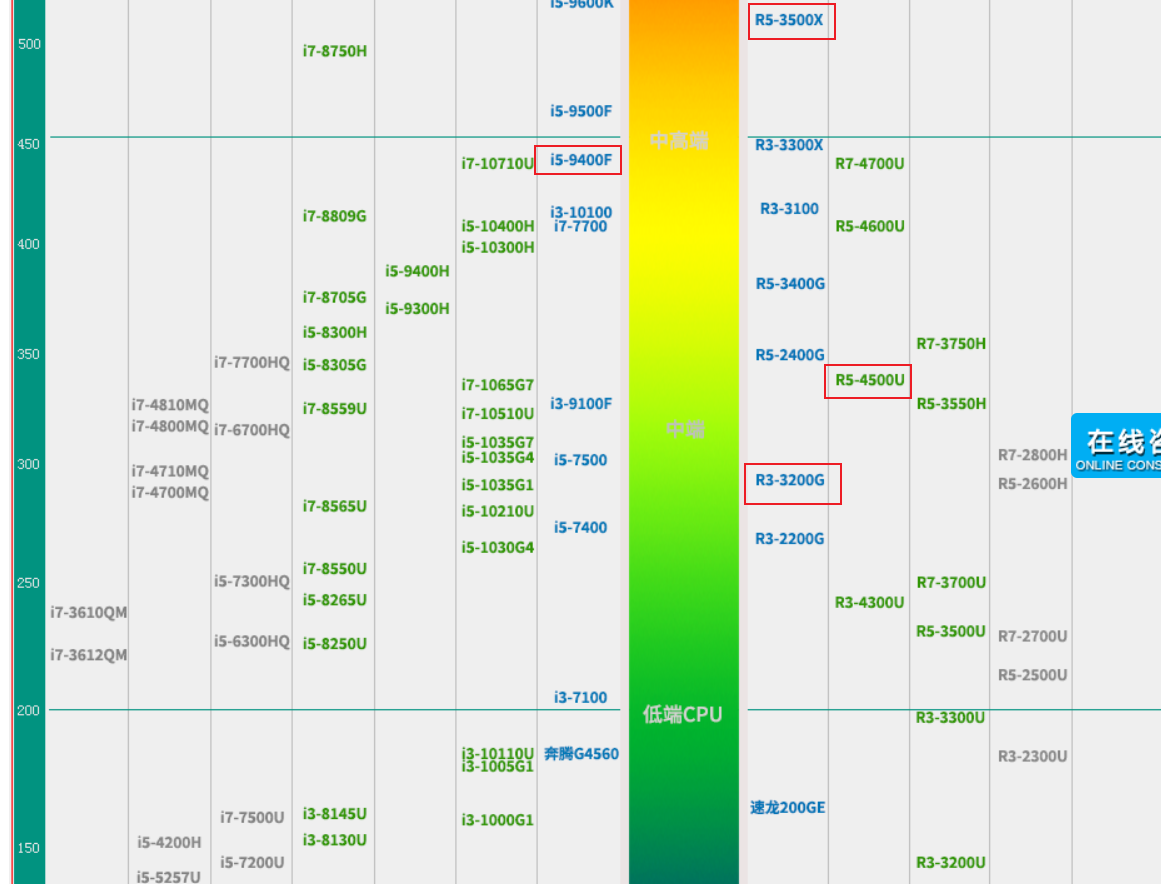

下图是7K325T器件的BANK分布图

图片来源UG471

图片来源UG471

简述HR BANK 与 HP BANK的区别

1、底层元件的支持情况

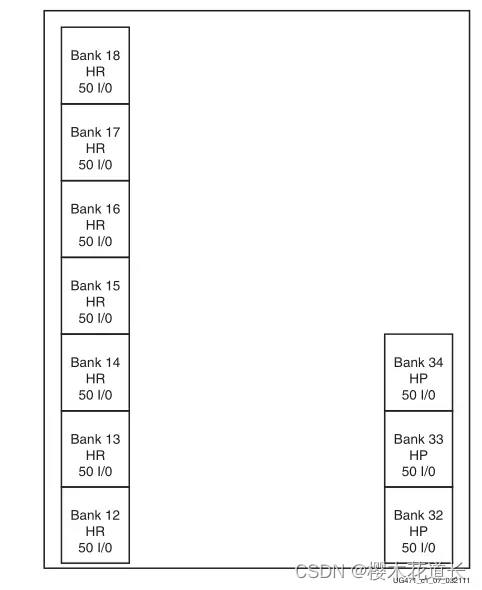

图片来源UG471

图片来源UG471

从上表我们可以发现,HR BANK不支持ODELAY,HP BANK不支持ZHOLD_DELAY;至于什么是ODELAY,什么是ZHOLD_DELAY,咱们后面讲到底层结构的时候再讲,暂不赘述。

2、支持的电平标准

图片来源UG471

图片来源UG471

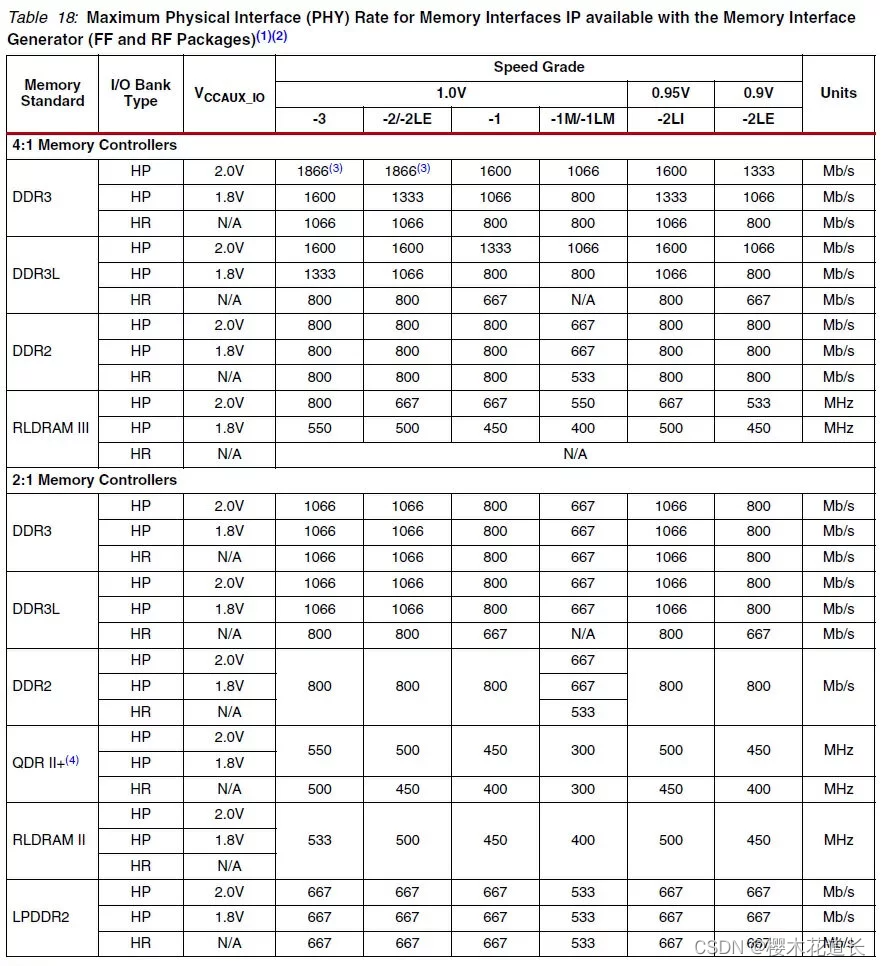

HRbank可以支持的电压范围比HP BANK更广,基本上从1.2V~3.3V的单端电压标准

都支持,但是HP BANK 支持DCI 和 Vccaux_io supply rail,这两个都是与DDR驱动相关,

如果设计中用到了DDR,建议将DDR接到HP BANK,为什么只是建议呢?因为HR BANK也

可以驱动DDR,但是性能会差很多。

DS182

DS182

另外有一点需要特别注意的是:HR BANK和HP BANK虽然都能支持LVDS信号,但是HR BANK只能支持LVDS_25,也就是共模电压2.5V;HP BANK只能支持LVDS,共模电压1.8V。 记得第一次使用HR BANK驱动LVDS时,以为HR BANK支持1.2~3.3V所有电平,对LVDS信号同样有效,给BANK电压设计成1.8V,结果是各种调试,发现问题后,各种割板飞线,我踩过的坑希望后来人就不要在踩了。

The LVDS I/O standard is only available in the HP I/O banks. It requires a V CCO to be

powered at 1.8V for outputs and for inputs when the optional internal differential

termination is implemented (DIFF_TERM = TRUE).

The LVDS_25 I/O standard is only available in the HR I/O banks. It requires a V CCO to be

powered at 2.5V for outputs and for inputs when the optional internal differential

termination is implemented (DIFF_TERM = TRUE).

图片来源UG471

图片来源UG471

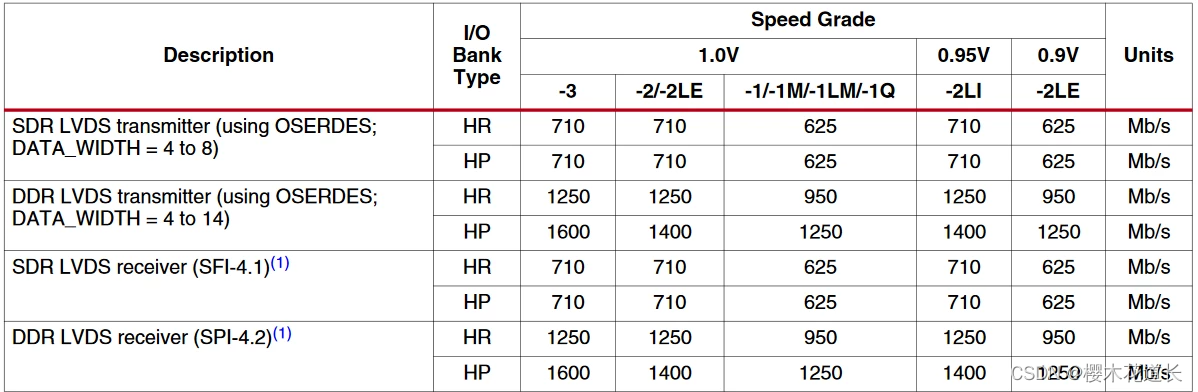

3、支持的速率

DS182

DS182

在SDR(单沿采样)模式下,HP BANK 和 HR BANK的最大速率没有区别,但是在DDR(双沿采样)模式下,HP BANK的速率相对于HR BANK有明显的提升。