verilog

2024/9/24 11:23:10详解IIC通信协议以及FPGA实现

一、IIC简介 IIC也称为I2C(Inter-Integrated Circuit)由飞利浦公司(现在的恩智浦半导体)开发,是一种用于短距离数字通信的串行,同步,半双工通信接口协议;传输在标准模式下可以达到10…

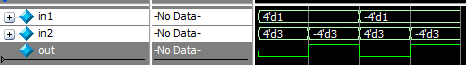

[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-26浅谈XILINX FIFO的基本使用

软件版本:VIVADO2021.1

操作系统:WIN10 64bit

硬件平台:适用 XILINX A7/K7/Z7/ZU/KU 系列 FPGA

实验平台:米联客-MLK-H3-CZ08-7100开发板

板卡获取平台:https://milianke.tmall.com/

登录“米联客”FPGA社区 http…

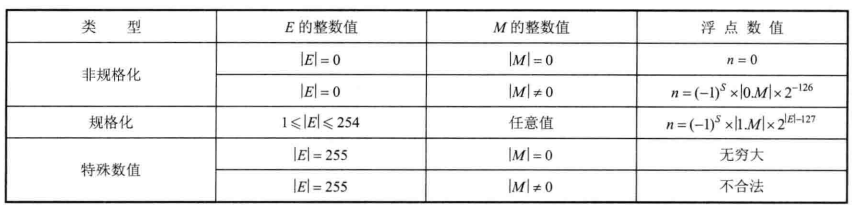

基于FPGA的数字信号处理(3)--什么是浮点数?

科学计数法

你可能不了解「浮点数」,但你一定了解「科学记数法」。

10进制科学记数法把一个数表示成a与10的n次幂相乘的形式(1≤|a|<10,a不为分数形式,n为整数),例如: 19970000000000 1.9…

[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-35 VIVADO用户IP软件总线接口封装

软件版本:VIVADO2021.1

操作系统:WIN10 64bit

硬件平台:适用 XILINX A7/K7/Z7/ZU/KU 系列 FPGA

实验平台:米联客-MLK-H3-CZ08-7100开发板

板卡获取平台:https://milianke.tmall.com/

登录“米联客”FPGA社区 http…

基于FPGA的数字信号处理(5)--Signed的本质和作用

前言

Verilog中的signed是一个很多人用不好,或者说不太愿意用的一个语法。因为不熟悉它的机制,所以经常会导致运算结果莫名奇妙地出错。其实了解了signed以后,很多时候用起来还是挺方便的。

signed的使用方法主要有两种,其中一种…

音频左右声道数据传输_2024年9月6日

如下为音频数据传输标准I2S总线的基本时序图 I2S slave将I2S master发送来的左右声道的串行数据DATA转变为16bit的并行数据 WS为左右声道选择信号,WS高代表左声道,WS低代表右声道; WS为高和为低都持续18个周期,前面16个周期用来传输数据。 I2…

米联客-FPGA程序设计Verilog语法入门篇连载-03 Verilog语法_基础语法

软件版本:无

操作系统:WIN10 64bit

硬件平台:适用所有系列FPGA

板卡获取平台:https://milianke.tmall.com/

登录“米联客”FPGA社区 http://www.uisrc.com 视频课程、答疑解惑! 1概述

本节主要讲解基础语法&#…

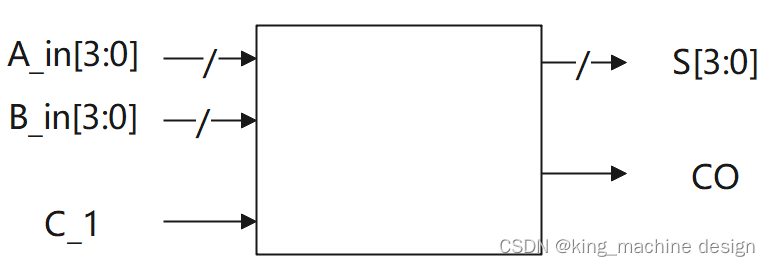

Verilog中4bit超前进位加法器

4bit超前进位加法器的逻辑表达式如下:

中间变量GiAiBi,PiAi⊕BiGiAiBi,PiAi⊕Bi

和:SiPi⊕Ci−1SiPi⊕Ci−1,进位:CiGiPiCi−1CiGiPiCi−1

用Verilog语言采用门级描述方式&am…

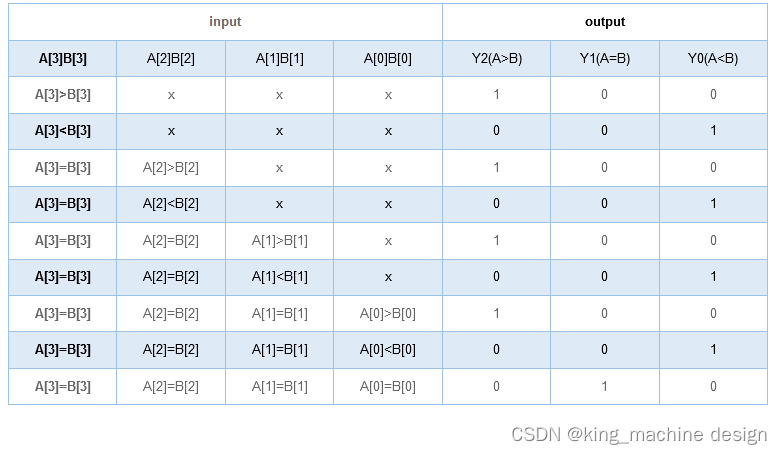

Verilog中4位数值比较器电路

某4位数值比较器的功能表如下。

请用Verilog语言采用门级描述方式,实现此4位数值比较器 参考代码如下:

(CSDN代码块不支持Verilog,代码复制到notepad编辑器中,语言选择Verilog,看得更清楚)

t…

详解IIC通信协议以及FPGA实现

一、IIC简介 IIC也称为I2C(Inter-Integrated Circuit)由飞利浦公司(现在的恩智浦半导体)开发,是一种用于短距离数字通信的串行,同步,半双工通信接口协议;传输在标准模式下可以达到10…

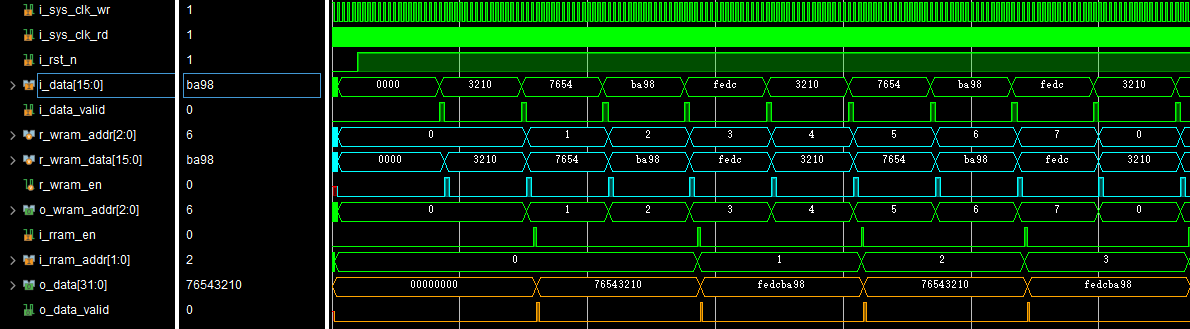

Xilinx RAM IP核的使用及注意事项

对于RAM IP核(Block Memory Generator核)的使用以及界面的配置介绍,文章RAM的使用介绍进行了较详细的说明,本文对RAM IP核使用中一些注意的地方加以说明。 文章目录 三种RAM的区别单端口RAM(Single-port RAM)简单双端口RAM(Simple Dual-port RAM)真双端…

vivado 的 ila 接AXI 总线一直报错

反复测试都是The debug hub core was not detected。

接线正确的前提下总是报错,我的时钟接的ps端的时钟线FCLK_CLK0.对jtag的频率多次调整也没效果,后来参考他人意见,重启了ps端,解决问题。

重启PS端就是将vitis软件至于DEBUG状…

Vivado综合属性SRL_STYLE怎么用?

“SRL_STYLE”属性是Vivado中用于控制移位寄存器(Shift Register Logic, SRL)映射方式的关键属性。

本文将详细介绍SRL_STYLE的工作原理、可选值及其在实际设计中的应用代码示例。

一、什么是SRL_STYLE?

SRL_STYLE属性用于指导Vivado综合工…

音频左右声道数据传输_2024年9月6日

如下为音频数据传输标准I2S总线的基本时序图 I2S slave将I2S master发送来的左右声道的串行数据DATA转变为16bit的并行数据 WS为左右声道选择信号,WS高代表左声道,WS低代表右声道; WS为高和为低都持续18个周期,前面16个周期用来传输数据。 I2…

![[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-26浅谈XILINX FIFO的基本使用](https://i-blog.csdnimg.cn/direct/3c582fd8da444ddba8e798b26e0859b8.png)

![[米联客-XILINX-H3_CZ08_7100] FPGA程序设计基础实验连载-35 VIVADO用户IP软件总线接口封装](https://i-blog.csdnimg.cn/direct/d134a9839bfb48d0bac1358819ee7f30.png)