低压差分信号具有传输速率快、抗干扰性强的特点,是现在广泛应用的数据接口标准之一。Xilinx FPGA支持LVDS电平标准,并提供了动态相位调整解决方案,解决了基于LVDS源同步传输时存在的数据偏斜问题。

1 LVDS 技术规范简介

随着接口和背板信号的数据速率需求稳步提高,基于TTL等单端信号传输的弱点越来越突出,存在传输功耗大、误码率高和电磁辐射强等缺点。增加总线宽度是提高接口和背板带宽的有效途径,但会使得线路板的布局难度加大,且引脚增加会导致连接器数量增加,致使系统成本上升。为保证接口和背板传输具有低功耗、低误码率、低串扰和低辐射等特性,业界推荐使用低压差分信号(LowVoltage Differential Signaling,LVDS)替代 TTL信号进行信号传输。

LVDS是20世纪90年代才出现的一种数据传输和接口技术,采用低压差分信号传输模式,核心技术是采用非常低的电压摆幅完成高速差分信号传输,可以实现点对点或一点对多点的连接,具有低功耗、低误码率、低串扰和低辐射等特点,其传输介质可以是PCB走线,或特制电缆。在对信号完整性、信号抖动及共模特性要求较高的应用场合,LVDS技术得到了越来越广泛的应用,如在计算机、通信设备和消费电子等领域。

LVDS 输出接口利用非常低的电压摆幅(约350mV),在两条PCB走线或一对平衡电缆上进行差分数据的传输,即低压差分信号传输,信号传输速率范围从几百Mbps到1Gbp/s左右。差分数据传输方式比单端数据传输对共模输入噪声有更强的抵抗能力,原因在于:利用差分线进行信号传输时,一条信号线传输正向信号,另一条信号线传输反向信号,两条差分信号线流经的电流及电压幅度相反,在接收端只关心两信号的差值,可以消除差分传输线上的共模噪声;由于两条传输信号线的极性相反,辐射产生的电磁场可以相互抵消,所以泄漏的电磁能量较少,对其他传输信号的影响较小。综上所述,利用LVDS技术进行信号传输,不但可以保持较高的传输速率,同时实现了低噪声、低功耗和低电磁辐射的功能。

LVDS的国际标准有两个:IEEE 1596.3和TIA/EIA(电讯工业联盟/电子工业联盟) ANSI/TIA/EIA-644。IEEE1596.3标准于1996年3月通过,主要面向可扩展一致接口(Scalable Coherent Interface,SCI),该标准定义了LVDS的电特性,还涉及SCI协议中包交换时的编码定义。ANSI/EIA-644标准于1995年11月通过,主要定义了LVDS的电气特性,推荐LVDS的最高数据传输速率为655Mbps,而LVDS在无衰耗传输线上的理论最高传输速率可达1.923Gbps。以上两个标准都注重对LVDS接口的电气特性和互连与线路端接等方面的规范,对于生产工艺、传输介质和供电电压等则没有明确规定,因此上述两个标准中都指定了与物理介质无关的特性,保证了LVDS能成为多用途的接口标准。

2 LVDS典型电路简介

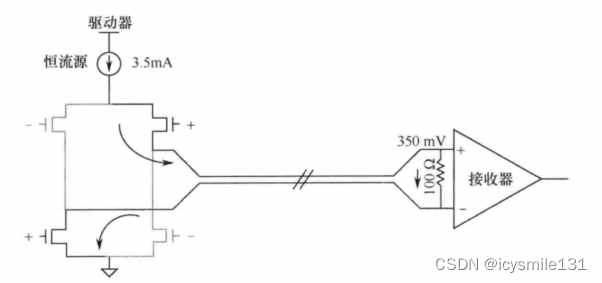

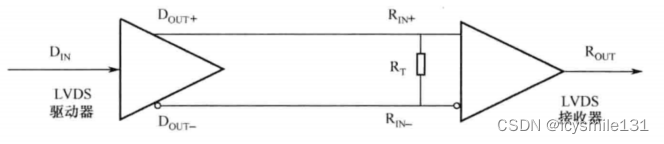

LVDS电路由驱动器、接收器及互连器组成,如图1所示。驱动器实现TTL或CMOS信号到LVDS信号的转换,接收器则实现LVDS信号到TTL或CMOS信号的转换。互连器包含电缆、PCB上的差分信号线及匹配电阻。LVDS的驱动器由一个驱动差分线对的电流源组成,驱动器电源为恒流源,输出3.5mA电流。为防止传输时信号在介质终端发生反射,同时减少电磁干扰,LVDS要求使用一个与介质相匹配的终端电阻,通常选择100Ω。终端匹配电阻终止环流信号,应尽可能靠近接收器输入端放置。由于接收器具有很高的输入阻抗,所以驱动器输出的电流大部分都流过匹配电阻,因此在接收器输入端产生的电压摆动幅度为350mV。

图1 LVDS电路结构示意图

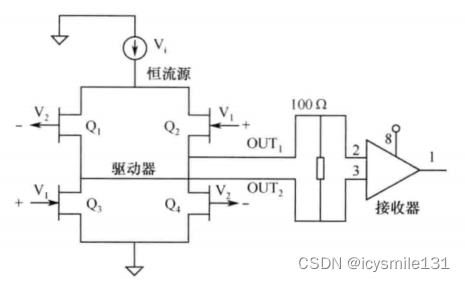

LVDS的工作原理如图2所示,Q1、Q2、Q3和Q4是尺寸工艺相同的nMOS 管, V1和V2是由同一输入CMOS信号导出的互为反相的信号,输出OUT1和OUT2与100Ω的终端电阻构成回路。当V1为高电平时,V2为低电平,此时Q3和Q2管导通,Q1和Q4管截止,电流从OUT1方向流向OUT2,并产生350mV的压降;当V1为低电平时,V2为低电平,此时Q1和Q4管导通,Q2和Q3管截止,电流从OUT2方向流向OUT¡,并产生350mV的压降。通过驱动器翻转,可以改变流经电阻的电流方向,从而产生有效的逻辑“1”和逻辑“0”状态。

LVDS物理接口通常使用1.2V偏置电压作为基准,电压摆动幅度为350mV,LVDS信号电平变化范围为0.85~1.55V,LVDS由逻辑“0”电平到逻辑“1”电平变化的时间比TTL和CMOS电平要快得多,因此LVDS信号可以支持更高的传输速率。LVDS的低幅驱动信号实现了高速操作,并减小了功率消耗。LVDS可以大幅降低功耗,因而在单个电路板上可以集成更多的接口驱动器和接收器,提高了PCB的设计集成度,并有利于降低系统成本。

图2 LVDS的工作原理图

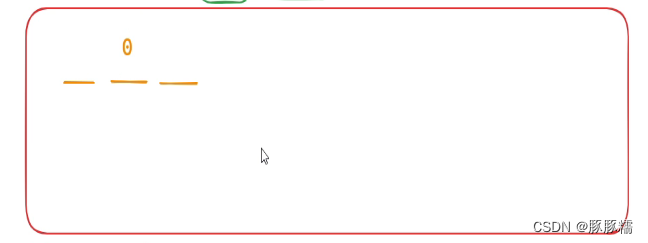

LVDS的传输距离因传输介质不同而存在差异,不同规格的PCB材质或电缆类型会对信号传输质量造成不同影响,从而导致最大传输距离存在偏差。PCB走线通常允许传输大约几十厘米的距离,双绞线电缆则允许传输大约几米的距离。数据传输速率受制于传输距离带来的影响,1Gbps的LVDS信号大概只能在1米左右长度的优质电缆上传输,但在100Mbps下传输距离可达到10米左右。LVDS支持包括点到点、点到多点等多种应用模式。点到点连接是LVDS的典型应用模式,如图3所示,包含一个驱动器,一个接收器,以及将两者连接起来的一对电缆(或PCB走线)和接收端的终端电阻。

图3 LVDS的点对点链路

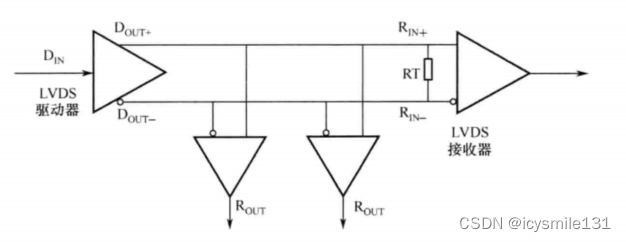

点到多点传输方式基于多分支总线拓扑结构,由一个驱动器连接多个接收器构成,如图4所示。

图4 LVDS的点对多点链路