GIC重点寄存器

1.中断分发器寄存器(Distributor register )

a.Distributor Control Register(中断分发控制寄存器), GICD_CTLR

PurposeEnables the forwarding of pending interrupts from the Distributor to the CPU interfaces使能将挂起的中断从分发器转发到CPU接口

EnableGrp1 (Group 1 Enable)

- 位位置:[1]

- 功能:全局使能位,用于控制是否将挂起的组1(Group 1)中断从中断分发器转发到CPU接口。

- 0:组1中断不被转发。

- 1:组1中断被转发,但需遵守优先级规则。

EnableGrp0 (Group 0 Enable)

- 位位置:[0]

- 功能:全局使能位,用于控制是否将挂起的组0(Group 0)中断从中断分发器转发到CPU接口。

- 0:组0中断不被转发。

- 1:组0中断被转发,但需遵守优先级规则。

b.Interrupt Group Registers(中断分组寄存器), GICD_IGROUPRn

PurposeThe GICD_IGROUPR registers provide a status bit for each interrupt supported by the GIC.Each bit controls whether the corresponding interrupt is in Group 0 or Group 1.GICD_IGROUPR寄存器为GIC支持的每个中断提供一个状态位。每个位控制相应的中断是在组0还是组1中。

GICD_IGROUPR 位分配

位范围:GICD_IGROUPR寄存器中的位[31:0]用于存储每个中断的组状态。

组状态位:每个位对应一个中断源。设置为0表示对应的中断属于组0(Group 0),设置为1表示属于组1(Group 1)。

功能:组0中断通常是不可屏蔽的,而组1中断可以被CPU接口的中断优先级掩蔽位所屏蔽。

在启动或重置时,每个ID32或更高的中断重置为组0,因此所有spi都是组0,除非系统重新编程适当的GICD_IGROUPR位。

在ARM通用中断控制器(GIC)中,中断ID与GICD_IGROUPR(中断组寄存器)之间的关系是通过整数除法(DIV)和模运算(MOD)来确定的。这种关系允许系统根据中断ID来配置或查询特定中断的分组信息。以下是如何根据中断ID来确定其在GICD_IGROUPR中的分组信息的步骤:

确定GICD_IGROUPR寄存器编号:

对于给定的中断ID

m,首先使用整数除法来确定它属于哪个GICD_IGROUPR寄存器。计算公式为n = m DIV 32,这里的n表示GICD_IGROUPR寄存器的编号。计算GICD_IGROUPR寄存器的偏移量:

每个GICD_IGROUPR寄存器的地址可以通过公式

0x080 + (4*n)来计算,其中0x080是第一个GICD_IGROUPR寄存器的基地址,4*n是当前寄存器相对于第一个寄存器的偏移量。确定组状态位的位号:

在确定了GICD_IGROUPR寄存器后,需要找到中断ID

m在该寄存器中对应的位。这通过模运算m MOD 32来实现,结果给出了在GICD_IGROUPR寄存器中的具体位号。读取或设置组状态位:

一旦知道了GICD_IGROUPR寄存器的编号和位号,就可以读取或设置该位来查询或配置中断的分组状态。如果位值为1,则中断属于组1;如果位值为0,则中断属于组0。

c.Interrupt Set-Enable Registers(中断使能寄存器), GICD_ISENABLERn

PurposeThe GICD_ISENABLERs provide a Set-enable bit for each interrupt supported by the GIC.Writing 1 to a Set-enable bit enables forwarding of the corresponding interrupt from theDistributor to the CPU interfaces. Reading a bit identifies whether the interrupt is enabled.GICD_ISENABLERs为GIC支持的每个中断提供了一个使能位。

将1写入使能位可以使对应的中断从分发器转发到CPU接口。读取位可确定中断是否已启用。

Set-enable bits(设置使能位)

- 位范围:[31:0],共32位,每位对应一个特定的中断。

- 功能:对于SPIs(共享外设中断)和PPIs(私有外设中断),每位控制相应中断从中断分发器(Distributor)转发到CPU接口的使能状态。

读取(Reads)

- 0:对应中断的转发被禁用。

- 1:对应中断的转发被使能。

- 通过GICD_ISENABLER寄存器,系统可以精确控制哪些中断应该被使能,哪些应该被禁用

写入(Writes)

- 0:对位没有任何影响,即不会改变中断的使能状态。

- 1:使能对应中断的转发。写入1后,后续读取该位将返回值1,表示中断已被使能。

- 允许系统设计者根据需要动态调整中断的使能状态,以适应不同的运行条件或任务优先级。

SGIs(软件生成中断)

- 对于SGIs,位的读写行为是由IMPLEMENTATION定义的。

d.Interrupt Clear-Enable Registers(中断禁用寄存器), GICD_ICENABLERn

PurposeThe GICD_ICENABLERs provide a Clear-enable bit for each interrupt supported by theGIC. Writing 1 to a Clear-enable bit disables forwarding of the corresponding interrupt fromthe Distributor to the CPU interfaces. Reading a bit identifies whether the interrupt isenabled.GICD_ICENABLERs为GIC支持的每个中断提供一个Clear-enable位。将1写入Clear-enable位,将禁止从分发端向CPU接口转发相应的中断。读取位标识中断是否被启用。

Clear-enable bits(清除使能位)

- 位范围:[31:0],共32位,每位对应一个特定的中断。

- 功能:对于SPIs(共享外设中断)和PPIs(私有外设中断),每位控制相应中断从中断分发器(Distributor)转发到CPU接口的使能状态。

读取(Reads)

- 0:对应中断的转发被禁用。

- 1:对应中断的转发被使能。

写入(Writes)

- 0:对位没有影响,即不会改变中断的使能状态。

- 1:禁用对应中断的转发。写入1后,后续读取该位将返回值0,表示中断已被禁用。

SGIs(软件生成中断)

- 对于SGIs,位的读写行为是由IMPLEMENTATION定义的。

e.Interrupt Priority Registers(中断优先级寄存器), GICD_IPRIORITYRn

PurposeThe GICD_IPRIORITYRs provide an 8-bit priority field for each interrupt supported by theGIC. This field stores the priority of the corresponding interrupt.GICD_IPRIORITYRs为GIC支持的每个中断提供了一个8位优先级字段。该字段存储了相应中断的优先级。

GICD_IPRIORITYR 位分配

位范围:GICD_IPRIORITYR寄存器中的位[31:0]用于存储每个中断的优先级值。

优先级字段:每个优先级字段持有一个优先级值,这个值的范围是实现定义的(IMPLEMENTATION DEFINED)。值越低,对应中断的优先级越高。

优先级分组:寄存器被分为多个部分,每个部分对应一个特定的字节偏移(byte offset),分别是3、2、1和0。

功能:每个字段为单个中断持有优先级值。这部分描述了中断ID值如何确定GICD_IPRIORITYR寄存器的编号以及该寄存器中优先级字段的字节偏移。

For interrupt ID m, when DIV and MOD are the integer division and modulo operations:

• the corresponding GICD_IPRIORITYRn number, n , is given by n = m DIV 4• the offset of the required GICD_IPRIORITYRn is ( 0x400 + (4* n ))• the byte offset of the required Priority field in this register is m MOD 4, where:— byte offset 0 refers to register bits [7:0]— byte offset 1 refers to register bits [15:8]— byte offset 2 refers to register bits [23:16]— byte offset 3 refers to register bits [31:24].计算GICD_IPRIORITYR寄存器编号:对于给定的中断ID

m,使用整数除法(DIV)来确定它对应的GICD_IPRIORITYR寄存器编号n。计算公式为n = m DIV 4。计算GICD_IPRIORITYR寄存器的偏移量:

每个GICD_IPRIORITYR寄存器的地址可以通过公式

0x400 + (4*n)来计算,其中0x400是第一个GICD_IPRIORITYR寄存器的基地址,4*n是当前寄存器相对于第一个寄存器的偏移量。确定优先级字段的字节偏移量:

在确定了GICD_IPRIORITYR寄存器后,需要找到中断ID

m在该寄存器中对应的位。这通过模运算(MOD)来实现,计算公式为m MOD 4,结果给出了在寄存器中的字节偏移量。字节偏移量的含义如下:

字节偏移量3:对应寄存器的位[31:24]。

字节偏移量2:对应寄存器的位[23:16]。

字节偏移量1:对应寄存器的位[15:8]。

字节偏移量0:对应寄存器的位[7:0]。

f.Interrupt Processor Targets Registers(中断处理器目标寄存器), GICD_ITARGETSRn

PurposeThe GICD_ITARGETSRs provide an 8-bit CPU targets field for each interrupt supportedby the GIC. This field stores the list of target processors for the interrupt. That is, it holdsthe list of CPU interfaces to which the Distributor forwards the interrupt if it is asserted andhas sufficient priorityGICD_ITARGETSRs为GIC支持的每个中断提供一个8位CPU目标字段。这个字段存储中断的目标处理器列表。也就是说,它保存了一个CPU接口的列表,如果中断发生断言且具有足够的优先级,则分发器将中断转发到该CPU接口

GICD_ITARGETSR 位分配

位范围:GICD_ITARGETSR寄存器中的位[31:0]用于存储每个中断的目标CPU接口信息。

CPU目标字段:每个字段为单个中断持有CPU目标列表。这意味着每个中断可以被配置为发送到一个或多个CPU接口。

字节偏移量:寄存器被分为多个部分,每个部分对应一个特定的字节偏移(byte offset),分别是3、2、1和0。

功能:每个位在CPU目标字段中对应于系统中的一个处理器。例如,位值为0x3意味着中断将被发送到处理器0和1。对于GICD_ITARGETSR0到GICD_ITARGETSR7,读取任何CPU目标字段将返回执行读取操作的处理器编号。

A CPU targets field bit that corresponds to an unimplemented CPU interface is RAZ/WI.For interrupt ID m , when DIV and MOD are the integer division and modulo operations:• the corresponding GICD_ITARGETSRn number, n , is given by n = m DIV 4• the offset of the required GICD_ITARGETSR is ( 0x800 + (4* n ))• the byte offset of the required Priority field in this register is m MOD 4, where:— byte offset 0 refers to register bits [7:0]— byte offset 1 refers to register bits [15:8]— byte offset 2 refers to register bits [23:16]— byte offset 3 refers to register bits [31:24].未实现的CPU接口:如果CPU目标字段中的某位对应于未实现的CPU接口,那么该位的行为是读时忽略(RAZ,Read As Zero)和写时忽略(WI,Write Ignore)。

计算GICD_ITARGETSR寄存器编号:

对于给定的中断ID

m,使用整数除法(DIV)来确定它对应的GICD_ITARGETSR寄存器编号n。计算公式为n = m DIV 4。计算GICD_ITARGETSR寄存器的偏移量:每个GICD_ITARGETSR寄存器的地址可以通过公式

0x800 + (4*n)来计算,其中0x800是第一个GICD_ITARGETSR寄存器的基地址,4*n是当前寄存器相对于第一个寄存器的偏移量。确定优先级字段的字节偏移量:在确定了GICD_ITARGETSR寄存器后,需要找到中断ID

m在该寄存器中对应的字节偏移量。这通过模运算(MOD)来实现,计算公式为m MOD 4,结果给出了在寄存器中的字节偏移量。字节偏移量的含义如下:

字节偏移量3:对应寄存器的位[31:24]。

字节偏移量2:对应寄存器的位[23:16]。

字节偏移量1:对应寄存器的位[15:8]。

字节偏移量0:对应寄存器的位[7:0]。

2.CPU接口单元寄存器

在ARM通用中断控制器(GIC)中,CPU接口单元寄存器是用于控制和配置每个CPU接口的中断行为的一组寄存器。这些寄存器允许每个CPU核心独立地管理其中断,包括中断的使能、优先级掩蔽和中断处理。

a.CPU Interface Control Register(CPU接口控制寄存器), GICC_CTLR

Purpose

Enables the signaling of interrupts by the CPU interface to the connected processor, andprovides additional top-level control of the CPU interface. In a GICv2 implementation, thisincludes control of the end of interrupt (EOI) behavior.允许CPU接口向连接的处理器发出中断信号,并提供对CPU接口的额外顶层控制。在GICv2(通用中断控制器版本2)实现中,这包括对中断结束(EOI,End of Interrupt)行为的控制。

NoteIn a GICv2 implementation that includes the GIC Security Extensions, independent EOIcontrols are provided for:• Accesses from Secure state. This control applies to the handling of both Group 0 andGroup 1 interrupts.• Accesses from Non-secure state. This control only applies to the handling of Group 1interrupts.The EOI controls affect the behavior of accesses to GICC_EOIR and GICC_DIR .在包含GIC安全扩展的GICv2实现中,为以下情况提供了独立的EOI控制:

- 从安全状态(Secure state)的访问。此控制适用于处理Group 0(组0)和Group 1(组1)中断。

- 从非安全状态(Non-secure state)的访问。此控制仅适用于处理Group 1中断。

EOI控制影响对GICC_EOIR(通用中断控制器结束中断寄存器)和GICC_DIR(通用中断控制器去激活寄存器)的访问行为。

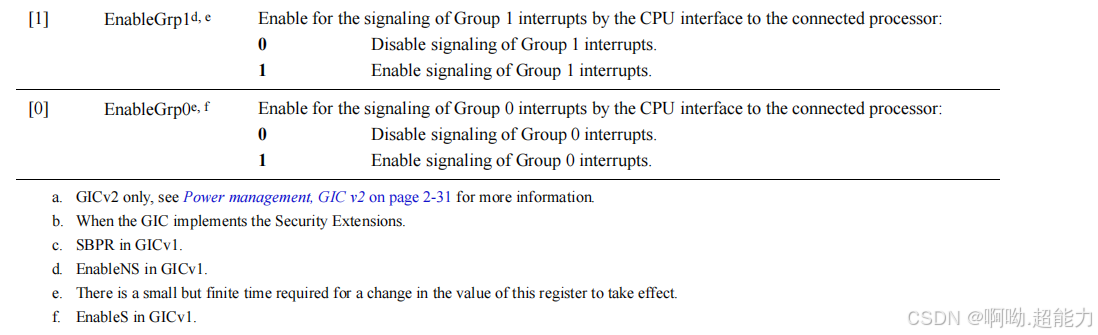

EnableGrp1d,e(位[1]):用于控制CPU接口向连接的处理器发送Group 1中断信号的能力。

0:禁用Group 1中断的信号发送。1:启用Group 1中断的信号发送。

EnableGrp0e,f(位[0]):用于控制CPU接口向连接的处理器发送Group 0中断信号的能力。

0:禁用Group 0中断的信号发送。1:启用Group 0中断的信号发送。

附加说明:

a:仅适用于GICv2,

b:当GIC实现安全扩展时。

c:在GICv1中,这对应于SBPR(Secure Binary Point Register,安全二进制点寄存器)。d:在GICv1中,这对应于EnableNS(启用非安全中断)。

e:更改此寄存器的值需要一小段但有限的时间才能生效。

f:在GICv1中,这对应于EnableS(启用安全中断)。

b.Interrupt Priority Mask Register, GICC_PMR

PurposeProvides an interrupt priority filter. Only interrupts with higher priority than the value in thisregister are signaled to the processor.提供一个中断优先级过滤器。只有优先级高于此寄存器中的值的中断才会向处理器发出信号。NoteHigher priority corresponds to a lower Priority field value.

位分配:[7:0]:优先级位,用于设置优先级屏蔽级别。

优先级功能:如果中断的优先级高于GICC_PMR寄存器中设置的值,CPU接口将向处理器发出中断信号。

支持的优先级级别:如果GIC(General Interrupt Controller)支持的优先级级别少于256个,那么一些位将被忽略(RAZ/WI,即Read As Zero/Write Ignored):

16个支持的优先级级别:Bit[3:0] = 0b0000。

32个支持的优先级级别:Bit[2:0] = 0b000。

64个支持的优先级级别:Bit[1:0] = 0b00。

128个支持的优先级级别:Bit[0] = 0。

c.Interrupt Acknowledge Register, GICC_IAR

Purpose

The processor reads this register to obtain the interrupt ID of the signaled interrupt. Thisread acts as an acknowledge for the interrupt.处理器读取这个寄存器以获得信号中断的中断ID。这个读取操作相当于对中断的确认。

CPUID(CPUID):位[12:10]用于在多处理器实现中标识请求中断的处理器。对于SGI(软件生成中断),这个字段标识发起中断请求的处理器。它返回发起请求的CPU接口编号,例如,值为3意味着请求是由写入GICD_SGIR在CPU接口3上生成的。对于所有其他中断,这个字段是读时忽略(RAZ,Read As Zero)。

- 读取GICC_IAR返回CPU接口上最高优先级的挂起中断的中断ID。

- 如果中断分发器到CPU接口的中断转发被禁用,或者CPU接口到连接的处理器的中断信号被禁用,或者CPU接口上没有足够优先级的挂起中断来向处理器发出信号,那么读取GICC_IAR将返回一个虚假中断ID 1023。

中断ID(Interrupt ID):

位[9:0]表示中断ID

d.End of Interrupt Register, GICC_EOIR

PurposeA processor writes to this register to inform the CPU interface either:• that it has completed the processing of the specified interrupt• in a GICv2 implementation, when the appropriate GICC_CTLR .EOImode bit is setto 1, to indicate that the interface should perform priority drop for the specifiedinterrupt.处理器向此寄存器写入数据,以通知CPU接口以下信息:

完成中断处理:处理器已经完成了对指定中断的处理。

执行优先级降低:在GICv2实现中,当相应的GICC_CTLR.EOImode位被设置为1时,指示CPU接口应该为指定的中断执行优先级降低。

CPUID(CPUID):

位[12:10]用于在多处理器实现中标识处理器。如果写入操作是针对软件生成中断(SGI),这个字段包含从相应的GICC_IAR(中断确认寄存器)访问中得到的CPUID值。在所有其他情况下,这个字段是设置为0(SBZ,Set to 0)。

EOIINTID(中断结束ID):

位[9:0]表示从相应的GICC_IAR访问中得到的中断ID值。这个值用于确认哪个中断已经被处理。

- 中断处理完成:写入GICC_EOIR的值必须是从GICC_IAR读取的中断ID。这是为了通知GIC中断已经被处理完毕。

- 多处理器系统:在多处理器系统中,CPUID字段确保了中断可以被正确地分配给处理它的处理器。

- 中断识别:EOIINTID字段允许GIC识别和确认哪个中断已经被处理,这对于中断的管理和调度至关重要。

For every read of a valid Interrupt ID from the GICC_IAR, the connected processor must perform a matching write to the GICC_EOIR. The value written to the GICC_EOIR must be the interrupt ID read from the GICC_IAR.

If a read of the GICC_IAR returns the ID of a spurious interrupt, software does not have to make a corresponding write to the GICC_EOIR. If software writes the ID of a spurious interrupt to the GICC_EOIR, the GIC ignores that write.对于从GICC_IAR读取的有效中断ID,与其相连的处理器必须执行相应的写操作到GICC_EOIR。写入GICC_EOIR的值必须是从GICC_IAR读取的中断ID。如果从GICC_IAR读取的ID是虚拟中断ID,软件不需要进行相应的写操作到GICC_EOIR。如果软件将虚拟中断ID写入GICC_EOIR,GIC会忽略该写操作。

NoteFor compatibility with possible extensions to the GIC architecture specification, ARM recommends that software preserves the entire register value read from the GICC_IAR when it acknowledges the interrupt, and uses that entire value for its corresponding write to the GICC_EOIR.为了兼容对GIC架构规范可能的扩展,ARM建议软件在确认中断时保留从GICC_IAR读取的整个寄存器值,并将整个值用于对GICC_EOIR的相应写入。

I.MX6ULL中断处理

GIC控制器寄存器地址

ARM Platform Memory Map

支持的中断源个数

全局中断控制器(GIC)从所有芯片源收集多达128个中断请求,并提供一个接口到Cortex A7 CPU。前32个中断是cpu接口的私有中断。这些中断不包括在下面的表中。除了那些私有的CPU中断外,所有中断都连接到GPC。每个中断都可以配置为正常中断或安全中断。还支持软件力寄存器和软件优先级屏蔽。

This table describes the ARM Cortex A7 interrupt sources:(下表描述了ARM Cortex A7的中断源 )

部分GPIO管脚

Cortex-A7内核的GIC支持多达512个中断ID,i.MX6ULL芯片支持160个中断源,这些中断源包括私有外设中断(PPI)、共享外设中断(SPI)和软件生成中断(SGI)

- ID0-ID15:用于SGI,这些中断是软件生成的,用于处理器间通信。

- ID16-ID31:用于PPI,这些中断是私有的,每个CPU核心都有自己的PPI。

- ID32-ID159:用于SPI,这些中断可以被多个CPU核心共享。

通过GPIO(通用输入输出)控制器和GIC(通用中断控制器)来处理外部中断的流程

1.GPIO interrupt configuration register1 中断配置寄存器(GPIOx_ICR1)和GPIO interrupt configuration register2 中断配置寄存器(GPIOx_ICR2)

2.GPIO interrupt mask register 中断屏蔽寄存器(GPIOx_IMR)

在GPIO(通用输入输出)控制器中,GPIO_IMR 寄存器包含了每个中断线的掩蔽位(masking bits)。这些掩蔽位用于控制是否允许相应的中断线向中断控制器发送中断请求

GPIO_IMR 通常与中断使能寄存器GPIO_ISR一起使用,后者用于启用或禁用特定引脚的中断功能。

中断掩蔽(Interrupt Masking):

GPIO_IMR寄存器中的每个位对应一个GPIO引脚的中断掩蔽状态。- 当一个位被设置为0时,对应的中断线被掩蔽,即该引脚的中断请求将不会传递到中断控制器。

- 当一个位被设置为1时,对应的中断线未被掩蔽,允许中断请求被发送

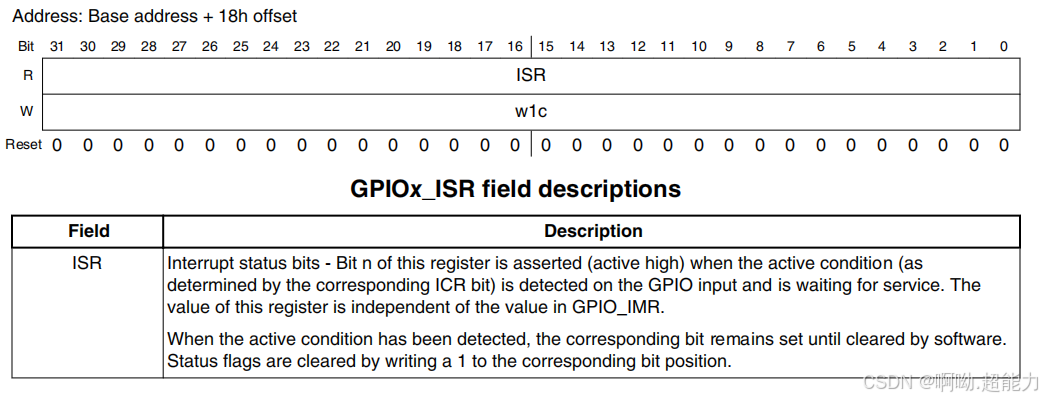

3.GPIO interrupt status register 中断状态寄存器(GPIOx_ISR)

GPIO_ISR的作用是中断状态指示器。每个位表示是否满足相应输入信号的中断条件。当一个中断条件被满足时(由相应的中断条件寄存器字段决定),在这个寄存器中设置相应的位。在读访问中,同步需要两个等待状态。重置需要一个等待状态。

中断状态位(Interrupt status bits)是用于指示GPIO(通用输入输出)输入信号中断状态的位。

中断状态位 - 该寄存器的第n位(活动高电平)在检测到GPIO输入端(由相应的ICR位确定)的活动条件时被置位,并等待服务。 该寄存器的值与GPIO_IMR的值无关。 当检测到活动条件时,相应的位将保持设置状态,直到通过软件清除。 状态标志位可以通过向相应的位写入1来清除。

- 此寄存器的值独立于GPIO_IMR(中断掩蔽寄存器)中的值。这意味着即使中断被掩蔽,中断状态位仍然可以被设置。

4.CPSR(Current Program Status Register,当前程序状态寄存器)

CPSR(Current Program Status Register,当前程序状态寄存器)是ARM架构中一个重要的寄存器,用于存储处理器的状态和控制信息。在系统启动或任务切换时,CPSR的初始化是至关重要的。

中断使能位(Interrupt Enable bits):CPSR中的I位(IRQ)和F位(FIQ)控制普通中断(IRQ)和快速中断(FIQ)的使能。

I位(IRQ):在CPSR中,I位实际上控制的是普通中断(IRQ,Interrupt Request)的使能。当I位被置为1时,普通中断被禁用;当I位被清零(置为0)时,普通中断被使能。这意味着如果I位为1,处理器将不会响应IRQ中断请求。

F位(FIQ):在CPSR中,F位控制的是快速中断(FIQ,Fast Interrupt Request)的使能。与I位类似,当F位被置为1时,快速中断被禁用;当F位被清零时,快速中断被使能。快速中断通常用于需要快速响应的紧急情况。

通过直接操作CPSR(当前程序状态寄存器)来实现ARM处理器上启用和禁用IRQ(普通中断)

示例代码:

启用IRQ函数 (enable_irq)

int enable_irq(void)

{int status;asm("mrs r0,cpsr\n" // 将CPSR的值移动到r0寄存器"mov r1,#1\n" // 将立即数1加载到r1寄存器"bic r0,r0,r1,lsl #7\n" // 清除r0的第7位(I位),左移7位是为了定位到I位"msr cpsr,r0\n" // 将修改后的r0值写回CPSR"mov %0,r0\n" // 将r0的值存储到status变量中:"=r"(status) // 输出操作数,将结果存储在status中::"r0","r1" // 破坏列表,指定r0和r1寄存器在asm中被修改);return status;

}禁用IRQ函数 (disable_irq)

int disable_irq(void)

{int status;asm("mrs r0,cpsr\n" // 将CPSR的值移动到r0寄存器"mov r1,#1\n" // 将立即数1加载到r1寄存器"orr r0,r0,r1,lsl #7\n" // 通过OR操作设置r0的第7位(I位)"msr cpsr,r0\n" // 将修改后的r0值写回CPSR"mov %0,r0\n" // 将r0的值存储到status变量中:"=r"(status) // 输出操作数,将结果存储在status中::"r0","r1" // 破坏列表,指定r0和r1寄存器在asm中被修改);return status;

}结语:

无论你是初学者还是有经验的开发者,我希望我的博客能对你的学习之路有所帮助。如果你觉得这篇文章有用,不妨点击收藏,或者留下你的评论分享你的见解和经验,也欢迎你对我博客的内容提出建议和问题。每一次的点赞、评论、分享和关注都是对我的最大支持,也是对我持续分享和创作的动力