前言

- 引入扇出的概念

- 介绍FPGA中的全局网络

- 为后续时序优化埋下伏笔

扇出

- 在FPGA设计中扇出是一个重要的概念,所谓的扇出就是一个控制信号所能控制的数据信号的总个数,比如ctrl信号的扇出就是16

reg ctrl = 0;

reg [15:0] out = 0;

always @(posedge clk ) beign : testif (ctl == 1'b1) beignout <= 16`d0;end else beginout <= 16`d1;end----------------------------或者------------------------------wire ctrl;

wire [15:0] out;

assign out = ctrl ? 16`d0 : 16`d1;

全局网络

- 为什么说全局网络

- 因为在FPGA或者IC设计中,信号的到达不是我们想的都能瞬时且同一时刻到达,也就说同一个信号到达不同的寄存器单元的时钟延迟可能不一样,这就导致存在始终偏移,如果不做任何优化措施,会经常遇到时序问题,只不过这个事情EDA帮我们做了很多。

- 全局网络在FPGA中具有比较重要的地位,一般来讲当一个信号的扇出达到一定程度的时候,可以称这个信号为全局网络,在FPGA设计中,比较明显的几个全局网络分别是

- 时钟信号

- 复位信号

- 使能信号

- 清零信号

- 在同步电路设计中,时钟信号覆盖整个FPGA设计

- 复位信号的扇出一般情况下不如时钟信号扇出多,主要原因:

- 复位信号一般在控制通路中使用

- 在数据通路中由于数据的流动性一般可以省去复位信号(一些对初始值有要求的信号可能需要复位)

- 如果在一个设计中不分控制通路还是数据通路,给每一个时序逻辑都加以复位,可能会在给整个设计在布线上制造麻烦,导致时序违例(如果你没遇到过这种情况,第一个原因是eda帮我做了优化,第二个就是你的工程太小了)

- 使能信号

- 至于为什么说使能信号也是全局网络的,是因为它存在一定的可能性,比如像复位信号那样使用不也就是全局网络了吗…

- 清零信号

- 异步清零类似复位

- 同步清零类似使能

时序优化

关于时序优化中我会单独做几次笔记与大家交流时序优化的方法和经验,

-

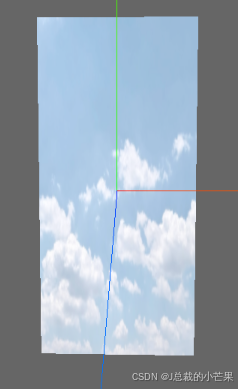

就像上面我们说的那样信号的到达不是我们想的都能瞬时且同一时刻到达,也就说同一个信号到达不同的寄存器单元的时钟延迟可能不一样,这就导致存在始终偏移, 扇出大的信号的很难做到尽可能同时到达目的单元,这也就导致数据建立时间不足,导致时序违例,如图

-

-

对于因为扇出过大导致的时序违例,可以通过逻辑复制的方式进行优化

- 把信号复制多份控制不同的寄存器