1. 问题描述

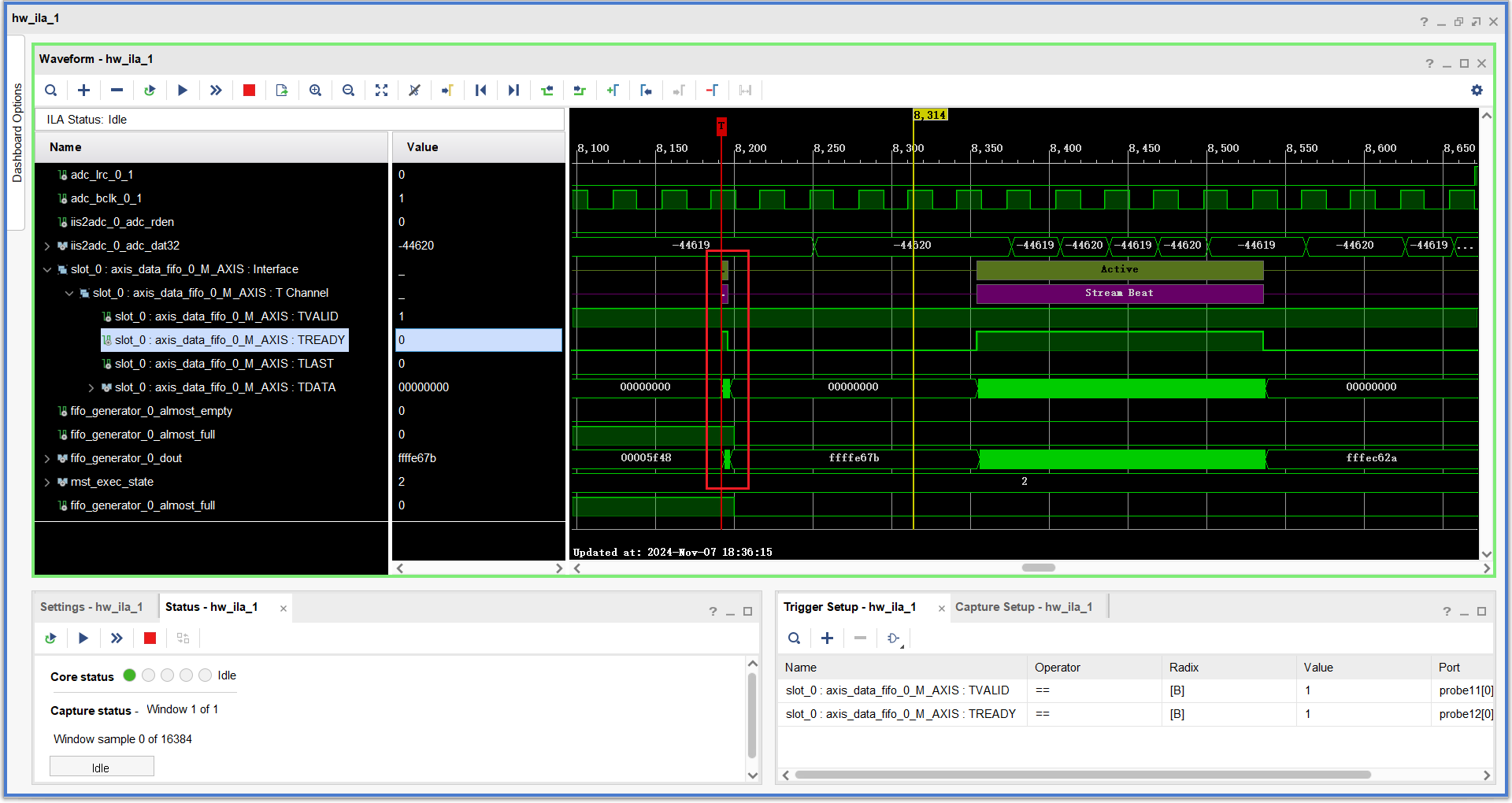

在突发的过程中总是一旦使用XAxiDma_SimpleTransfer函数就会出现AXI STREAM信号的READY信号先拉高4个数据(32位)的时钟后会迅速拉低,换句话说就是一旦PS端发起了XAxiDma_SimpleTransfer,AXI总线的READY信号就会拉高四个节拍,这样就会导致传输的数据出现问题。究其原因,Xilinx在其手册中有说明,在没有任何设置的情况下(即在其被编程运行之前),AXI DMA 在接收了四个节拍的流数据后,会将 <font style="color:rgb(77, 77, 77);">s_axis_s2mm_tready</font> 信号拉低。这将限制输入数据流。为了尽量减少节流,确保 AXI DMA 在实际数据到达之前就已经设置好并运行。

这样数据就不会连续进行传输…

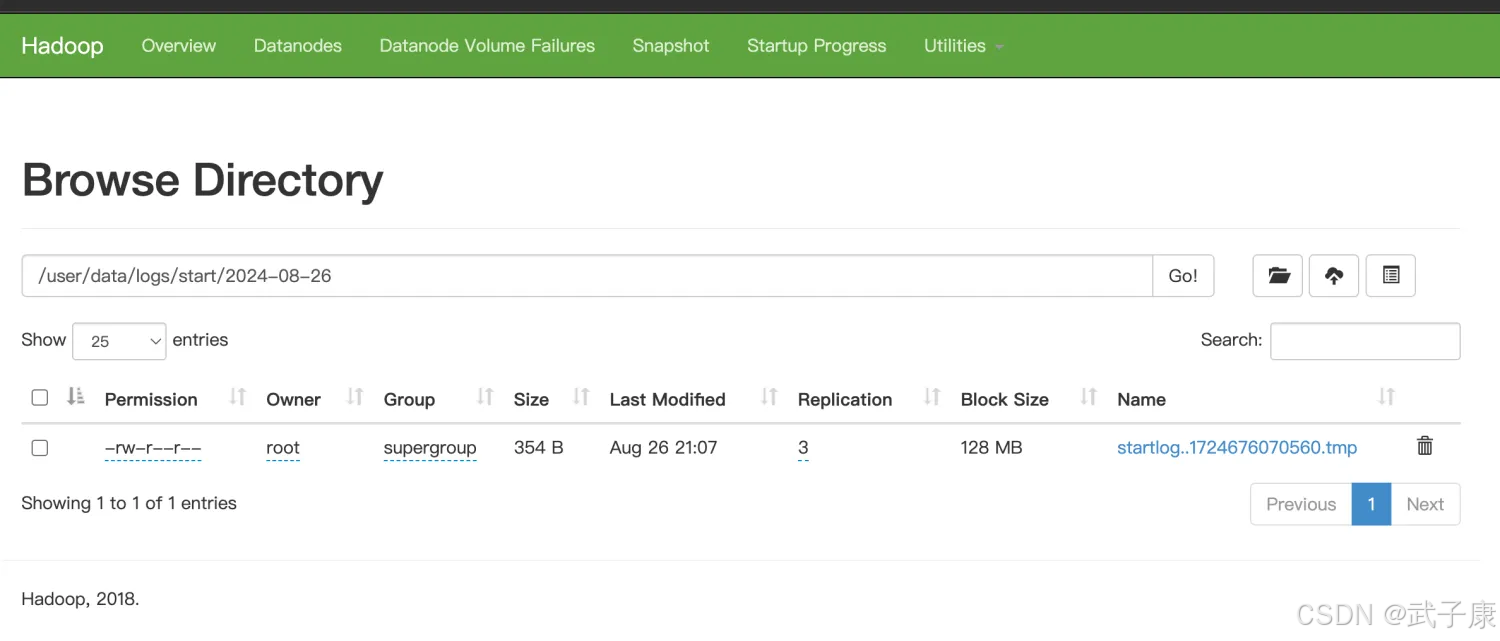

下面是具体的ILA示意图:

2. 项目说明

- 系统说明

做音频采集系统,使用ZYNQ7020采集音频IIS的32位数据到PS的DDR,音频的采样率是48K

AXI DMA IP在其中的作用是通过读取存储IIS音频的FIFO数据到PS的DDR中

- AXI DMA IP参数设置

突发的长度是256,位宽是32位