视频链接

PCIE转网口电路设计01_哔哩哔哩_bilibili

PCIe转网口电路设计

1、PCIE转网口电路设计基本介绍

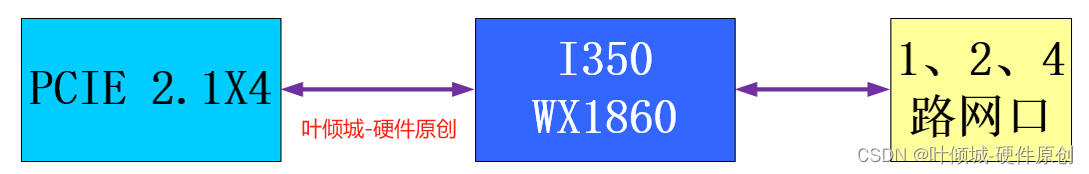

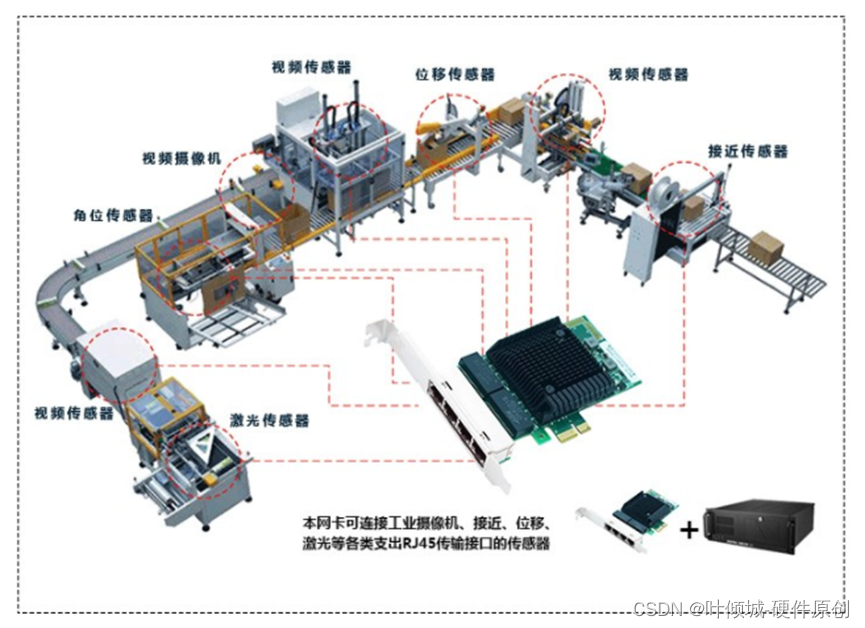

pcie转网口的设计,一般有intel (i350)和网讯(wx1860)两种方案。

2、PCIE转网口的方案

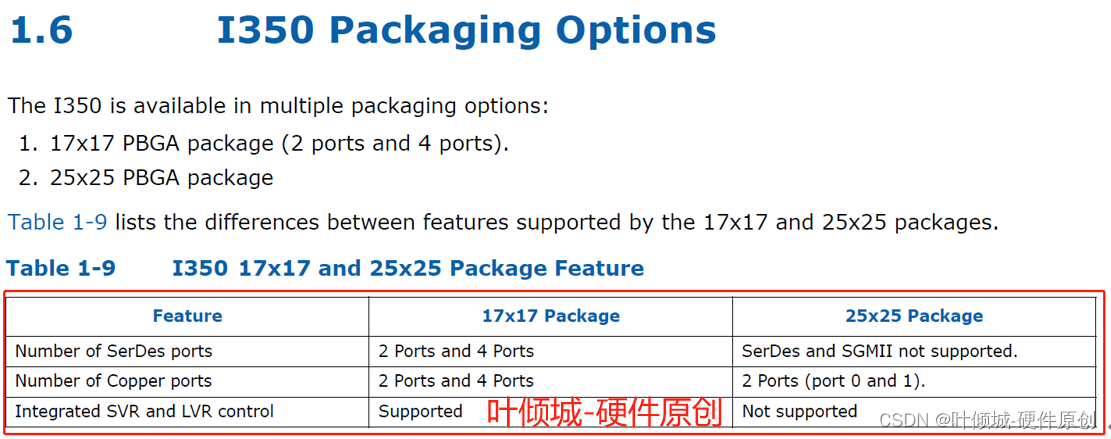

2.1、I350

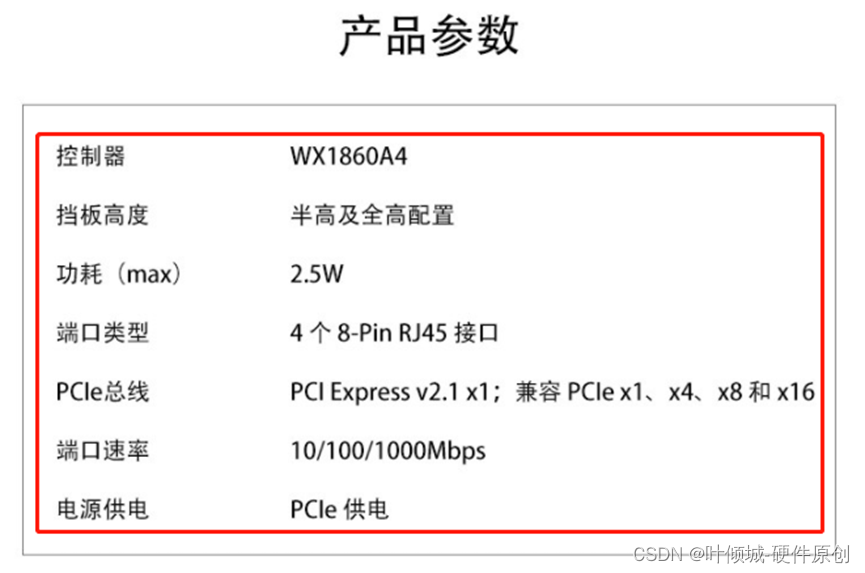

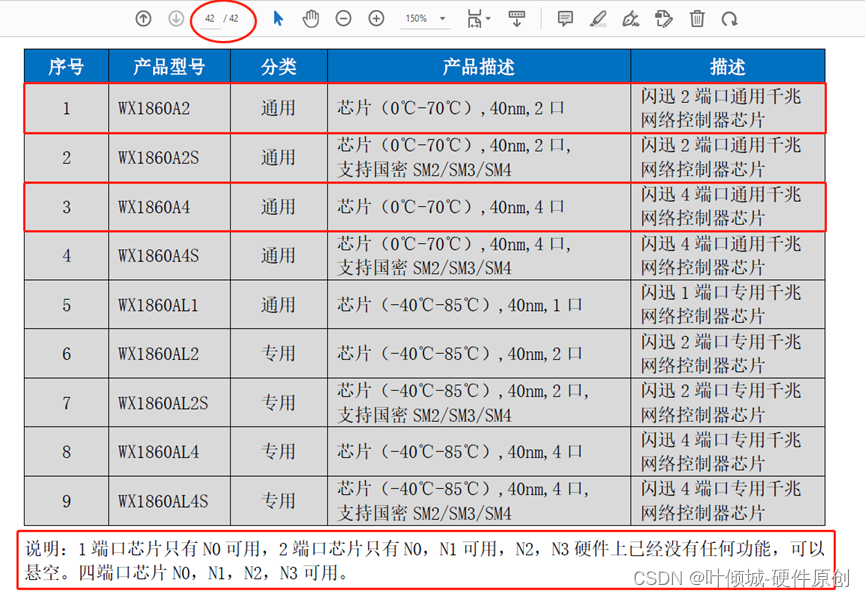

2.2、WX1860 (网迅) 国产化(★)

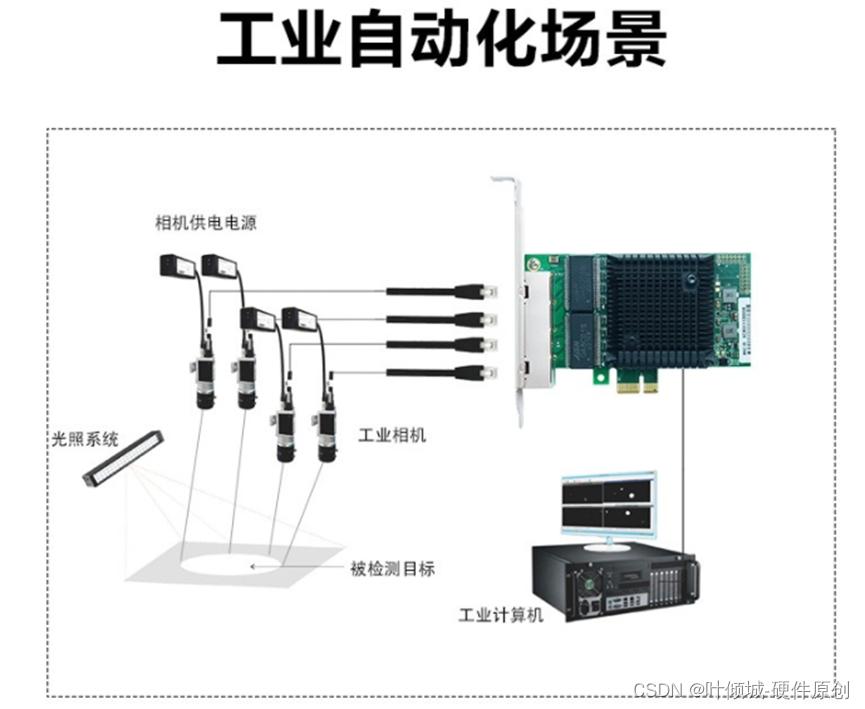

LRES2028PF-4SFP是深圳市联瑞电子有限公司在国产主控制器方案基础上开发的一款PCI Express V2.1 x4四光口千兆以太网网络适配器。

2.3、pcie转网口的其他方案

2.4、I350和WX1860的区别

2.4.1、网卡基本性能

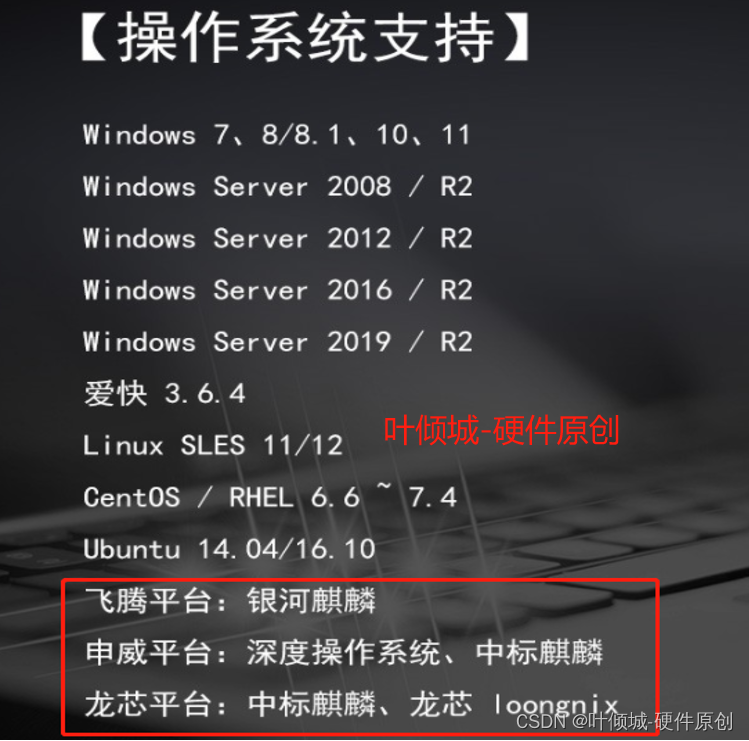

2.4.2、操作系统支持

2.4.3、其他(参考元器件手册里面的7个参数)

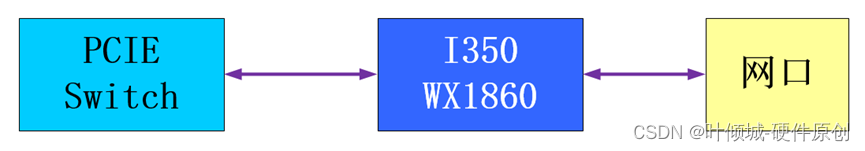

3、套片、桥片、PCIE switch等基本介绍

3.1、套片(不需要)

3.2、PCIE switch

3.3、桥片

3.4、CPU本身自带的PCIE接口

3.5、采用PCIE设计,适用于PCI Express x1,X4,X8,X16插槽。

4、网络相关概念

4.1、TS1588

IEEE 1588的全称是“网络测量和控制系统的精密时钟同步协议标准”。

4.2、NC-SI协议

NC-SI(Network Controller Sideband Interface)是一个由分布式管理任务组(Distributed Management Task Force, DMTF)定义的用于支持服务器带外管理的边带接口网络控制器的工业标准。

4.3、EFUSE--芯片存储

可用于存储MEM repair的存储修复数据,也可用于存储芯片的信息。

4.4、DFT测试

DFT,即可测试性设计(Design for Testability, DFT)是一种集成电路设计技术。

4.5、WOL功能

Wake-on-LAN简称WOL,中文译为“网络唤醒”、“远端唤醒”技术。

4.6、bypass功能

bypass,就是可以通过特定的触发状态(断电或死机)让两个网络不通过网络安全设备的系统,而直接物理上导通。

4.7、serdes接口(序列化反序列化器)

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

4.8、BMC

BMC,执行伺服器远端管理控制器

4.9、DMA

DMA(Direct Memory Access,直接存储器访问)

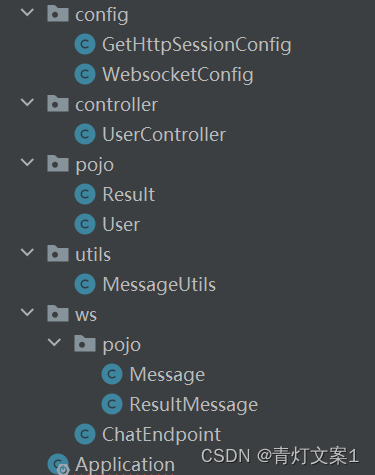

5、PCIE转网口(以WX1860)

网迅千兆以太网适配器包含四个千兆以太网端口,具有集成的硬件加速功能,能够执行TCP/UDP/IP校验和分载及TCP分段任务。

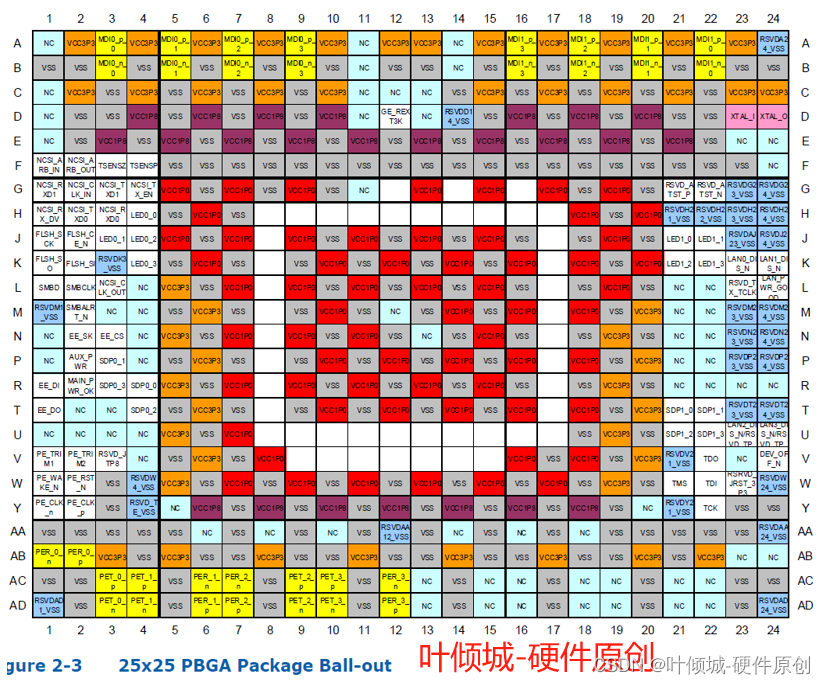

5.1、结构框图

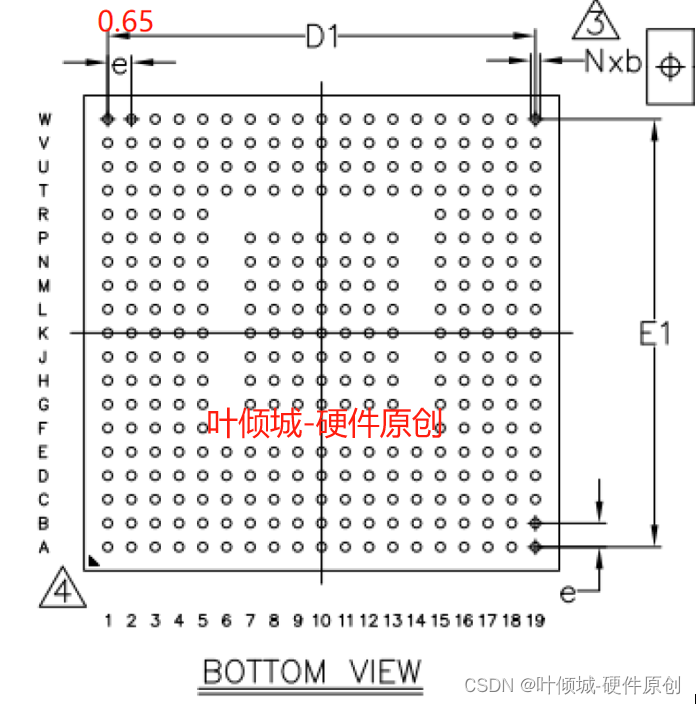

19*19-34=327

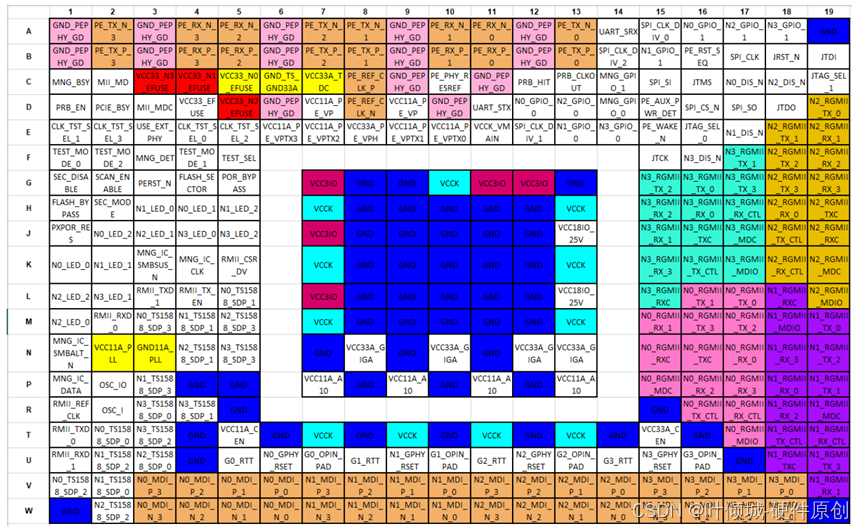

5.2、信号定义

5.2.1、Power supply (对应6.1)

总结:模拟3.3V & 数字3.3V、模拟1.1V & 数字1.1V

| Pin | I/O | 定义 |

| VCC33_N0_EFUSE VCC33_N1_EFUSE VCC33_N2_EFUSE VCC33_N3_EFUSE VCC33_EFUSE | P | EFUSE 模拟3.3V |

| VCC33A_TDC | 内部温度传感器模拟3.3V | |

| VCC33A_PE_VPH | PCIe模拟3.3V | |

| VCC33A_GIGA VCC33A_CEN | MDI 网口模拟3.3V | |

| VCCK_VMAIN | P | 内核数字电源1.1V |

| VCCK_AUX | 内核数字备用电源 1.1V | |

| VCC11A_PE_VP VCC11A_PE_VPTX0 VCC11A_PE_VPTX1 VCC11A_PE_VPTX2 VCC11A_PE_VPTX3 | P | PCIe 模拟电源 1.1V |

| VCC11A_A10 VCC11A_CEN | MDI网口模拟 1.1V | |

| VCC11A_PLL | PLL电源,模拟1.1V | |

| VCC18IO_25V | P | RGMII数字IO, 目前1.8V/2.5V模式不支持,需接到3.3V。 |

| VCC3IO | RGMII、Misc数字IO 3.3V | |

| GND | P | 电源地 |

| GND_PLL | P | PLL电源,通过磁珠单点接地 |

| GND_TS | P | 内部Thermal sensor电源,通过磁珠单点接地 |

5.2.2、Misc Interface (对应6.2)

| Pin | I/O | 定义 |

| prb_en | I/Down | 用于调试,N/C |

| prb_hit | O | 用于调试,N/C |

| prb_clkout | O | 用于调试,建议加测试点 |

| pcie_bsy | O | 高有效信号,用于指示PCIe 连接上有数据传输 |

| mng_bsy | O | 高有效信号用于指示 NCSI接口上的数据传输 |

| scan_enable | I/Down | 用于DFT测试。正常模式 N/C。 |

| test_sel test_mode_0 test_mode_1 test_mode_2 | I/Down | 用于调试,N/C |

| jtag_sel_0 jtag_sel_1 | I/Down | 选择 JTAG 接口的使用模块,2’b11 把芯片JTAG 接口连接在内部CPU,其它值用于调试。 (对应6.2.5) |

| clk_tst_sel_0 clk_tst_sel_1 clk_tst_sel_2 clk_tst_sel_3 | I/Down | 用于调试,N/C |

| flash_sector | I/Down | 选择用于初始化的 flash sector, N/C 0- 64KB sector 1- 256KB sector |

| flash_bypass | I/Down | 跳过 flash 初始化,用于调试,N/C |

| mng_det | I/UP | 用于调试, N/C |

| sec_disable | I/Down | 用于调试,N/C |

| use_ext_phy | I/Down | 高有效信号。有效时4个网口都选择用外部 RGMII PHY,否则4个网口都用内部PHY。 (对应6.2.6) |

| xtal_in xtal_out | I O | 外部无源晶振的输入,也可以直接输入25MHz 的有源时钟信号。 输出信号用于连接外部无源晶振。 (对应6.3) |

| sec_mode | I/UP | 用于调试, N/C |

| pe_rst_seq | I/Down | 用于调试, N/C |

| pe_aux_pwr_det | I/Down | 支持WoL,为高 不支持WoL,为低。 |

5.2.3、Internal PHY #0 #1 #2 #3 (13 X 4 对应6.4和6.6 )

| Pin | I/O | 定义 |

| n0_dis_n | I/UP | 网口#0 不使能信号,低有效(对应6.2.8) |

| n0_gphy_rset | A | 网口#0参考电阻接口,通过2.49KΩ±1%接地 |

| n0_led_0 | O | LED_0, Programmable LED which indicates by default activity, active high. Blink time 20-60ms adjustable, active high/low adjustable. |

| n0_led_1 | LED_1, Programmable LED which indicates by default a 100Mbps Link, active high. | |

| n0_led_2 | LED_2, Programmable LED which indicates by default a 1000Mbps Link, active high. | |

| n0_mdi_p_0 n0_mdi_n_0 | A | In MDI mode, this is the first pair in 1000Base-T |

| n0_mdi_p_1 n0_mdi_n_1 | In MDI mode, this is the second pair in1000Base-T | |

| n0_mdi_p_2 n0_mdi_n_2 | In MDI mode, this is the third pair in 1000Base-T | |

| n0_mdi_p_3 n0_mdi_n_3 | In MDI mode, this is the Fourth pair in 1000Base-T |

5.2.4、RGMII PHY #0 #1 #2 #3 (14 X 4 对应6.7)

| Pin | I/O | 定义 |

| n0_rgmii_tx_0 n0_rgmii_tx_1 n0_rgmii_tx_2 n0_rgmii_tx_3 | O | 网口#0 RGMII 发送数据接口 |

| n0_rgmii_rx_0 n0_rgmii_rx_1 n0_rgmii_rx_2 n0_rgmii_rx_3 | I/O | 网口#0 RGMII 发送数据接口 |

| n0_rgmii_txc n0_rgmii_tx_ctl | O | 网口#0 RGMII 发送控制接口 |

| n0_rgmii_rxc n0_rgmii_rx_ctl | I down | 网口#0 RGMII 接收控制接口 |

| n0_rgmii_mdc | O | 网口#0 RGMII MDIO接口, MDIO信号需外部上拉1.5-10Kohm电阻。 |

| n0_rgmii_mdio | I/O |

5.2.5、GPIO (对应6.8)

| Pin | I/O | Description |

| n0_gpio_0 [0:1] | I/O | 网口#0 GPIO 0,可用于复位输出或中断输入 网口#0 GPIO 0,可用于复位输出或中断输入 |

| n1_gpio_0 [0:1] | I/O | 网口#1 GPIO 0,可用于复位输出或中断输入 网口#1 GPIO 0,可用于复位输出或中断输入 |

| n2_gpio_0 [0:1] | I/O | 网口#2 GPIO 0,可用于复位输出或中断输入 网口#2 GPIO 0,可用于复位输出或中断输入 |

| n3_gpio_0 [0:1] | I/O | 网口#3 GPIO 0,可用于复位输出或中断输入网口#3 GPIO 0,可用于复位输出或中断输入 |

| mng_gpio_0 | I/O | CPU GPIO 0,可用于复位输出或中断输入 |

| mng_gpio_1 | I/O | CPU GPIO 1,可用于复位输出或中断输入 |

5.2.6、Management Interface (对应6.9)

管理接口可以作为MII接口,外接PHY使用,也可以作为NCSI接BMC芯片使用。在连接外部mac时,SMBUS mode和NC-SI mode可以同时支持。

| Pin | I/O | Description |

| uart_srx | I down | 片上 CPU UART 接口,用于调试,可访问 CPU内部寄存器信息。 (对应6.2.9) |

| uart_stx | O | |

| mng_ic_clk | IN/OD Up | 片上 CPU I2C 接口时钟信号,该信号在任何状态下都支持,与 pe_aux_pwr_det 无关。 |

| mng_ic_data | 片上 CPU I2C 接口数据信号,该信号在任何状态下都支持,与 pe_aux_pwr_det 无关。 | |

| mng_ic_smbsus_n | I/O Up | 片上 CPU I2C 接口挂起信号 |

| mng_ic_smbalt_n | 片上 CPU I2C 接口输出中断信号 | |

| rmii_ref_clk/ ncsi_ref_clk | I down | NC-SI Reference Clock Input – Synchronous clock reference for receive, transmit and control interface. It is a 50MHz clock +/- 100 ppm. |

| rmii_csr_dv/ ncsi_ tx_en | I down | Transmit Enable |

| rmii_rxd_0/ ncsi_txd_0 | I down | Transmit data signals from BMC to WX1860 |

| rmii_rxd_1/ ncsi_txd_1 | I down | |

| rmii_tx_en/ ncsi_csr_dv | I down | Carrier Sense/Receive Data Valid |

| rmii_txd_0/ ncsi_rxd_0 | O | Received data signals from WX1860 to BMC |

| rmii_txd_1/ ncsi_rxd_1 | ||

| mii_mdc | O | MII MDIO 接口。 |

| mii_md | I/O |

5.2.7、TS1588 Pins

| Pin | I/O | Description |

| n0_ts1588_sdp_[0:3] | I/O | 网口#0 TS1588 GPIO |

| n1_ts1588_sdp_[0:3] | I/O | 网口#1 TS1588 GPIO |

| n2_ts1588_sdp_[0:3] | I/O | 网口#2 TS1588 GPIO |

| n3_ts1588_sdp_[0:3] | I/O | 网口#3 TS1588 GPIO |

5.2.8、PCIe Interface Signals

| Pin | I/O | Description |

| pe_wake_n | OD Up | PCIe WAKE# 信号,低有效,使用WOL功能时需使能此信号。 |

| pxpor_res | I down | 复位信号输入 |

| por_bypass | I down | 片内上电复位控制电路旁路使能,高有效。有效时,片内上电复位控制电路被旁路,片内不再产生上电复位信号,芯片的上电复位信号来自pxpor_res,此时pxpor_res作为低有效信号。 (对应6.4) |

| perst_n | I | PCIe PERST#信号,低有效。 |

| pe_phy_resref | A | PCIe PHY参考电阻,200Ω接地。 |

| pe_ref_clk_p pe_ref_clk_n | A-in | PCIe 100MHz参考时钟,来自PCIe slot |

| pe_tx_p_[0:3] pe_tx_n_[0:3] | A-out | PCIe PHY Gen2x4 差分收发信号 |

| pe_rx_p_[0:3] pe_rx_n_[0:3] | A-in |

5.2.9、SPI Flash Interface Signals (对应6.2.2 & 6.5)

| Pin | I/O | Description |

| spi_clk_div_[0:2] | I down | 用于调试,不支持WOL 时默认配置011。 支持WOL 时采用000。 |

| spi_clk | O | SPI flash 接口信号 |

| spi_cs_n | O | |

| spi_si | I down | |

| spi_so | I |

5.2.10、JTAG (对应6.2.10)

| Pin | I/O | Description |

| TCK | I | JTAG chain clock |

| TDI | I | JTAG chain input |

| TDO | O | JTAG chain output |

| TMS | I | JTAG chain Test mode select |

| TRST_n | I | JTAG Reset (pull-up is recommended on JTAG Reset) |

5.2.11、others

| Pin | I/O | Description |

| G0_RTT G1_RTT G2_RTT G3_RTT | NC | |

| G0_OPIN_PAD G1_OPIN_PAD G2_OPIN_PAD G3_OPIN_PAD | NC |

| Pin Description | 数目(个) |

| Power Supply & Ground | 109 |

| Misc Interface | 26 |

| Internal PHY #0 #1 #2 #3 | 52 |

| RGMII PHY #0 #1 #2 #3 | 56 |

| PCIe Interface | 23 |

| SPI flash Interface | 7 |

| GPIO | 10 |

| Management Interface | 15 |

| TS1588 Pins | 16 |

| JTAG | 5 |

6、硬件设计注意项(★)

6.1、电源设计

6.1.1、电压及电流

6.1.2、EFUSE模块电源说明

6.1.3、电源时序(★)

6.2、模式配置说明(★)

6.3、时钟输入

6.4、复位设计

6.5、flash推荐

| Manufacturer | Model type |

| 兆易创新 | GD25Q80C 系列 |

| microchip | SST25VF080B 系列 |

| Winbond | w25q80dv 系列 |

6.6、WX1860芯片的LED[0:2]引脚输出控制说明

6.7、光口设计PHY推荐、中断引脚说明

6.8、Wake on lan国产平台work around 方案

6.9、WX1860的NCSI连接说明

6.10、SMBUS部分设计说明

6.11、其他

7、硬件实战(★)

7.1、I350

7.2、WX1860

8、layout设计注意事项

PCI_Express

1、串接0.1uF电容尽量靠近金手指放置;

2、差分线对内等长3mil;

3、差分线对间间距3W;

4、过孔尽量不超过2个,TX和RX分别走不同层,走线尽量短一些。

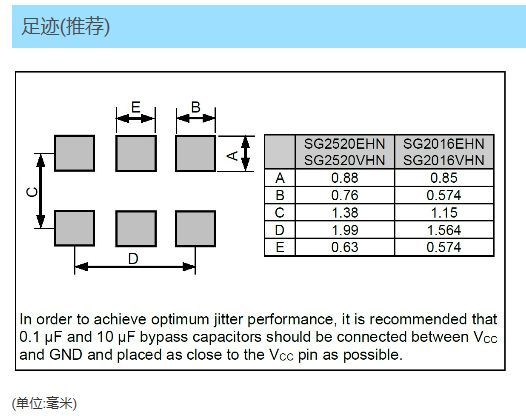

WX1860布线

BGA建议过孔和线宽:0.65mm间距我们采用孔径(内径8mil,外径14mil),走线我们建议3.9mil,用3.5mil 以上的线宽就行。

MDI部分布线建议如下:

1、PHY 距离网络变压器的距离要≥25mm,以便于将PHY和网络变压器有效隔离,减少EMI干扰。

2、差分线上的共模电容用于高频衰减,共模电容靠近网络变压器摆放;

3、网络变压器两侧的差分阻抗都设置为100Ω±10%;

4、网络变压器靠近RJ45连接器摆放;

5、75Ω电阻、0.1uF电容都靠近网络变压器对应引脚;

6、网络变压器下面的地挖空;

7、MDI差分对内误差不超过5mil,4对差分对间误差不超过800mil;差分对间距要大于30mil,过孔尽可能少;

8、MDI信号到变压器和变压器到RJ45的参考地要完整,不要破坏参考地完整性。