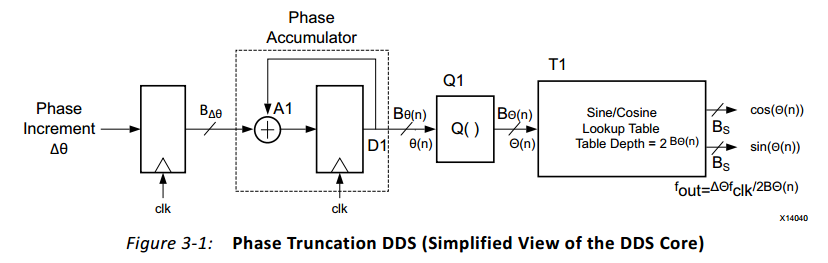

DDS内部结构

实现流程

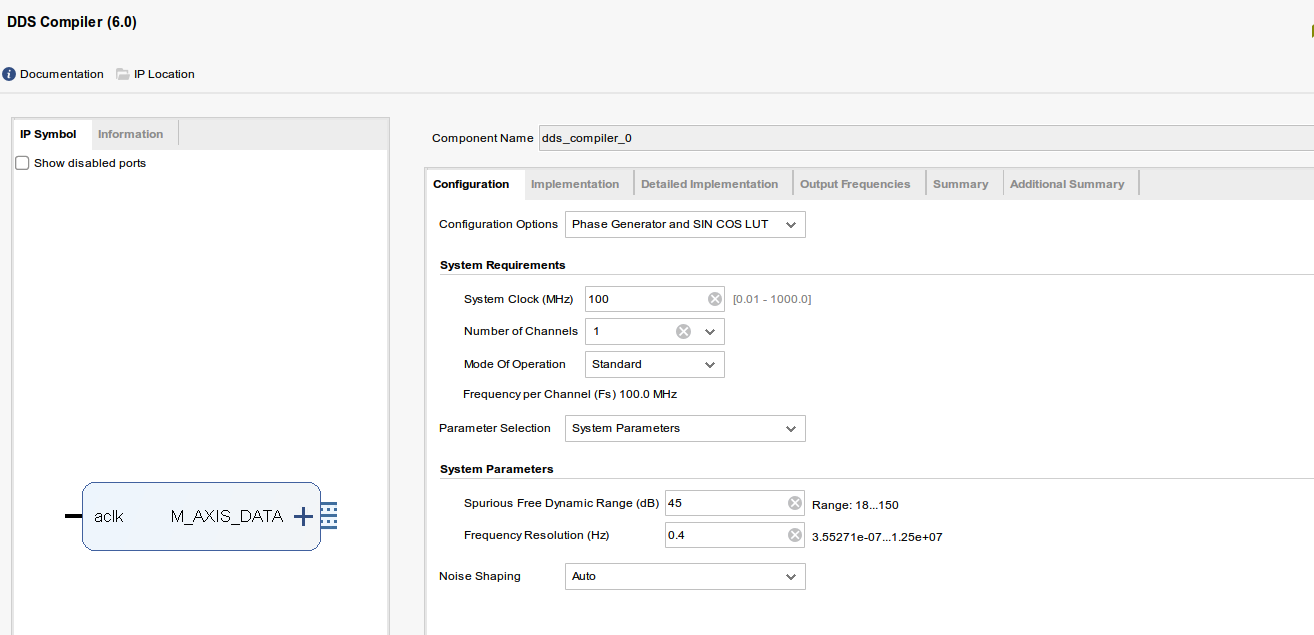

首先新建一个工程,创建bd文件,添加DDS Compiler核,此处不多赘述

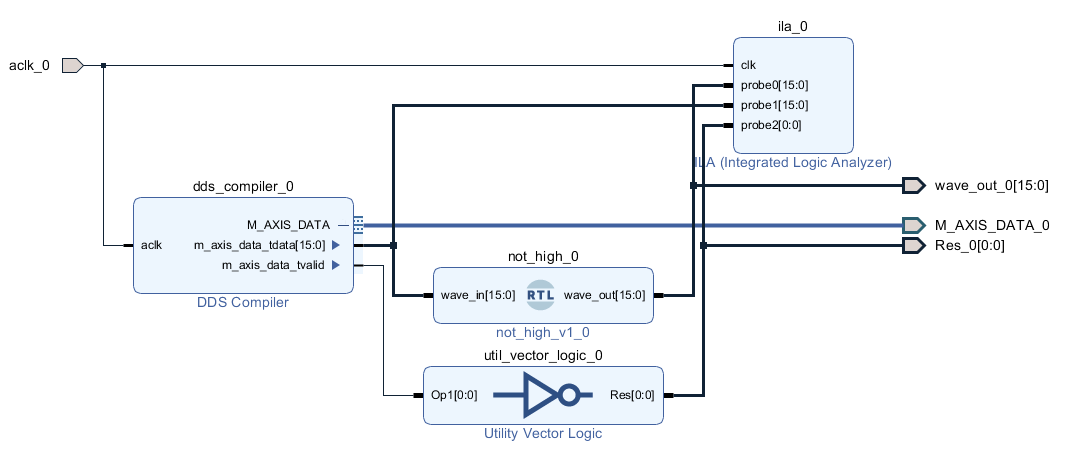

Block Design

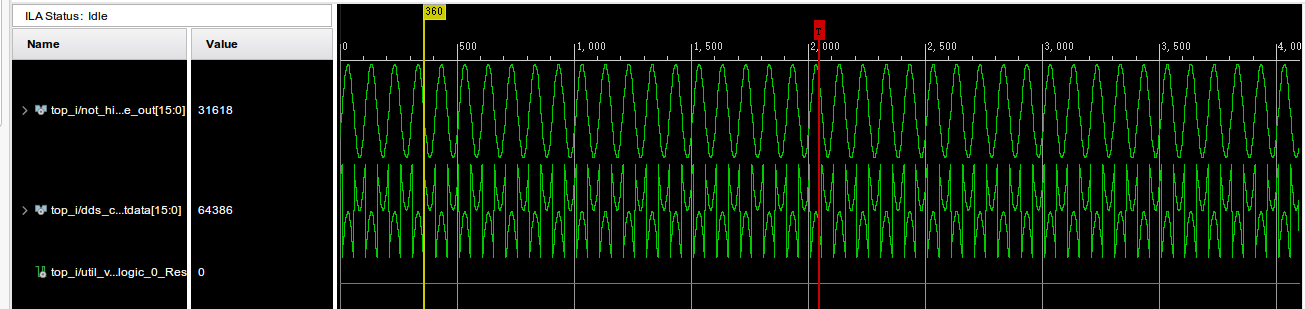

在观测输出的信号时,需要将最高位符号位的信号取反,这样才能输出正弦波,否则输出的波形如下图所示

将tvalid信号取反是因为将这个信号接到了开发板的LED0上,led需要低电平才能点亮,因此将vld信号进行取反

Testbench

bd文件转化成的Verilog文件如下

//Copyright 1986-2018 Xilinx, Inc. All Rights Reserved.

//--------------------------------------------------------------------------------

//Tool Version: Vivado v.2018.3 (win64) Build 2405991 Thu Dec 6 23:38:27 MST 2018

//Date : Tue Apr 23 18:35:43 2024

//Host : MOERJIE_PC running 64-bit major release (build 9200)

//Command : generate_target top_wrapper.bd

//Design : top_wrapper

//Purpose : IP block netlist

//--------------------------------------------------------------------------------

`timescale 1 ps / 1 psmodule top_wrapper(Res_0,aclk_0,wave_out_0);output [0:0]Res_0;input aclk_0;output [15:0]wave_out_0;wire [0:0]Res_0;wire aclk_0;wire [15:0]wave_out_0;top top_i(.Res_0(Res_0),.aclk_0(aclk_0),.wave_out_0(wave_out_0));

endmodule针对顶层模块的输入输出设计如下testbench文件

`timescale 1ns / 1ps

//

// Company:

// Engineer: Sawen Moerjie

//

// Create Date: 2024/04/23 13:51:29

// Design Name:

// Module Name: top_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module top_tb();reg aclk;//wire [15:0] M_AXIS_DATA_0_tdata;wire Res_0;wire [15:0] wave_out;initial beginaclk=1'b0;end always #5 aclk=~aclk;top_wrapper top_wrapper_u0(.aclk_0 (aclk),.Res_0 (Res_0),.wave_out_0 (wave_out));endmoduleTestbench语法

1. 输入信号声明使用reg,输出信号声明使用wire

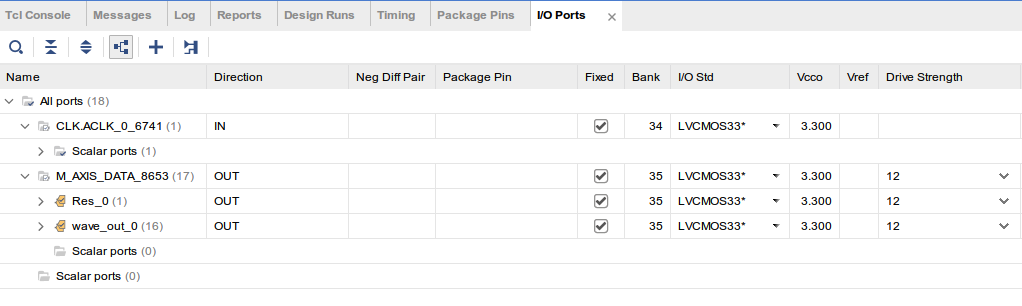

引脚约束

IO电平标准要设置为LVCMOS33,否则无法生成Bitstream文件

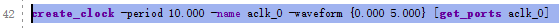

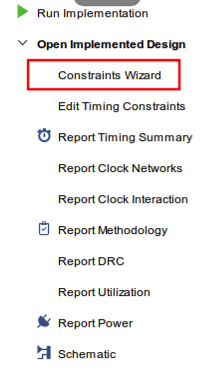

时序约束

添加完成后xdc文件会新增一行