SDRAM(Synchronous Dynamic Random Access Memory) 同步动态随机存储器,同步是指 Memory工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写(from baidu)。

SDRAM的储存是由电容介质充放电实现的,掉电丢失。

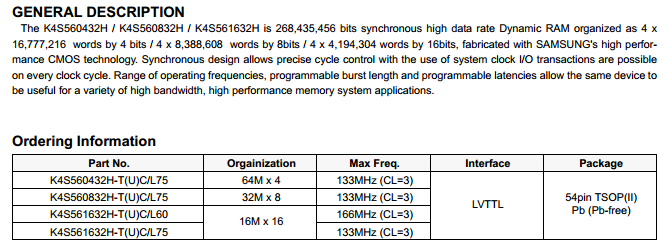

下面我们拿三星的一款SDRAM作为样本详细解析

这块芯片是一块CMOS技术芯片,标准供电电压3.3V

SDRAM芯片的地址都有行列之分,相当于一个表格给定行地址和列地址就能确定其中的某个数据,一块芯片里有几个不同的表格,每个表格称为一个bank

该芯片(大部分SDRAM)中有4个bank

上图中有三种型号*4 *8 *16分别表示输出数据宽度为4bit,8bit,16bit

上图中的引脚作用如下(#代表低电平有效)

CLK 系统时钟 边沿采样,系统时钟必须供给才能让芯片运作

#CS 片选信号 能够屏蔽对芯片的操作,除了CLK,CKE,DQM脚不被影响

CKE 时钟使能信号 当它为0时能够屏蔽系统时钟以此来冻结整个芯片(类似锁存作用)在发送命令一个时钟周期之前就必须将CKE置1

A0~A12 地址 行列地址共用这个信号,行地址占用A0~A12,列地址占用 (x4 : CA0~ CA9,CA11), (x8 : CA0~ CA9), (x16 : CA0~ CA8)

BA0~BA1 bank选择地址 在行地址锁存时间时激活某个bank,在列地址锁存时间时选择bank来读写(后面会说)

#RAS 行地址锁存 当它为0时在时钟边沿时锁存行地址

#CAS 列地址锁存 当它为0时在时钟边沿时锁存列地址

#WE 写使能 使能写,使能行预充电

DQM 数据输入输出屏蔽 使数据输出脚变成高阻态,屏蔽数据输入

DQ0~n 数据输入输出 这些脚同时是数据输入脚也是数据输出脚 (x4 : DQ0~3), (x8 : DQ0~7), (x16 : DQ0~15)

VDD 电源

VSS 地

VDDQ 数据电源 数据电源需要较小的噪声干扰

VSSQ 数据地 同样需要较小的噪声干扰

NC 无连接

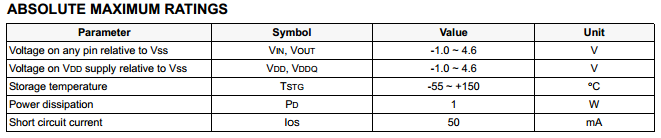

下面是芯片工作环境的相关参数,一般商用SDRAM的标准值应该也差不多

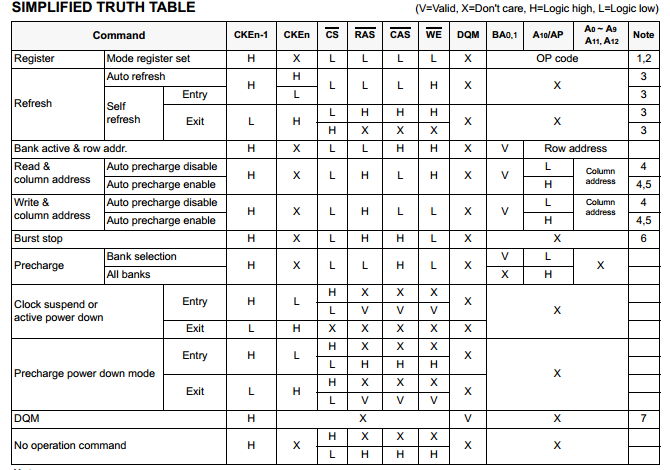

下面我们通过真值表来对使用时序进行分析

H高电平,L低电平,X无影响,V有效的

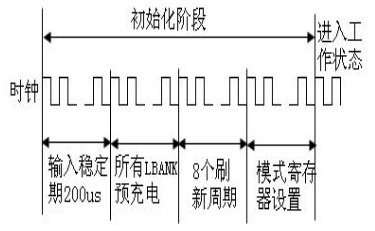

SDRAM的初始化:

当VDD和VDDQ被同时加电后,首先需要维持CLK时钟还有CKE为1,DQM为1,200us的延时(期间空操作,对应No Operation Command),然后就需要一个预充电指令Precharge我们选择所有bank预充电,这个指令的值可以在真值表中看出,然后执行2个以上自动刷新Auto refresh接着就执行Mode register set

SDRAM具有模式寄存器,通过该模式寄存器,可以切换SDRAM的操作模式

Mode register set(模式寄存器设置)相关信息

如果A9在模式寄存器设置周期为1,"Burst Read Single Bit Write(突发读单bit写)"功能将允许,RFU在模式寄存器设置周期应该保持为0

在模式寄存器周期之后芯片就能够正常读写了

先来说下突发的概念

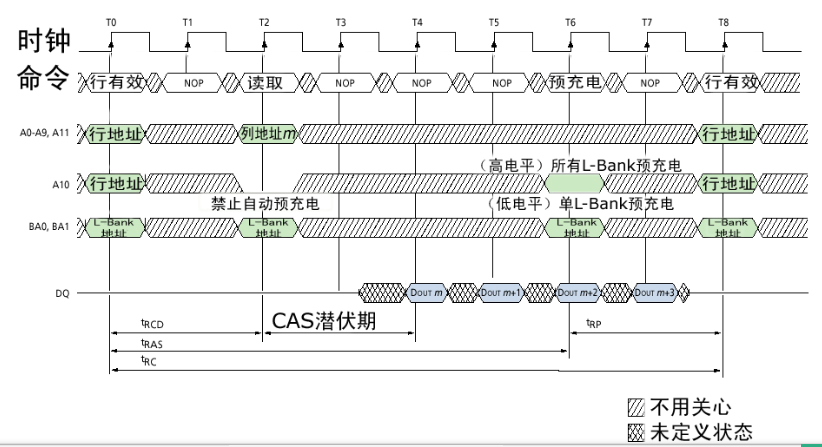

在实际工作中,bank地址与相应的行地址是同时发出的,这个命令叫做“行有效”或“行激活”对应前面图中bank active&row addr。

在此之后将发送列地址寻址命令与具体的操作命令(读还是写),这两个命令也是同时发出的我们叫“读/写”(看真值表)

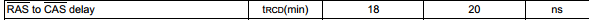

从”行有效“到“读/写”命令发出之间的间隔被定义为tRCD(RAS to CAS Delay),直白地说“行选通周期”,它是SDRAM时序的一个重要参数,需要根据控制芯片频率而定。

tRCD以时钟周期为单位

翻看数据手册,我们可以发现该芯片的tRCD的最小值

接下来,相关的列地址被选中后,将会触发数据传输。数据从储存器到达IO口仍然需要一定时间,该时间被定义为CL(CAS Lantency)

直白地说,列地址脉冲选通潜伏期

CL也是以时钟周期为单位,对于SDRAM,写入是没有潜伏期的

突发(burst)是指在同一行周期中相邻的存储单元连续进行数据传输的方式,连续传输的周期数就是突发长度(Burst Lengths)BL

在进行突发传输时,只要指定起始列地址与突发长度,内存就会依次自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址

这样,除了第一次数据传输需要若干周期(主要是tRCD+CL)外,其后每个数据只需要一个时钟周期就可以获得。

在读取完数据之后为了腾出读出放大器以供同一bank内其他行的寻址并行传输数据,内存芯片要进行预充电工作,如果当前寻址的存储单元是bank1,

行2,列6,接下来的寻址是bank1,行2,列8,则不用预充电,因为读出放大器正在为这一行服务,但如果是bank1,行4,列2,因为不同行,就必须先把行2关闭

从开始关闭现有行工作到可以打开新行的工作之间的时间间隔是tRP(Row Precharge command period)行预充电有效周期,单位也是时钟周期数

预充电:如果在读写完一行后要对同一bank另一行进行寻址,就要将原有效行关闭,准备打开新有效行重新寻址。关闭原有效行,准备打开新行的操作就是预充电。

预充电可以通过命令控制,也可以通过辅助设定让芯片在每次读写操作之后自动执行。在发送预充电命令之后,需要一段时间才能允许发送行有效,这个间隔就是tRP

刷新:SDRAM需要不断刷新来保留数据,刷新操作分为两种,自动刷新Auto Refresh和自刷新Self Refresh,都是一个内部的自动操作。

自动刷新:SDRAM内部有一个行地址生成器,用来自动依次生成行地址,由于刷新是针对一行中的所有储存体进行,所以无需列寻址,所以是列提前于行方式刷新

自刷新:主要用于休眠模式低功耗模式下的数据储存,此时不需要依靠系统时钟工作,而是根据内部时钟进行刷新操作,在SR期间除了SKE之外的所有外部信号都是无效的。

只有重新使能CKE才能退出自刷新模式进入正常状态。

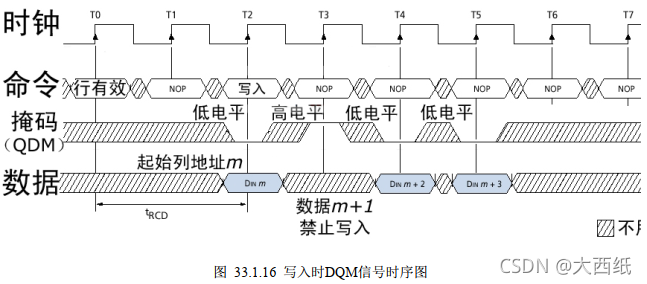

数据掩码(DQM):在讲述读/写操作时,我们谈到了突发长度,如果BL=4,那么也就是说一次传送4*位宽bit数据。但是,如果其中的第二笔数据不需要怎么办,这就用到了该技术

通过DQM,内存可以控制IO端口取消哪些输入或者输出数据。在读取时,被屏蔽的数据仍然会从储存体传出,只是被屏蔽。