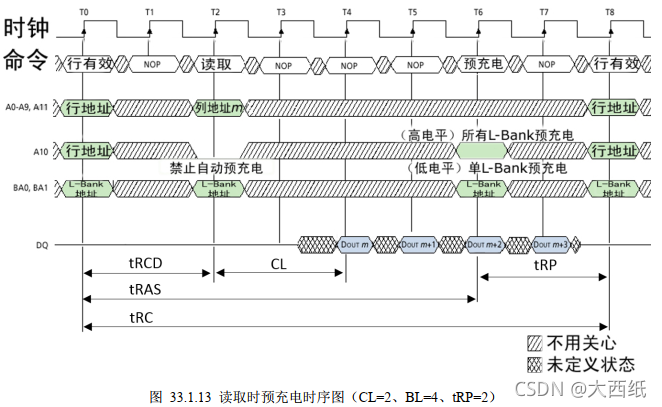

简介、优缺点、历史

1、译为“同步动态随机存取内存”,区别于异步DRAM。SRAM是异步静态存储器。

2、同步(Synchronous):与通常的异步 DRAM 不同, SDRAM 存在一个同步接口,其工作时钟的时钟频率与对应控制器(CPU/FPGA上的读写控制器)的时钟频率相同,并且 SDRAM 内部的命令发送与数据传输均以此时钟为基准,实现指令或数据的同步操作;

动态(Dynamic): SDRAM 需要不断的刷新来保证存储阵列内数据不丢失;

随机(Random):数据在 SDRAM 中并不是按照线性依次存储,而是可以自由指定地址进行数据的读写。

3、SDRAM 使用至今已过数十载,产品更新历经五代, 分别是:第一代 SDR SDRAM,第二代 DDR SDRAM,第三代 DDR2 SDRAM,第四代 DDR3 SDRAM,第五代, DDR4 SDRAM。

4、优点:空间存储量大、读写速度快以及价格相对便宜。

缺点:由于 SDRAM 需要不断刷新来保证数据的可靠性,以及行列地址线分时复用等原因,使其对操作时序的要求较为严格,进而导致控制逻辑较为复杂。

5、容量:4Meg × 16 × 4Banks,“4Meg”表示单个 L-Bank 包含的存储单元的个数,此芯片行地址13 位,即8192 (2^13)行,列地址 9 位,即512(2^9)列,乘积为 4M(8192 ×512 = 4194306)。“16”表示数据位宽,即每个存储单元存储数据的 bit 数。“4BANKS”表示一片 SDRAM 中包含的 L-Bank个数。由此可得 SDRAM 芯片的存储容量为:256MBit。

结构

1、一块存储阵列(行x列),称之为一个逻辑 Bank(Logical Bank,简称L-Bank、 Bank),SDRAM 内部并不是一个全容量的 L-Bank,而是分割为若干个 L-Bank,目前大多为 4 个。若干 L-Bank 的分割,原因有二,一是技术、成本等诸多因素;二是由于SDRAM 的工作原理限制,单一 L-Bank 可能会造成非常严重的寻址冲突,大幅度降低内存效率。

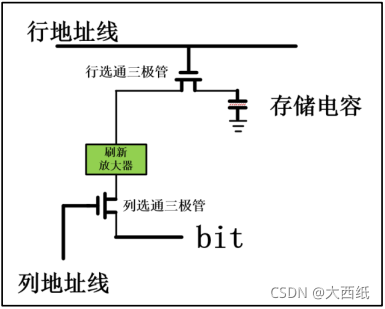

2、SDRAM 的基本存储单位是存储单元,而一个存储单元的容量为若干个 Bit,对于SDRAM 而言就是芯片的位宽,每个 Bit 存放于一个单独的存储体中。存储体是利用电容能够保持电荷以及可充放电的特性制成,主要由行选通三极管、列选通三极管、存储电容以及刷新放大器构成。电容所存储的电荷会随时间慢慢释放,这就需要不断刷新为电容充电,以保证存储数据可靠性。

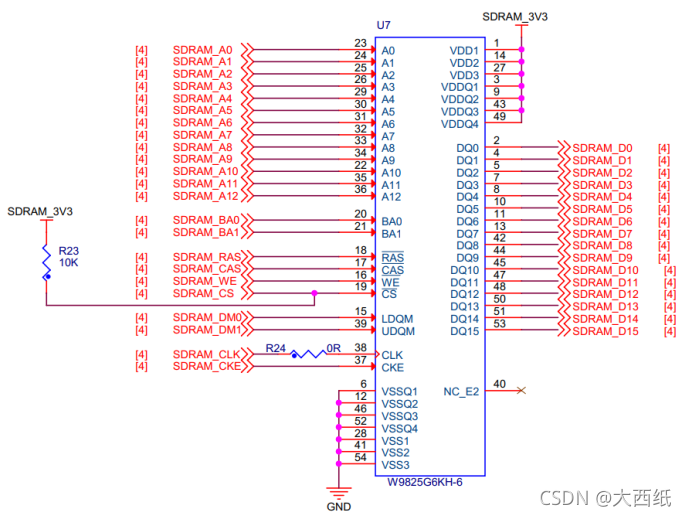

3、 芯片图:SDRAM 型 号 为 W9825G6KH,存 储 容 量 为 256Mbit(32MByte),地址位宽13位, 数据位宽 16 位。

4、原理图:

参数

1、tRCD:打开行地址(激活)是需要一定时间的,即从打开行地址到可以打开列地址进行读写,这之间有一定的时间间隔,这个间隔叫做tRCD(ACTIVE-to-READ or WRITE delay),对于不同型号规格的器件,这个值是不一样的。例如,某个型号的SDRAM器件,对于最大运行频率为133M的器件,该值为15ns。当SDRAM工作在133M时,其一个时钟周期为7.52ns,因此,在实际操作时,必须等待2个时钟周期之后才能选通列地址。而另一款SDRAM器件,其最大运行频率也为133M,但是tRCD.值为20,因此,必须等待3个时钟周期(7.52*3 >20)之后才能打开列地址。

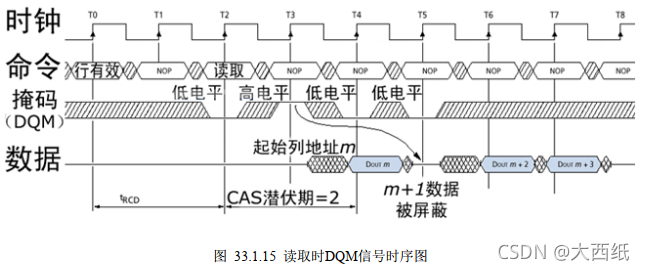

2、CL:只出现在读操作。当列地址被打开后,数据并不是立即出现在最终的数据总线引脚上,而是有若干个时钟的延迟,这个延迟叫做列选通潜伏期(CLCL=CASREADlatency),注意,列选通潜伏期的值针对不同速度等级的器件,其值是不一样的。

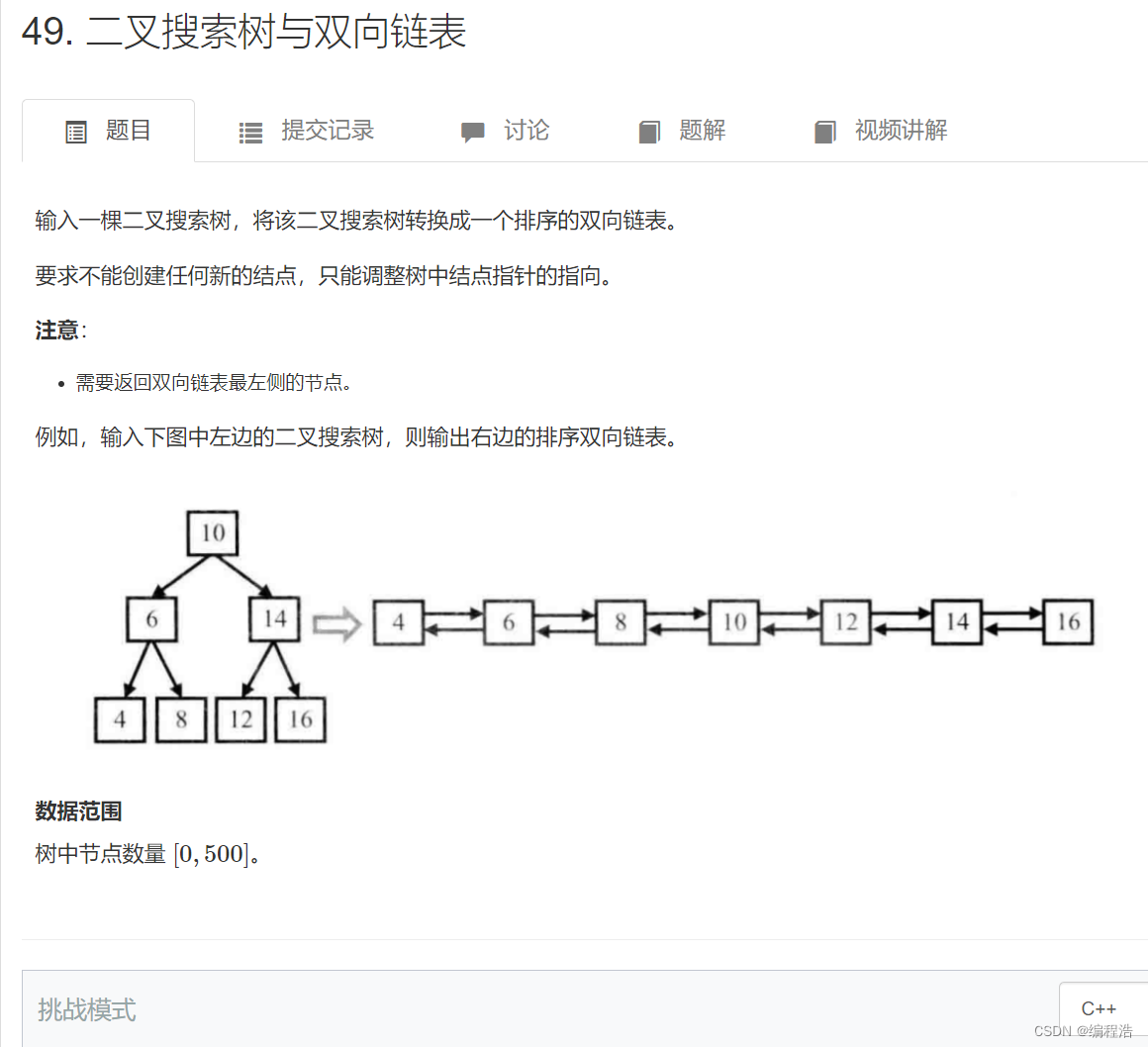

时序

1、初始化:①上电后需要200us的初始暂停,不做任何操作。②200us以后给所有L-Bank预充电。③然后是连续8次刷新操作。④最后设置模式寄存器(MR, Mode Register)。

2、行激活:初始化后,无论是读操作还是写操作, 都要先激活( Active) SDRAM中的一行,使之处于活动状态(又称行有效) 。在此之前还要进行SDRAM芯片的片选和L-Bank的定址,不过它们与行激活可以同时进行。片选CS#为低电平,RAS(行地址选通脉冲)有效,A0-A11为行地址(当CAS列地址选通脉冲时,就是列地址,公用的)。行激活的同时也是相应L-Bank有效,所以行激活也可称为L-Bank有效。

3、列激活:发送列读写命令时必须要与行激活命令有一个tRCD时间间隔。

4、读:上面已经确定了具体的存储单元,在CAS后,要等待CL时间后,数据通道DQ上才有数据。

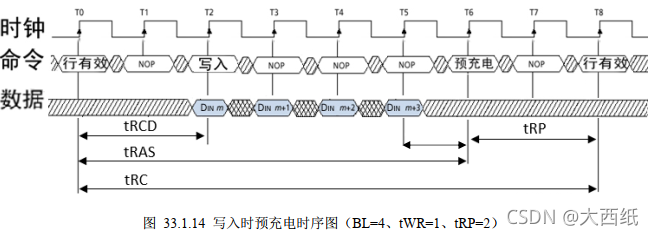

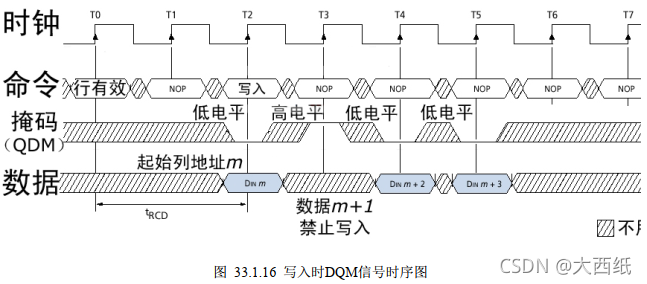

5、写:数据与写指令同时发送。不过,数据并不是即时地写入存储单元,数据的真正写入需要一定的周期。为了保证数据的可靠写入,都会留出足够的写入/校正时间( tWR,Write Recovery Time) ,这个操作也被称作写回( Write Back)。

6、突发长度:突发( Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度( Burst Lengths,简称BL)。如果一次只操作一个单元占用了大量的内存控制资源,在数据进行连续传输时无法输入新的命令,效率很低。BL在设置模式寄存器时设置。读/写操作模式分为“ 突发读/突发写” 和“ 突发读/单一写”。当位宽4bit,数据组成8列,一行即为32bit,在顺序读的突发类型,一次读4个长度时,如果给的地址不是第一个存储单元的地址,而是第二位时,不会读出1234,而是读出顺序为1230。

7、预充电:操作完一行后,要对同一L-Bank的另一行进行寻址,要关闭原来的行,再发新的地址。L-Bank关闭现有工作行,准备打开新行的操作就是预充电( Precharge)。在读写过程中,工作行内的存储体由于“行激活”而使存储电容受到干扰,因此在关闭工作行前需要对本行所有存储体进行重写。预充电实际上就是对工作行中所有存储体进行数据重写,并对行地址进行复位,以准备新行工作的过程。预充电可以通过命令控制,也可以通过辅助设定(让没用到的列地址A10为高电平)让芯片在每次读写操作之后自动进行预充电。

写操作时, 由于每笔数据的真正写入则需要一个足够的周期来保证,这段时间就是写回周期( tWR)。所以预充电不能与写操作同时进行。

8、刷新:预充电是对一个或所有L-Bank中的工作行(处于激活状态的行) 操作,并且是不定期的;而刷新则是有固定的周期,并依次对所有行进行操作,以保留那些久久没经历重写的存储体中的数据。但与所有L-Bank预充电不同的是,这里的行是指所有L-Bank中地址相同的行,而预充电中各L-Bank中的工作行地址并不是一定是相同的。

9、数据掩码:如果BL=4,那么也就是说一次就传送4笔数据。为了屏蔽不需要的数据,人们采用了数据掩码( Data I/O Mask,简称DQM)技术。为了精确屏蔽一个数据总线位宽中的每个字节,每个DQM信号线对应一个字节( 8bit)。因此,对于数据总线为16bit的SDRAM芯片,就需要两个DQM引脚。官方规定,读时,DQM两个时钟周期后生效,写时为一个。

操作

1、CS_N、 RAS_N、 CAS_N、 WE_N 四路控制信号,拼接成{CS_N,RAS_N,CAS_N,WE_N} = 4’bXXXX,组成SDRAM 指令集。其他信号在SDRAM 的操作中,起到辅助作用。例如配置模式寄存器命令时,地址线不同对应存器配置不同模式。