LabVIEWCompactRIO 开发指南37

在第三方模拟器中执行

如果需要验证时序和功能,在将LabVIEW FPGA VI编译到硬件之前,可以与三款第三方仿真器进行交互:MentorGraphicsModelSim(LabVIEW2013及更早版本)、MentorGraphicsQuesta和XilinxISim。可以使用这些模拟器的设计验证和调试功能来调试功能行为和基于时序的错误。要将ISim与LabVIEW FPGA模块配合,应熟悉HDL仿真器和VHDL,这是编写测试台所需的。现在可以选择使用VHDL或LabVIEW为ModelSim编写测试工作台。白皮书Cycle-AccurateCoSimulationwithMentorGraphicsModelSim提供了与ModelSim接口的教程。

在硬件中执行

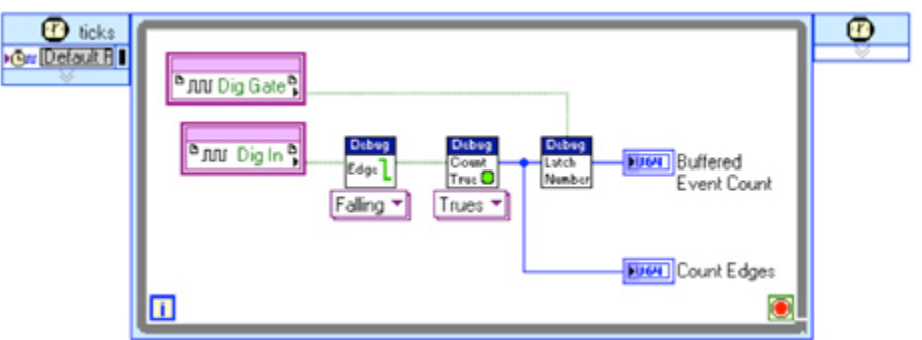

在仿真模式或桌面环境中进行调试可以节省时间,但确实会出现需要将代码编译到FPGA目标,然后实时运行和调试的情况。在这些情况下,必须将其他代码写入应用程序,以测试和验证应用程序的核心功能。调试完成后,通常会删除或禁用此代码。NIFPGA Debug Librar组件提供了一组简单函数,可实时地调试LabVIEW FPGA应用程序。除了执行常见的简单任务外,这些函数还提供模块化编程接口,帮助快速构建高级调试结构。

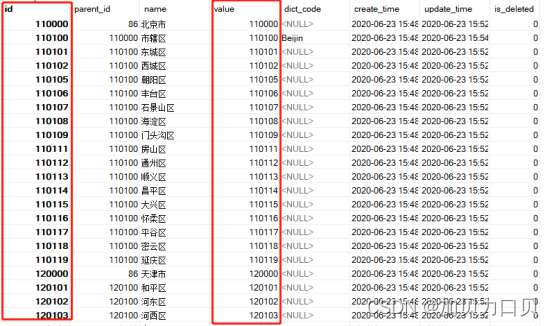

图5.40.高级I/O计数器

优化LabVIEW FPGA代码

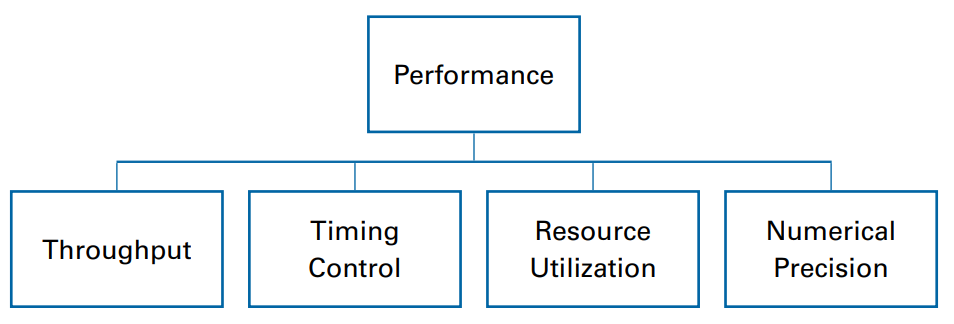

在LabVIEWFPGA中使用常规的LabVIEW编程技术时,会立即获得基于FPGA的方法的优势。有时,可能需要在以下一个或多个相关维度上进一步推动系统:吞吐量、时序、资源和数值精度。

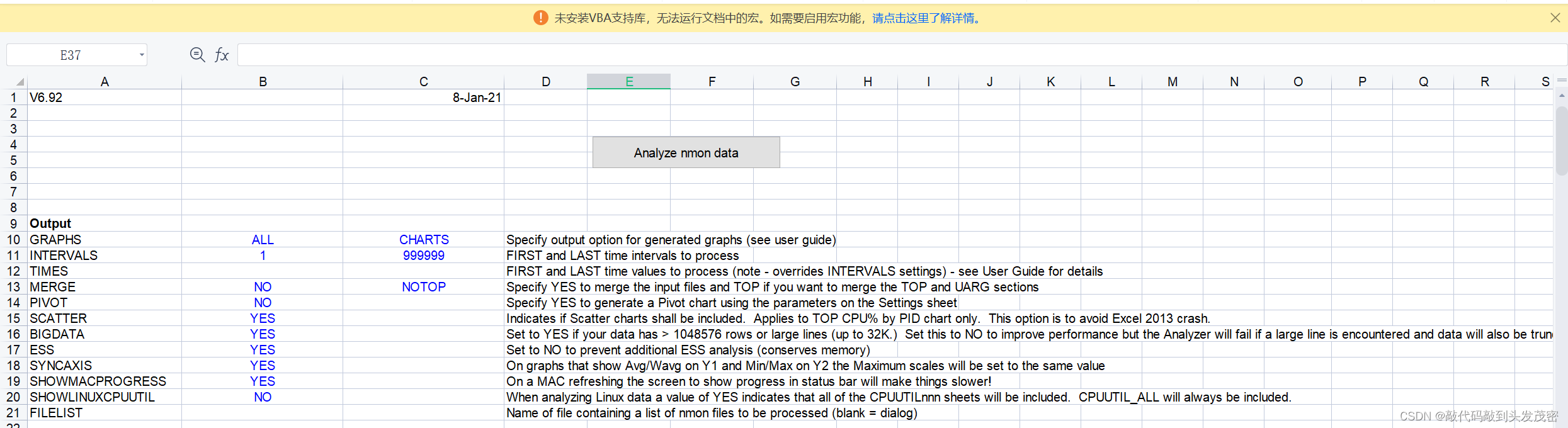

图5.41.借进一步推动系统实现吞吐量、定时控制、资源利用或数值精度

这些维度通常是相互关联的,因此使用其中一个维度改进设计有时会对其他维度产生积极影响,但更多时候是以牺牲它们为代价的。了解这些维度以及它们之间的关系非常重要,因此本指南在下面列出了一些基本定义,并在后面的章节中探讨了相关技术。

吞吐量

吞吐量是DSP和数据处理应用的关键问题。它以每单位时间的工时来衡量。在大多数使用NIRIO硬件的应用中,工作是指处理或传输样本,因此其吞吐量通常以每秒样本或某种等效形式(如字节、像素、图像、帧或每秒操作数)来测量。快速傅里叶变换(FFT)是吞吐量的处理函数的一个示例,其吞吐量可以以FFT、帧或每秒样本数来测量。

High-PerformanceRIO Developer’s Guide更深入地讨论了影响吞吐量的因素,以及一套技术,可帮助在创建LabVIEW FPGA应用程序时实现更高的吞吐量。

定时控制

时序控制是指规定和测量系统中感兴趣事件之间的时间量的能力。使用LabVIEW FPGA时,设计会转换到硬件电路,因此可以创建具有快速时时响应且抖动极小的设计。控制应用通常需要保证系统采样和控制信号更新之间的最大响应时间。此时间量称为延迟。在数字协议应用中,定时规范可以指与正在传输的数据或信号相关的事件之间的目标、最小或最大时间。精确的定时控制对于控制和数字协议应用领域都很重要。

High-PerformanceRIO Developer’s Guide,更深入地讨论了延迟以及一套技术,可帮助在使用LabVIEW FPGA时实现更低或更精确的定时响应。

资源利用率

FPGA的资源数量有限,并且通常比处理器或微控制器在存储和存储器元件方面受到更多的限制。能够将设计融入FPGA是整个开发过程的硬约束。FPGA也由不同类型的资源组成,因此用完一种类型的资源可能会阻止在应用程序中取得进展。

更重要的是,资源利用率会对其他性能维度产生巨大影响,尤其是吞吐量和满足时间限制。请参阅High-PerformanceRIO Developer’s Guide,了解组成FPGA的不同资源的描述,以及如何平衡这些资源以使设计适合并提高性能。

数值精度

数值精度问题围绕着是否有足够的数字或位,以便应用程序可以正常工作。数值精度不足被认为是必须避免和测试的功能问题。用于表示系统变量的位数(包括用于整数的位数、定点数的整数和小数部分以及浮点数的动态范围)可能会对应用程序的性能和资源利用率产生重大影响,因此应考虑这一点。

编译LabVIEW FPGA代码

LabVIEW FPGA编译过程已在本章第一部分中介绍。此过程最多可能需要几个小时,具体取决于设计有多复杂。本节提供了一些减少编译时间和理解编译报告的提示。

减少编译时间

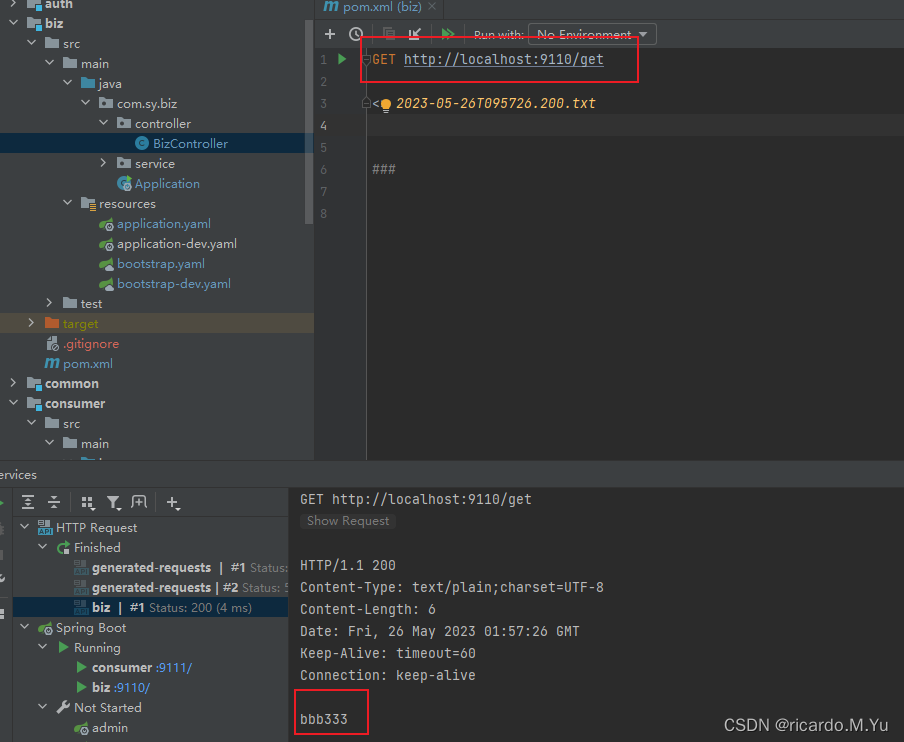

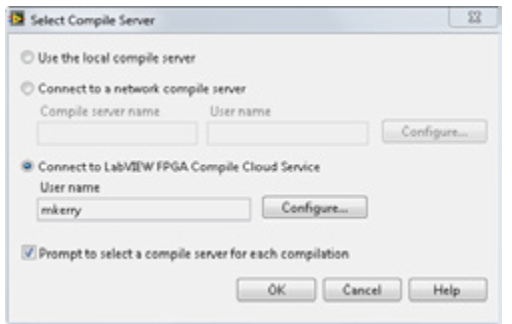

NI提供了多种用于编译LabVIEW FPGA代码的选项。在LabVIEW项目中创建LabVIEW FPGA构建规范时,会在类似图5.42的对话框中看到选项。

图5.42可用于选择编译服务器的几个选项

使用本地编译服务器-默认情况下,可以在本地开发电脑上进行编译。这是编译小型VI的可行解决方案,但如果担心编译时间过长,则应考虑以下其他选项。

连接到网络编译服务器(单个服务器)-可以选择将编译卸载到网络上基于Windows或Linux的单个计算机。事实证明,在Linux机器上编译与在Windows机器上编译时,编译时间会减少。

连接到网络编译服务器(场)—如果在团队中工作,则可以使用LabVIEWFPGA

Compile Farm Toolkit来设置包含多个工作程序的编译场。该工具包可帮助创建现场服务器来管理FPGA编译。可以根据需要连接任意数量的工作计算机,中央服务器软件通过并行编译和队列来管理。如果无法将云技术用于项目,这是减少编译时间的有效方法。

连接LabVIEW FPGA编译云服务—此服务可帮助使用最新的专用高RAM高端计算机在Linux上编译FPGA VI。根据LabVIEW FPGA VI的大小,可能会注意到,与在Windows桌面上编译相比,编译时间大大缩短。在云中编译还增加了并行编译许多VI的能力。

阅读编译报告

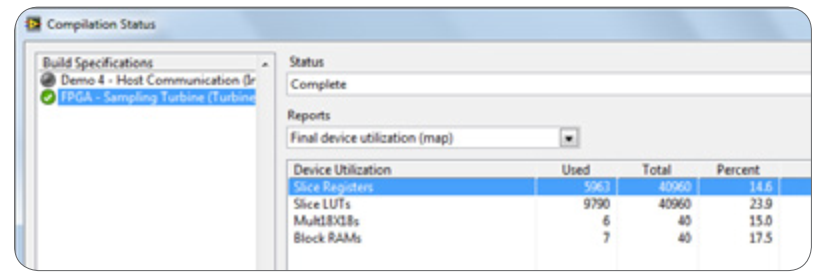

编译FPGA VI后,LabVIEW显示一个编译报告,其中包含有关应用程序整体大小和速度的信息。此信息可以帮助决定如何在必要时优化代码。

请注意,编译器算法不是确定性的,即使不更改VI或编译器设置,也可能从一次编译到下一次编译获得不同的结果。如果编译失败,可以更改编译器设置,方法是右键单击LabVIEW项目中的构建规范,然后从上下文菜单中选择属性。在“属性”页面中,选择Xilinx Options.。

VI大小

成功编译对话框中显示的最终设备利用率(映射)报告提供有关使用的切片寄存器、切片查找表和乘法器数量以及使用的块RAM量的信息。建议的最佳实践是将最终应用中的整体FPGA使用率保持在90%以下。如果将来升级软件并需要重新编译VI,可能会发现不同版本的Xilinx编译工具链或多或少地使用结构。在这种情况下,需要一些额外的空间来使用。

图5.43.最终设备利用率报告

VI速度

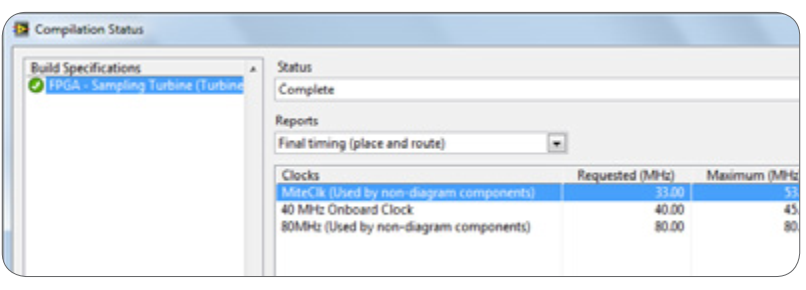

“成功编译报告”对话框还包含有关应用程序时钟速率的信息。

■请求—显示已编译的FPGA VI运行的时钟速率。默认设置为40MHz。

■最大值—显示FPGA VI的理论最大编译速率。

图5.44.最终时间报告

如果最大速率慢于请求的速率,则会产生错误,编译过程将停止。必须将应用程序修改为最大速率等于或大于请求的速率。使用SCTL时的一个常见问题是请求的速率超过理论最大值。

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。