目录

一、前言

二、GATED_CLOCK

2.1 属性说明

2.2 工程代码

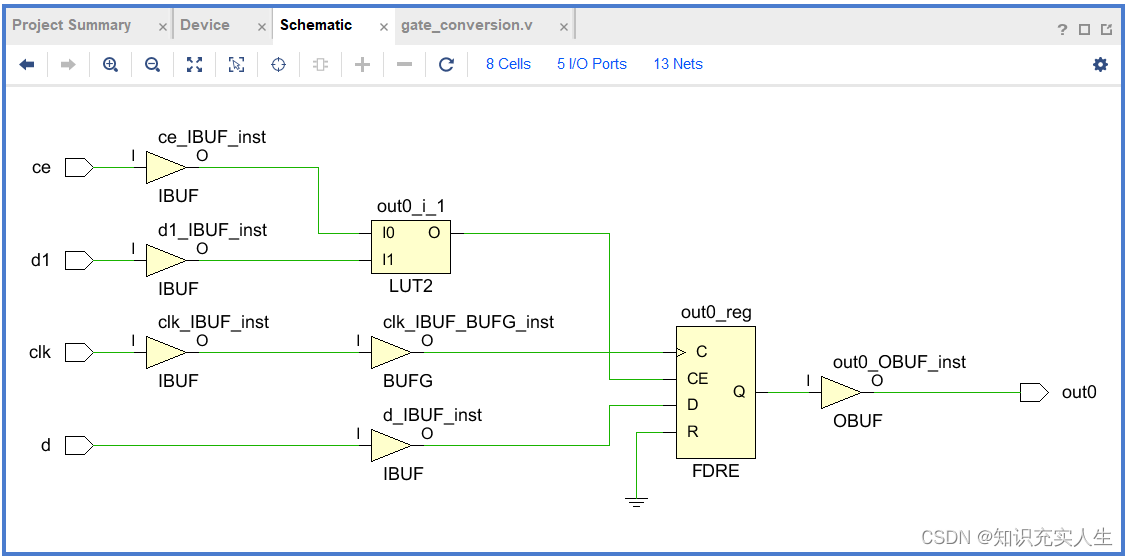

2.3 综合结果

一、前言

在工程设计中,时钟信号通常来源于专用的时钟单元,如MMCM和PLL等。但也存在来自逻辑单元的信号作为时钟,这种时钟信号为门控时钟。门控时钟可以降低时钟网络的动态功耗,但同时也因为由组合逻辑生成,容易产生毛刺。针对门控时钟,综合工具有专门的配置项-gated_clock_conversion和属性gated_clock,启用后会将门控时钟进行转换。

二、GATED_CLOCK

2.1 属性说明

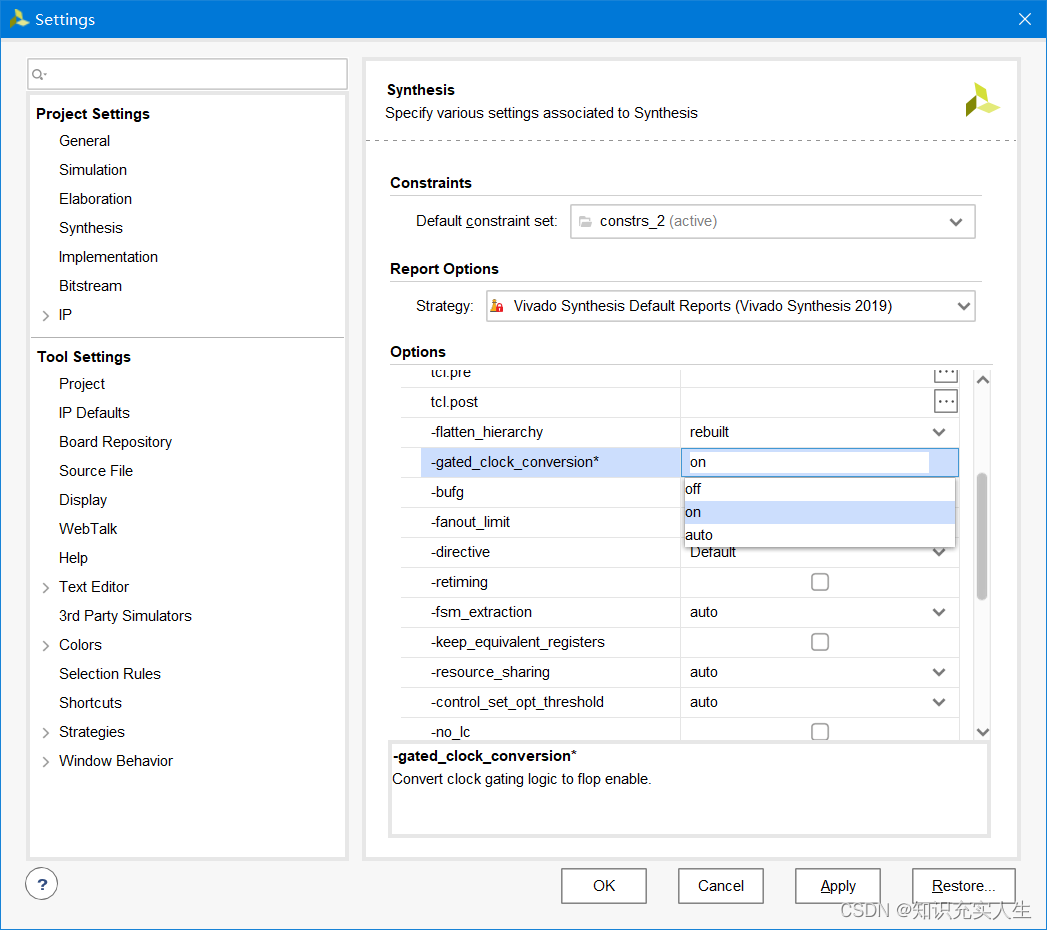

门控时钟转换的配置,需先在Vivado中“Tools->Settings->Project Settings->Synthesis” 进行-gated_clock_conversion进行设置,可设置为off,on,auto,配置界面如下图。

off:禁止门控时钟的转换

on:设置为on时并且RTL代码中时钟信号有gated_clock属性时,门控时钟将会进行转换

auto:属于下面两种情况之一将存在门控时钟转换

1、gated_clock属性设置为YES

2、综合工具检测到组合逻辑并且存在有效的时钟约束时,将会由综合工具决定是否转换

RTL中设置GATED_CLOCK属性 gated_clock可设为yes或no

(* gated_clock="yes"*) input clk;

2.2 工程代码

设计为一个触发的时钟信号来自于两个输入信号进行或运算,

module gate_conversion (d,d1,ce,clk,out0 );

input d,ce;

input d1;

(* gated_clock = "true" *)input clk;

assign clk_conversion=clk|d1;

output out0;

reg out0;

always@(posedge clk_conversion)

if(ce)out0<=d;

endmodule2.3 综合结果

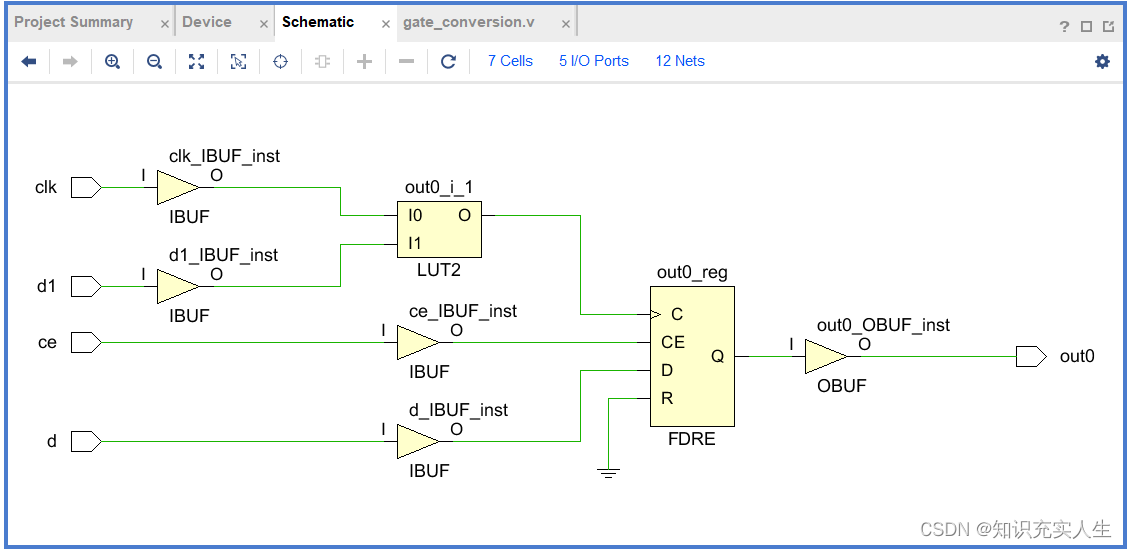

GATED_CLOCK设置为no,未启用门控时钟转换时,FDRE的时钟信号来自LUT2

GATED_CLOCK设置为yes,启用门控时钟转换,clk直接连接到FDRE的C端口, 即信号clk和ce进行了交换