涉及延迟参数

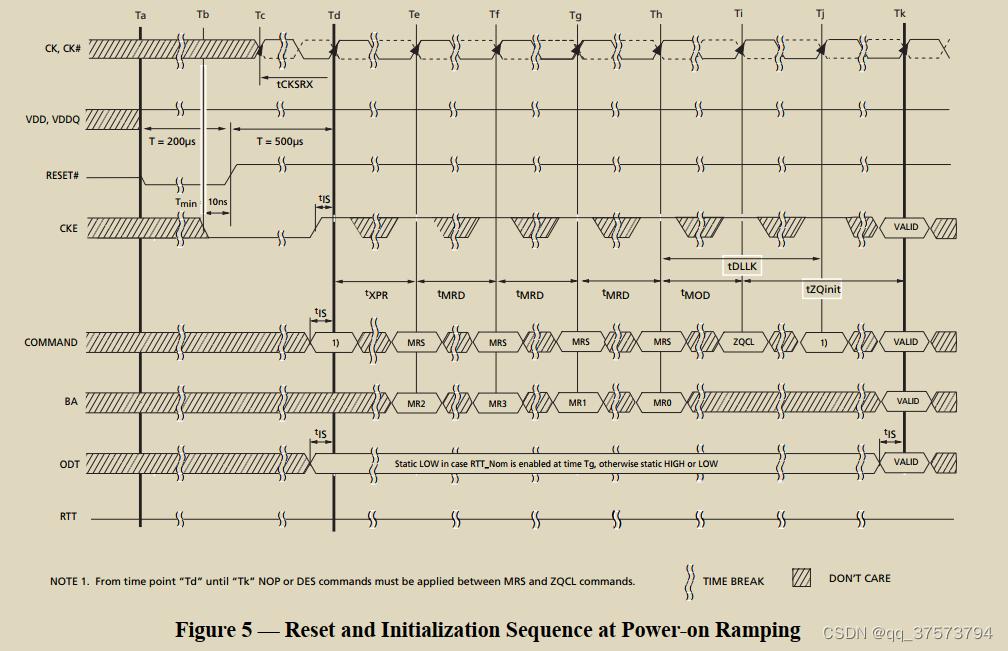

PowerOn

-

RESET# 在电源稳定状态下,保持至少200us

-

在RESET# 解复位之前,CKE需要拉低至少 10ns RESET#

-

解复位之后,需要CKE继续拉低 500us CKE有效之前,CK需要稳定至少 max(10ns, 5*clk);同时在CKE有效之前,需要发送一个NOP或者Deselect命令; CKE一旦拉高,就需要持续到initial sequence完全结束

-

在RESET# 复位状态下,以及解复位后,CKE有效之前, ODT需要维持 Z 状态; 在完全初始化之前 ODT也会保持在一个静态值

-

CKE有效之后,等待至少 tXPR=max (tXS ; 5 x tCK)

-

load MR2寄存器 (BA 010)

-

load MR3寄存器 (BA 011)

-

load MR1寄存器 (BA 001 A[0] = 0)

-

load MR0寄存器 (BA000 A[8] = 1)

-

发起ZQCL命令,进行ZQ长校准 等待 t DLLK & t ZQinit

都完成之后,可以正常进行DDR访问

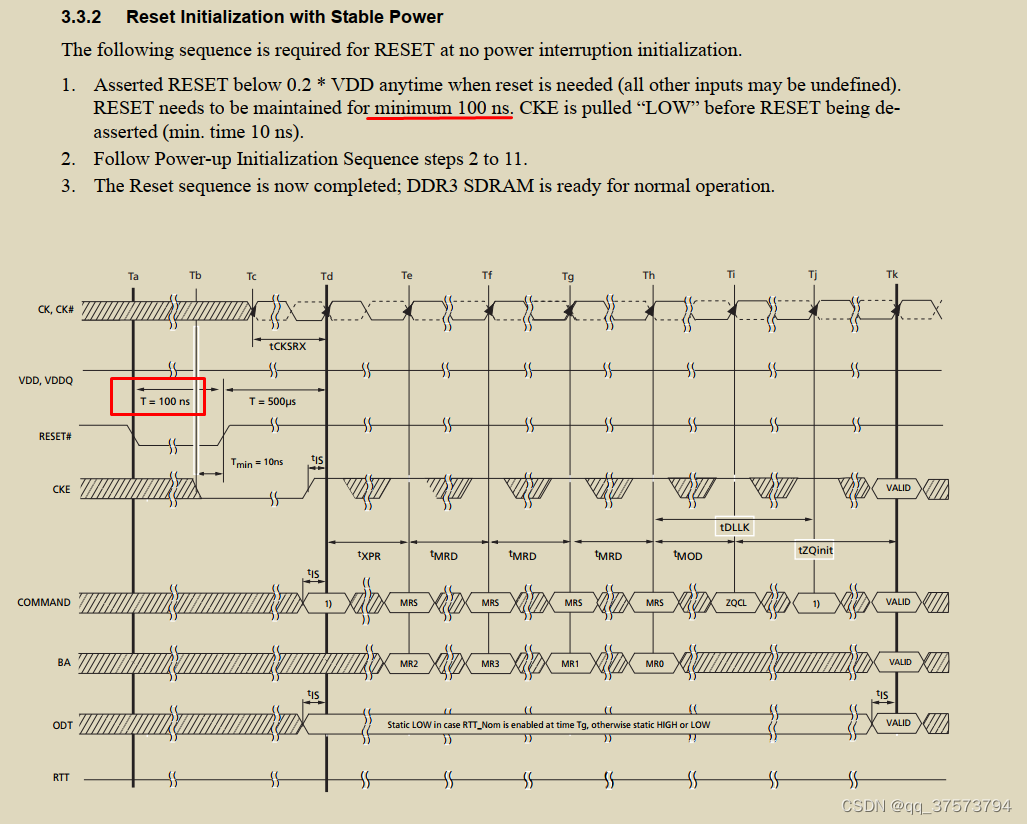

Reset

相对于power up的sequence上,Reset# 拉低时间上有区别,其余保持一致