FPGA实现DDRIP核配置(Memory Interface Solutions)

DDR读写控制分三个文章来写,一部分写DDR的IP核配置,一部分写DDR的读写基本的过程和仿真,最后写读写控制的实现和需要注意的问题。

同步动态随机存取内存(synchronous dynamic random-access memory,简称SDRAM)是有一个同步接口的动态随机存取内存(DRAM)。简单粗暴点说这个东西就是存储数据的。数据的读写速率对系统性能有很大的影响。在使用FPGA的过程中DDR是避免不开的一个高速数据存储介质。如何高速使用DDR是一块很大的内容,这里主要说MIG的IP配置。会根据配置选项讲讲SDRAM的使用原理。其实最好把你选用的DDR数据手册读懂就会特别的好使用SDRAM了。这里的IP配置主要是根据Xilinx官方文档UI806来配置的。

1、首先要申请一个DDR的IP核,在Xilinx的IP中是内存解决方案(Memory

Interface Solutions)这个IP。这个是默认选项,其中Component是用户自己定义的模块的名字。

Number of controller 这个是你控制多少DDR模块,这里一般选择一个模块。(这个和DDR芯片数量没有直接关系,有时候用户选择2片DDR级联,但是实际上还是属于一个DDR模块)

2、这个选项栏是选择兼容相同封装的其他型号FPGA芯片,默认是不兼容。

3、 这个选项栏的选择SDRAM类型,这里需要根据硬件类型来确定选项。

4、这个选项卡比较重要。

Frequency是DDR工作的主频率。也是这个IP核工作的频率,这个频率的设定要根据芯片支持的频率来设定。

Memory type也要根据你的SDRAM类型来选则,根据所选内存的不同而选用不同内存组件和模块分为组件、UDIMM、SODIMM和RDIMM。Virtex-5fpga

ddr2sdram控制器仅支持双列DIMM的深度设计。

Memory Part芯片型号。此功能有助于为设计选择内存部件。可以从现有列表中进行选择,也可以创建新零件。

Data Width数据宽度。数据宽度值可以根据前面选择的存储器类型在这里选择。该列表显示所选零件的所有支持数据宽度。选择其中一个。这些值通常是单个设备数据宽度的倍数。在某些情况下,宽度可能不是精确的倍数。例如,虽然16位是x16组件的默认数据宽度,但8位也是有效值。

Memory Depth记忆深度。DDR2 SDRAM Virtex-4 FPGA控制器采用直接时钟捕获方法,支持1到4个内存深度。DDR2 SDRAM Virtex-5 FPGA控制器仅支持双列DIMM的内存深度为2。深部设计支持的最大频率小于或等于150 MHz。对于其他设计,此选项不可用。

ECC代表纠错码。此功能允许生成ECC和代码。此部分基于选定的数据宽度启用。此选项仅适用于DDR2 SDRAM

Virtex-4和Virtex-5 FPGA设计。

Data Mask数据掩码。标记此数据掩码复选框时,将分配数据掩码管脚。如果未选中此数据掩码复选框,则不会分配数据掩码管脚,这会提高管脚效率。对于不支持数据掩码的内存部件,此选项已禁用且无法更改。同样,对于启用ECC的设计,此选项也被禁用。此选项仅适用于DDR2和DDR SDRAM。

5、这部分是设置读写突发长度、突发类型、预充电时间和IO的阻抗匹配。

5、这部分是设置读写突发长度、突发类型、预充电时间和IO的阻抗匹配。

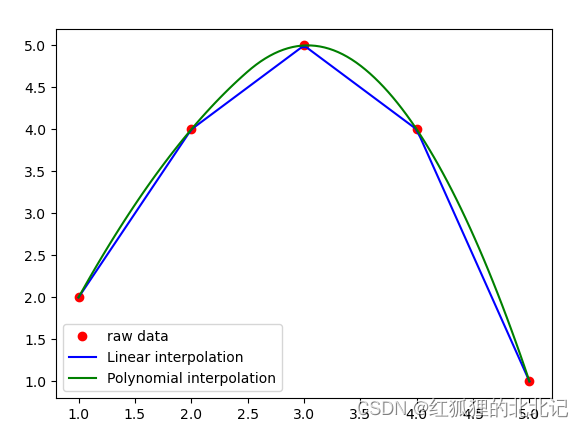

下面这个图就能很好的说明突发长度、突发类型和预充电时间的关系。突发类型分为Sequential 顺序突发和 Interleaved交错突发。突发长度是根据芯片来设置,一般是1、2、4、8突发,芯片得到读出命令到数据实际输出的时间就是预充电时间,就是下图中的CAS。

6、这部分主要是选择IP核的时钟源核时钟方式。可以使用由主时钟的PPL产生的时钟也可以使用DCM来产生时钟,也可以使用外部差分时钟输入来作为IP核的时钟。这几种方式通过实际的验证发现对最终数据的读写都没有影响,但是使用外部差分时钟需要注意内外时钟不同源导致的时钟域的变化问题(内外时钟不一致如果不进行处理的话容易造成数据的读写错误)。

7、这部分就默认设置就行。

8、IO口的选择和配置。这里要根据原理图来进行连接。我在用6SLX45芯片时的原理图连接对应关系如下图

在原理图设计时应该严格按照FPGA芯片推荐设计设置,然后根据具体选择的BANK来选择引脚IO配置。

也可以通过直接填写每个IO口来完成。

9、这部分的前面配置信息的一个总览,这部分需要仔细查看配置是否和芯片型号一致,如果不一致可以返回去更改。

10、接下来一致点next即可。

DDR的IP核配置相对简单,通过上面的配置即可生成一个完整的DDR控制器的例程。