一.背景介绍

FPGA开发过程中,往往有许多重复性繁琐的事情要处理,这时候直接使用HDL编程实现,会很浪费资源;而且有些工作是不需要并行执行,这时候NIOS II 内核就提供了很好的解决方案。在ARM+FPGA或者DSP+FPGA的嵌入式应用领域下,当用户既要实现强大的CPU来完成大量工作;又需要利用FPGA的超高速短延时实现并行设计的情况。如果用户对CPU的处理速度要求不那么高,而且希望控制成本在较低的范围。这个时候也是使用NIOS II 软内核的绝佳时机。

特此说明:本案例使用的quartus软件版本是 V13.14 Bit32位软件。

参考路径: https://blog.csdn.net/tq384998430/article/details/84953257

二.工具介绍

- Quartus ii 工具 :

- NIOS IP核添加工具 : Qsys 在quartus中的打开方式: 菜单 Tools > Qsys

3.NIOS 编程工具:NIOS II Software Build Tools for Eclipse (简称Eclipse) 在quartus中打开方式:菜单Tools > NIOS II Software Build Tools for Eclipse

三.关键过程步骤

- Qsys 内核添加工作。

- Quartus 工程编辑生产工作。

- Eclipse 编码(类似与DSP编码环境)。

四. Qsys内核添加配置

- 进入Qsys

在quartus软件中,工具栏快捷进入,如下;

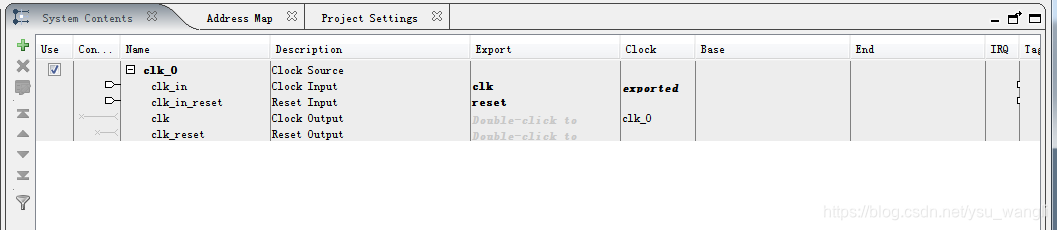

2.进入软件后首先看到自动生产的时钟模块

3.在Library库中搜素添加其他工具模块

首先添加:时钟、CPU、ROM、RAM、JTAG_UART、SYS ID、PIO模块;如下面图片所示。

然后配置各个模块,如下面所述。

1)配置时钟:双击 Clk_0 模块进行设置

2)定制NIOS II :NIOS II一共三款类型,我选择了NIOS II/e,这是最小体积但是性能最差的一款处理器,因为我的开发板是Cyclone II的EC2C5T144C8,内部资源比较有限,如果选择NIOS II/f的话会导致内部资源不够用。下面还有Reset Vector和Exception Vector没有配置,因为现在还配置不了,这些向量是跟程序运行地址相关的,但是还没有添加系统存储器。

2)定制NIOS II :NIOS II一共三款类型,我选择了NIOS II/e,这是最小体积但是性能最差的一款处理器,因为我的开发板是Cyclone II的EC2C5T144C8,内部资源比较有限,如果选择NIOS II/f的话会导致内部资源不够用。下面还有Reset Vector和Exception Vector没有配置,因为现在还配置不了,这些向量是跟程序运行地址相关的,但是还没有添加系统存储器。

3)片上RAM和ROM配置:类型、数据宽度和数据深度

4)JTAG-UART配置:默认即可

5)SYS-ID配置:默认即可

5)SYS-ID配置:默认即可

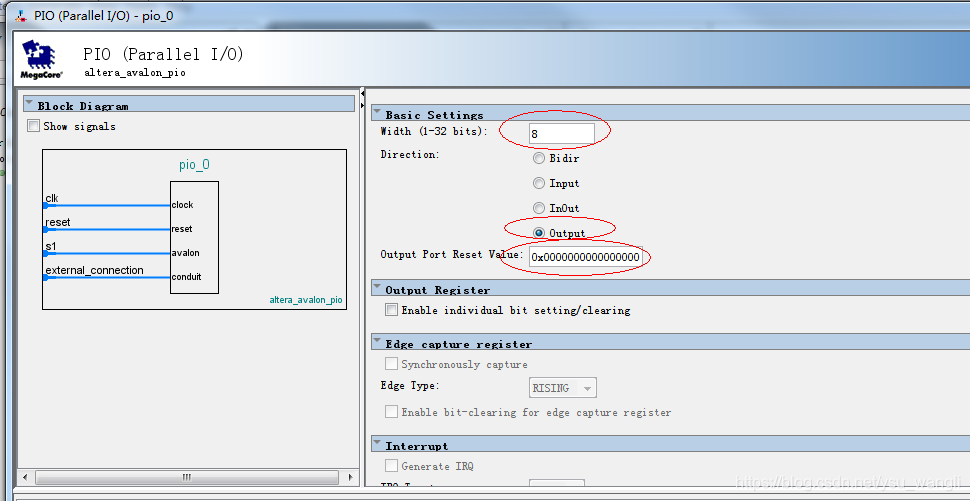

6)PIO模块配置:IO宽度即对应FPGA引脚个数,输入输出类型,和复位时引脚状态。

6)PIO模块配置:IO宽度即对应FPGA引脚个数,输入输出类型,和复位时引脚状态。

7)EPCS读写模块:该模块是第二期开发配置(上述配置结果,系统程序只能在片上的ROM运行),实现NIOS II 初始化从片外 EPCS FLASH芯片读程序。建议,初次学习NIOS,这步骤先不用。

4. 模块间连接;参考下面连接图

操作方式:鼠标放在执行模块的信号上右键, *** Connections > 列表点击连接。PS:复位信号与JTAG仿真复位信号都要连接,便于JTAG在线单步调试过程实现。

5. HDL代码模块生成;操作方式:菜单栏 > Generate > Generate

菜单栏 > Generate > HDL Example 里面Copy代码,用途是实现NIOS II 内核接口使用。

五. Quartus 工程配置

未完待续…