目录

学习目标

学习内容

1.门的类型

2.门延迟

学习时间

学习小结

学习目标

学习Verilog 提供的门级原语

理解门的实例引用、门的符号以及andor,bufnot类型的门的真值表

学习如何根据电路的逻辑图来生成verilog描述

讲述门级设计中的上升、下降和关断延迟

解释门级设计中的最小、最大和典型延迟

学习内容

提示:这里可以添加要学的内容

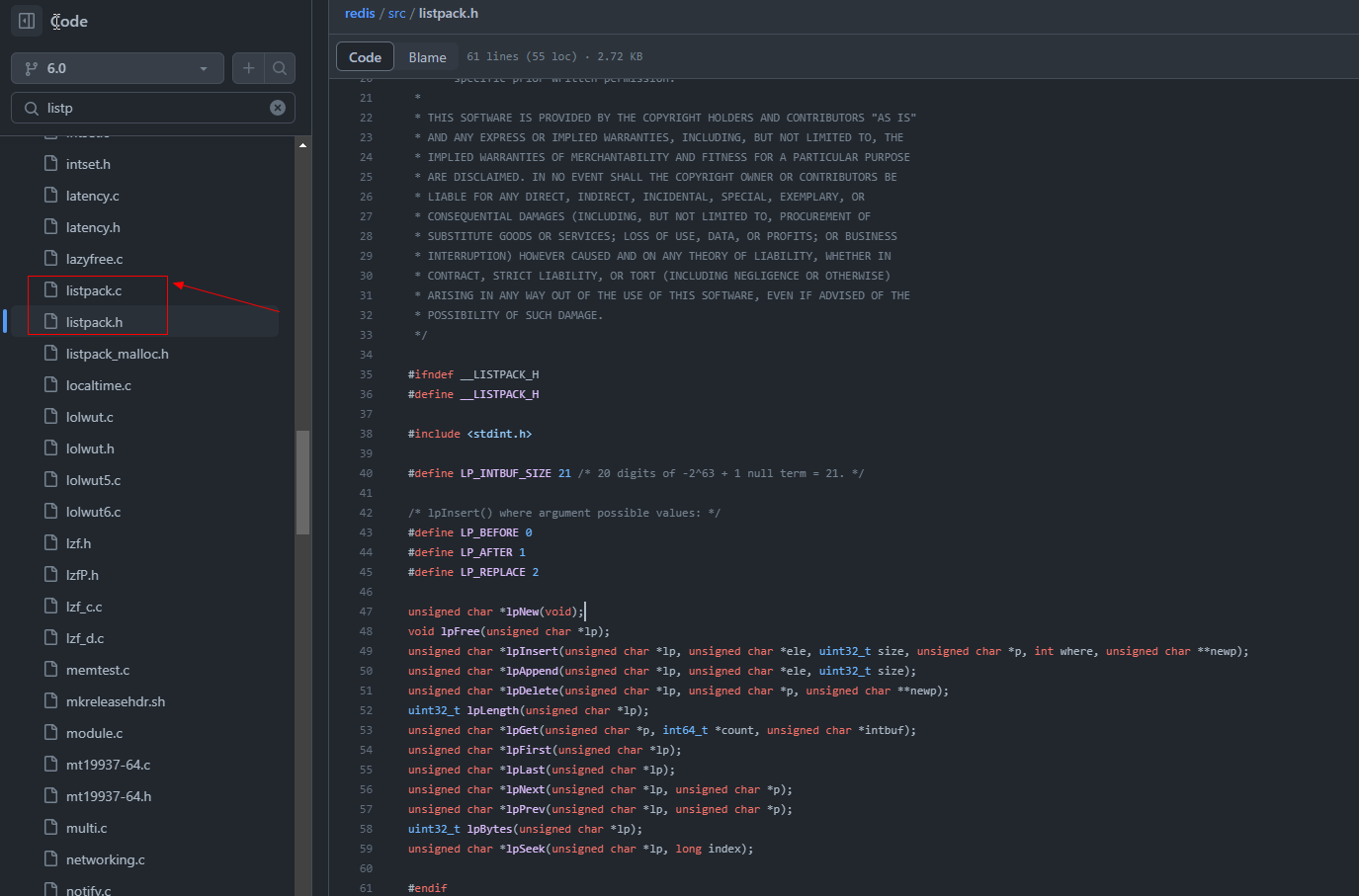

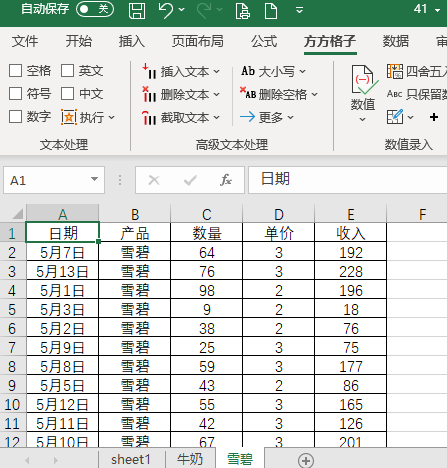

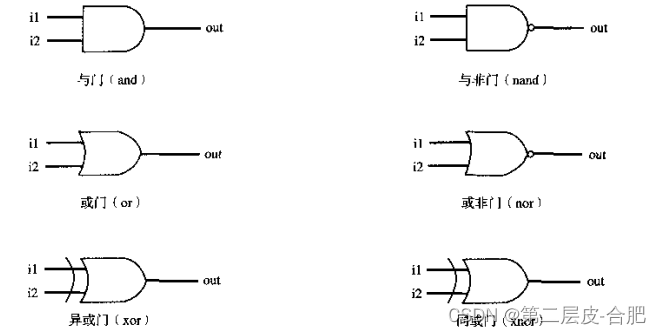

1.门的类型

逻辑电路可以使用逻辑门来设计。Verilog语言通过提供预定义的逻辑门原语来支持用户使用逻辑门设计电路。调用(实例引用)这些门级原语与调用(实例引用)自己定义的模块相同,两者的区别仅仅在于门级原语是预定义的,可以直接使用而无需声明。基本的逻辑门分为两类:( 1)与/或门类( and/or );(2)缓冲器/非门类( bufnot )。我们可以使用它们来设计任何逻辑电路。

在Verilog语言中,我们可以调用(实例引用)这些逻辑门来构造逻辑电路。下面的例子说明了如何编写门实例引用的模块。在中、所有门实例的输出端口( out)都被连接到OUT,两个输入端口(il和i2)则被连接到N1和IN2。注意,在门级原语实例引用的时候,我们可以不指定具体实例的名字,这一点为设计师编写需要实例引用几百个门的模块提供了方便。

2.门延迟

迄今为止,我们所描述的电路都是无延迟的(即零延迟)。然而,在实际的电路中,任何一个逻辑门都具有延迟。Verilog 允许用户通过门延迟来说明逻辑电路中的延迟;此外、用户还可以指定端到端的延迟,这部分内容将在后续中进行讨论。 (迄今为止,我们所描述的电路都是无延迟的(即零延迟)。然而,在实际的电路中,任何一个逻辑门都具有延迟.Verilog允许用户通过门延迟来说明逻辑电路中的延迟;此外、用户还可以指定端到端的延迟,这部分内容将在后面中进行讨论.

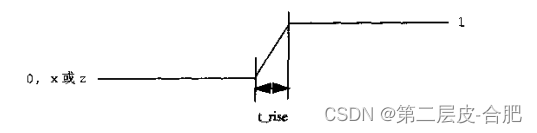

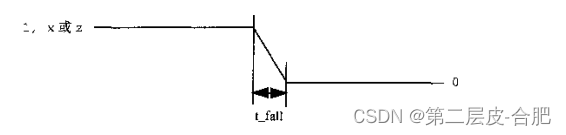

上升延迟:

下降延迟

关断延迟:是指门的输出从0,1、x变化为高阻抗z所需的时间

另外,如果值变化到不确定值x,则所需的时间可以看成是以上三种延迟值中最小的那个:在Verilog 中,用户可以使用三种不同的方法来说明门的延迟。如果用户只指定了一个延迟值,那么对所有类型的延迟都使用这个延迟值;如果用户指定了两个延迟值,则它们分别代表上:升延迟和下降延迟,两者中的小者为关断延迟;如果用户指定了.三个延迟值,则它们分别代表上升延迟.下降延迟和关断延迟。如果未指定延迟值,那么默认延迟值为0。

在Verilog中,用户除可以指定上面所述的三种类型的延迟以外,对每种类型的延迟还可以指定其最小值、最大值和典型值。用户可以在仿真-开始时就决定具体选择使用哪一种延迟值(最小值/最大值/典型值)在建立器件行为模型时要用到延迟的最小值/最大值/典型值,这是因为受到集成电路制造工艺过程的影响,真实的器件延迟总是在最大值和最小值之间的范围内变化。三延迟值的定义为: 在verilog中,用户除可以指定上面所述的三种类型的延迟以外,对每种类型的延迟还可以指定其最小值、最大值和典型值.用户可以在仿真-开始时就决定具体选择使用哪一种延迟值(最小值/最大值/典型值)在建立器件行为模型时要用到延迟的最小值/最大值/典型值,这是因为受到集成电路制造工艺过程的影响,真实的器件延迟总是在最大值和最小值之间的范围内变化.三延迟值的定义为:

最小值:设计者预期逻辑门所具有的最小延迟。

典型值:设计者预期逻辑门所具有的典型延迟。

最大值:设计者预期逻辑门所具有的最大延迟。

学习时间

20230613

学习小结

门的基本类型包括: and (与门),or(或门),xor (异或门),buf(缓冲门〉和not(非门〉等。每种门都有逻辑符号、真值表和对应的 Verilog 原语。这些原语的调用(实例引用)方法和模块的调用方法一样,但这些原语是Verilog语言预定义的(不需要自行编写)门的任意一个输入发生变化以后,门的输出立即被重新计算。

Verilog支持内部原语实例数组和用户定义的模块。

每种门都具有三种类型的延迟:上升延迟、下降延迟和关断延迟。Verilog语言允许对每种门指定一个、两个或三个不同的延迟值。Verilog 仿真器会根据指定的数值对三种(上升、下降和关断)延迟的具体值进行计算。

用户可以对Verilog 中的每种延迟分别指定最小值、典型值和最大值,并且可以在仿真时指定具体使用哪个值进行仿真。这种机制使得用户可以灵活地使用不同的延迟值进行仿真,而无需改变Verilog源描述。