本文分别以DDR/DDR2/DDR3为例介绍

DDR 266、DDR2 533、DDR3 1066

一、核心频率

核心频率即DDR的clk频率

DDR 266 核心频率133MHz

DDR2 533 核心频率 133MHz

DDR3 1066 核心频率 133MHz

266 533 1066是DDR的标签表示的就是DDR的标称单bit位宽数据传输速率或等效频率

二、工作频率

DDRx是差分工作时钟,数据传输在时钟的上下边沿,工作频率为核心频率的2倍。所以:

DDR 266 工作频率 266MHz

DDR2 533 工作频率 266MHz

DDR3 1066 工作频率 266MHz

三、内存等效频率

DDR 266 等效频率 266MHz

DDR2 533 等效频率 533MHz

DDR3 1066 等效频率 1066MHz

四、预取

预取的核心就是并串转换

为什么要预取?DDR的工作频率是核心频率的两倍,那么它所需要的数据必然也是SDRAM的2倍,就需要数据预取。相应的DDR内部总线位宽比SDRAM宽一倍。

DDR 2bit预取

DDR2 4bit预取

DDR3 8bit预取

所以相同的ddr内核频率下,DDR3的等效频率是DDR的4倍,DDR2的2倍

首先纠正一下,8bit预取技术只能通过I/O控制器将等效频率提高为实际频率的4倍,而DDR技术再次翻倍才使最终等效频率达到核心频率的8倍。

8bit预取技术即是在I/O控制器发出请求信号之前,存储单元已经事先准备好了8bit的数据。为了实现这一原理,采用了并行转串行数据线的设计,即将多个存储单元构成矩阵,将数据经由统一双极型晶体管DQ总线发射。下图有助于说明。

可以形象理解为一个蓄水池里接了8根进水管,却只接了一根出水管,那么出水速度肯定是极快的。也就是说,对DDR3,存储单元的内部总线位宽:芯片位宽(即I/0控制器位宽)=8:1。这就像是硬盘的Raid阵列技术。(本段摘自百度知道)

问题:

1.DDR是不是同时读取2个bank,DDR2同时读取4个bank,DDR3同时读取8个bank??

2.读取bank用的是哪个时钟clk_p or clk_q?

3.预取的数据要不要并行转串行?

4.I/O位宽是怎么回事?

是否假如单颗DDR3 16bit,核心频率为133MHz时,DDRC连接DDR3的I/O为128bit时可以做如下推论:

需要8颗DDR3 16bit,DDR3内部总线位宽128bit(8bit预取),8颗DDR3 16bit总带宽16.65GBps,则DDRC最大满负荷工作频率为1066MHz(不考虑latency),DDRC如果工作频率为533MHz只能最大达到8颗DDR3 16bit总带宽的50%???

5.DDRC(DDR控制器)数据速率匹配是怎么做的?

6.多颗DDR是如何连接

7.单颗DDR的位宽是如何确定

由下图看到这块内存条是4GB 2Rx8,其中4GB是整个内存条的储存空间。2Rx8表示该内存条是2 Rank 每颗ddr位宽8bit。Rank的概念问题8介绍

8.多颗DDR组成的是多通道?

一个DDR颗粒或者说单颗DDR也就是 ddr single chip。从上图来看就是一个黑块就是一颗DDR芯片,上图HMT351S6BFR8C-H9就是由16颗DDR组成的2 rank内存条。图中只看到8颗是因为该款为双面

一个i7 CPU支持两个Channel(双通道),每个Channel上可以插俩个DIMM,而每个DIMM由两个rank构成,8个chip组成一个rank。由于现在多数内存颗粒的位宽是8bit,而CPU带宽是64bit,所以经常是8个颗粒可以组成一个rank。所以小张的内存条2R X 8的意思是由2个rank组成,每个rank八个内存颗粒。由于整个内存是4GB,我们可以算出单个内存颗粒是256MB。

由上面一段的叙述 可知多通道和单颗DDR之间还有DIMM-->rank。所以整个层级是 channel-->DIMM-->rank-->single chip

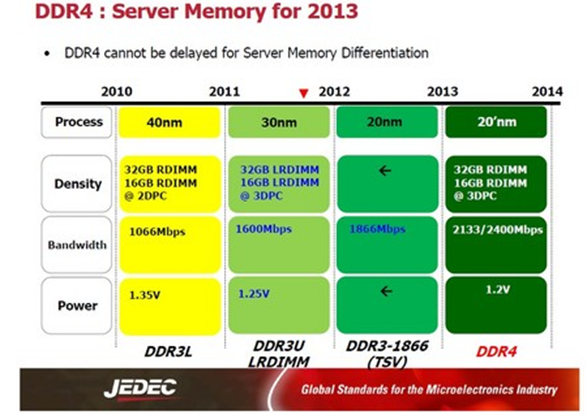

五、DDR4

DDR4的预取任然是8bit

在DDR在发展的过程中,一直都以增加数据预取值为主要的性能提升手段。但到了DDR4时代,数据预取的增加变得更为困难,所以推出了Bank Group的设计。每个Bank Group可以独立读写数据,这样一来内部的数据吞吐量大幅度提升,可以同时读取大量的数据,内存的等效频率在这种设置下也得到巨大的提升。DDR4架构上采用了8n预取的Bank Group分组,包括使用两个或者四个可选择的Bank Group分组,这将使得DDR4内存的每个Bank Group分组都有独立的激活、读取、写入和刷新操作,从而改进内存的整体效率和带宽。如此一来如果内存内部设计了两个独立的Bank Group,相当于每次操作16bit的数据,变相地将内存预取值提高到了16n,如果是四个独立的Bank Group,则变相的预取值提高到了32n。(该段粘贴复制)

六、带宽计算

带宽=等效工作频率x通道数x通道位宽

其中单颗DDR 通道数为1

七、DDR3的地址及容量

八、位宽

以DDR3颗粒为例,单颗最大bit位宽为16bit。若需要构成64bit位宽则需要4颗DDR3的内存芯片

内存模组位宽=内存芯片位宽×单面芯片数量(假定为单面单物理BANK)