SD RAM

SDRAM—Synchronous dynamic random-access memory (SDRAM)。

同步动态随机存取存储器,即数据的读写需要时钟来信号同步。其存储单元不是按线性排列的,是分页的。

DRAM和SDRAM由于实现工艺问题,容量较SRAM大,但是读写速度不如SRAM,且不需要刷新操作。

DDR信号

CK-时钟

CK和CK#是差分时钟输入。所有地址和控制输入信号均在CK的上升沿和CK的下降沿的交点处采样。

CKE-时钟使能

内部时钟信号以及设备输入缓冲器和输出驱动器激活CKE HIGH,而禁用CKE Low。

将CKE设为低电平可提供预充电掉电和自刷新操作(所有Bank都处于空闲状态),或有效掉电(在任何Bank中均处于活动状态)。

对于自刷新退出,CKE是异步的。 在上电和初始化序列期间VREFCA和VREFDQ变得稳定之后,必须在所有操作(包括自刷新)中维护它们。

在整个读写访问过程中,必须将CKE保持在较高水平。掉电期间禁用除CK,CK,ODT和CKE以外的输入缓冲器。自刷新期间禁用除CKE以外的输入缓冲区。

CS-片选

CS设置为高电平时,所有命令均被屏蔽。CS为具有多个等级的系统提供外部等级选择。CS被视为命令代码的一部分。

ODT-端接

ODT(注册为HIGH)使能DDR3 SDRAM内部的端接电阻。

启用后,ODT仅适用于x4 / x8配置的每个DQ,DQS,DQS和DM / TDQS,NU / TDQS(当通过MR1中的模式寄存器A11 = 1启用TDQS时)信号。

对于x16配置,ODT应用于每个DQ,DQSU,DQSU,DQSL,DQSL,DMU和DML信号。

如果MR1被编程为禁用ODT,则ODT引脚将被忽略。

命令输入

RAS,CAS和WE(以及CS)定义要输入的命令。

RAS:行地址;

CAS:列地址;

WE:写使能信号。

DM-输入信号屏蔽

DM是用于写数据的输入掩码信号。 在写访问期间,当DM采样到与该输入数据一致的高电平时,将屏蔽输入数据。

DM在DQS的两个边缘上采样。 对于x8设备,通过MR1中的模式寄存器A11设置启用DM或TDQS / TDQS功能。

BA0/BA1-组地址输入

BA0-BA2定义将哪个活动,读取,写入或预充电命令应用到哪个组。存储体地址还确定在MRS周期中是否要访问模式寄存器或扩展模式寄存器。

A0-A15-地址信号输入

为活动命令提供行地址,为读/写命令提供列地址,以从相应存储体的存储器阵列中选择一个位置。 (A10 / AP和A12 / BC具有其他功能,请参见下文)。

在模式寄存器设置命令期间,地址输入还提供操作码。

A10/AP-预充电

在读/写命令期间对A10进行采样,以确定是否应在读/写操作后对所访问的存储体执行自动预充电。(高:自动预充电;低:无自动预充电)。

在预充电命令期间对A10进行采样,以确定预充电是适用于一个Bank(A10低电平)还是适用于所有Bank(A10高电平)。如果仅要预充一个Bank,则按Bank选择该Bank地址。

A12/BC-突发传输

在读取和写入命令期间对A12 / BC进行采样,以确定是否将执行突发斩波。(高,无突发斩波;低:突发斩波)。

RESET-复位

低电平有效异步复位:当RESET为低电平时复位有效,而当RESET为高电平时无效。

在正常操作期间,RESET必须为高电平。

RESET是CMOS轨到轨信号,其DC高低为VDD的80%和20%,即DC高时为1.20V,DC低时为0.30V。

DQ-数据输入输出

双向数据总线。

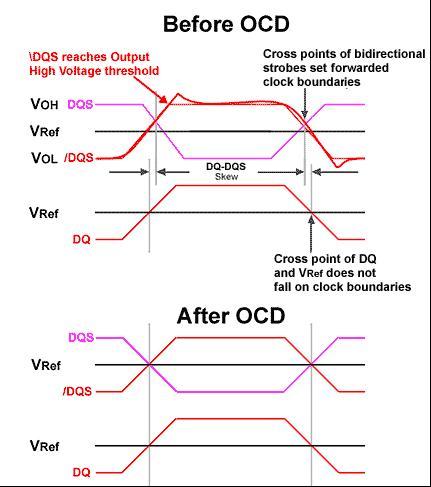

DQS-数据选通

数据选通:输出带读数据,输入带写数据。 与读取数据边缘对齐,以写入数据为中心。

数据选通DQS,DQSL和DQSU与差分配对;分别向DQS,DQSL和DQSU发送信号,以在读取和写入期间向系统提供差分对信令。

DDR3 SDRAM仅支持差分数据选通,不支持单端。

TDQS-8位数据选通

TDQS / TDQS仅适用于x8 DRAM。 通过MR1中的模式寄存器A11 = 1启用时,DRAM将在TDQS / TDQS上启用与DQS / DQS相同的终端电阻功能。

当通过MR1中的模式寄存器A11 = 0禁用时,DM / TDQS将提供数据屏蔽功能,并且不使用TDQS。

x4 / x16 DRAM必须通过MR1中的模式寄存器A11 = 0禁用TDQS功能。

ZA Calebration-ZQ校准

ZQ校准参考引脚

VREFDQ

DQ参考电压

VREFCA

CA参考电压

DQ Power Supply: 1.5 V +/- 0.075 V

DQ电源:1.5 V +/- 0.075 V