名词解释

NAND Flash:半导体闪存

HDD:机械硬盘

FW:固件

Peak Power:峰值功率

Active Power:读写功耗

Idle Power:空闲功耗

standby/sleep Power Dev Sleep Power:SSD内部休眠功耗

RAM:掉电丢失数据

FGT:浮栅晶体管

FormFactor:尺寸标准件

AFA:全闪存整列

性能测试

性能测试工具:IoMeter、FIO

连续读写吞吐量:Throughput

随机读写:IOPS

访问模式

Random 随机 Sequentiall连续

SSD的操作流程:

主机 -> 写命令 -> 收Data到Chash -> FLT发出写闪存请求 -> 写出命令

注意:闪存不能履写,闪存块需要先写擦后写

SLC:1bit数据闪存(电压区分,高0低1)

MLC:2bit数据闪存(电子数区分)

TLC:3bit数据闪存

DIE/LUN是接收和执行闪存命令的基本单元: LUN>Plane>Block>Page

FTL

FTL是Flash Translation Layer(闪存转换层)

**闪存块的重要特性:**地址映射、垃圾回收、磨损平衡、坏块管理、读干扰处理、数据保持处理

- 闪存块(Block)需要先擦除后写入,不能覆盖写(Update in Place)。FTL还需要做垃圾回收:把若干个闪存块上的有效数据搬出,写到某个新的闪存块,然后把之前的闪存块擦除(GC,Garbage Collection,垃圾回收)

- 磨损均衡(Wear Leveling)让数据写入均摊到每个闪存块上,让每个闪存块的磨损保持均衡,保证SSD实现最大的数据写入量。闪存块的寿命使用PE(Program/EraseCount)进行衡量。

- 避免读干扰

- 数据保持(Data Retentuion):上电后扫描全盘,搬动刷新数据

- 坏块管理

- MLC\TLC的特殊处理:避免Lower Page数据被Upperpage/ExtraPage写入时破坏;改善性能和可靠性;

FTL也可以区分主机端和设备端两种实现

映射管理

使用LBA(Logical Block Address,逻辑块地址)访问SSD。

映射表可以放在板载DRAM、SRAM和闪存中,HMB技术:NVME1.2>版本可以将映射表放置在主机的DRAM中

映射表刷新:新产生的映射关系累计到达一定阈值、用户写入的数据量达到一定阈值、闪存写完闪存块的数量达到一定阈值

垃圾回收GC

一般选择每个Die上块号一样的所有闪存块做垃圾回收

写放大:WA

Trim

数据作废指令

磨损平衡

冷数据:不经常更新;热数据:更新频繁

新老块:擦写次数

动态磨损平衡(DynamicWL):把热数据写到年轻的块上

静态磨损平衡(StaticWL):冷数据写到老年的块上,一般使用GC机制实现

冷热数据混合写会导致性能下降,写放大

掉电恢复

掉电前需要完成的工作:把buffer中缓存的用户数据刷入闪存;把映射表刷入闪存;闪存的快信息写入;SSD的其它信息写入;

在掉电之前设置Checkpoint(快照点),在快照点写入当前状态信息、映射表、缓存数据等。

坏块管理

坏块的来源:出厂坏块、增长坏块(后期使用产生的坏块),坏块的第一个闪存页和最后一个闪存页数据区的第一个字节和Spare区的第一个字节会被写上一个非0XFF的值。或者单独建立坏块信息表

坏块管理:略过(Skip)、替换(Replace)替换模式需要在每个Die上分配预留空间

SLC Cash

将MLC或者TLC中的部分闪存块配置成SLC模式:性能、防止LowerPage数据被破坏、解决闪存缺陷、更多的数据写入量

强制写入:用户数据必须先写入到SLC闪存块,然后通过GC搬到MLC/TLC

RD&DR

RD:电子从基底进入浮栅极,使电子翻转(1到0)(高电平为0,低电平为1)

DR:栅极电子穿过绝缘材料,使比特翻转(0到1)

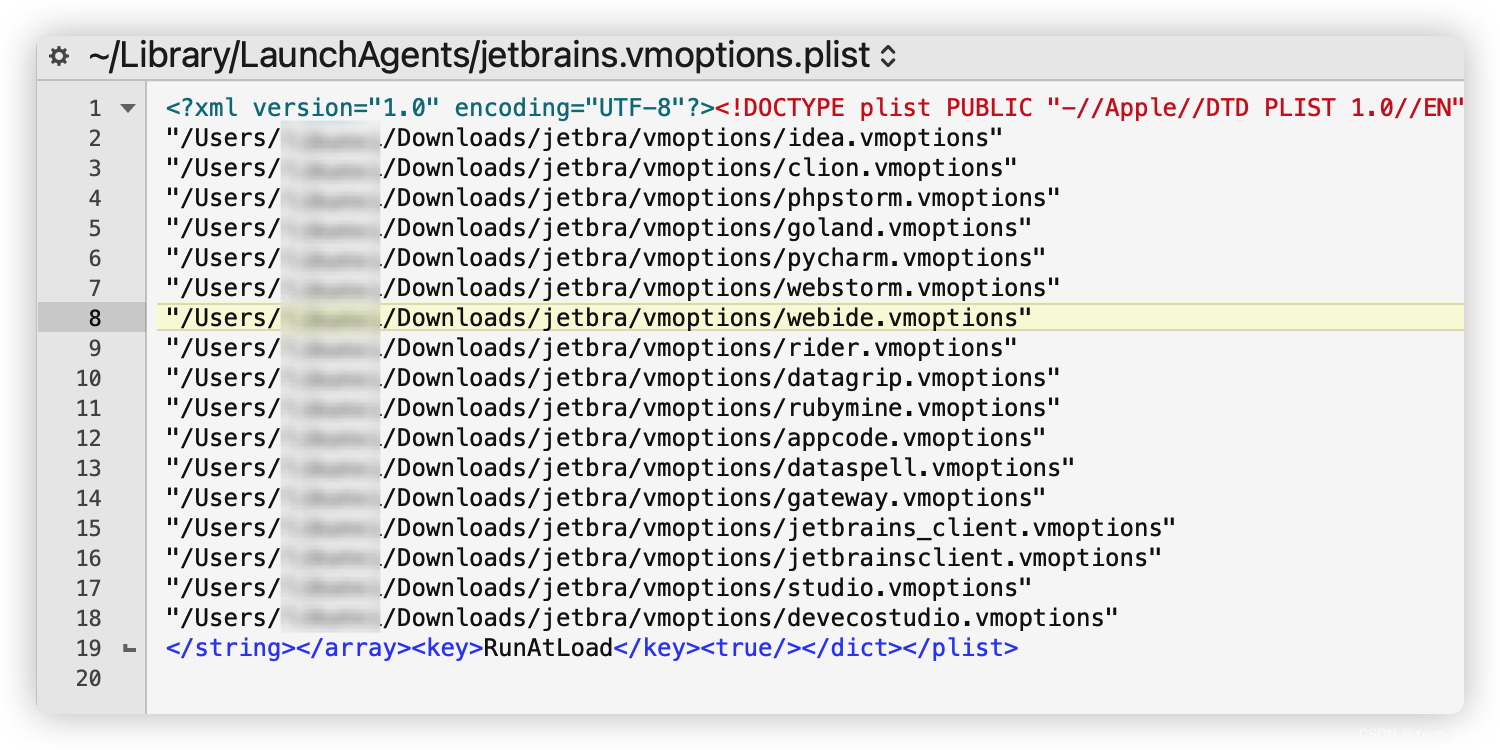

DeviceBasedFTL

1)主机驱动:为应用程序提供读写接口,和板载控制器通过NVMe等协议进行交互

2)板载控制器:

- 通过SATA\NVMe等协议接收主机发送的命令并执行

- 管理SSD,实现FTL垃圾回收磨损平衡等算法

- 控制和实现闪存时序

3)闪存阵列:存储介质

ECC

纠错的核心是通过增加冗余信息,使得原始信息的编码之间有足够大的区别

奇偶校验(Parity-Check)

校验矩阵H 和生成矩阵G

LDPC (Low Density Parity-Check Code)

低密度奇偶校验:正则LDPC保证校验举证每行有固定J个1,每列有固定K个1,非正则LDPC无此限制

eMMC

系统特性

eMMC = MMC标准接口 + MMC控制器 + NAND Flash

JESD84-B51,它规范了总线接口以及控制芯片,而对在系统架构中的主机和存储阵列部分的内容并没有未完全规定。

上电:确定工作模式,通信速率

内部结构:控制器+nanoflash

供电:VCC\VCCQ

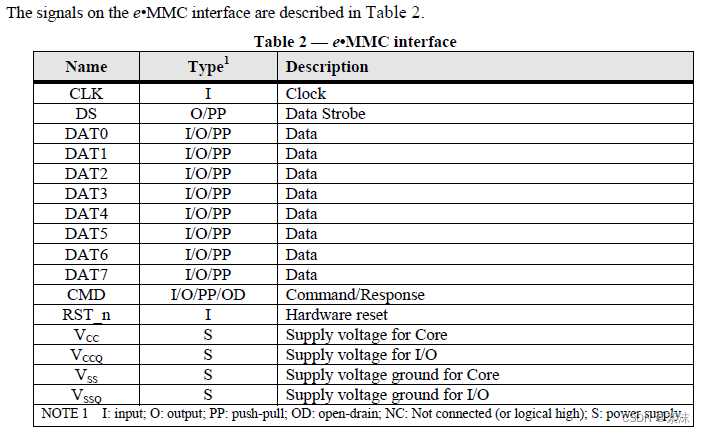

总线:cmd dat clk ds

eMMC的总线由11条信号线组成:

- 1条时钟信号线(CLK): 用于从主机输出时钟信号,进行数据传输的同步和设备运作的驱动。

- 1条数据选通信号线( Data Strobe ): 在eMMC 5.0中引入的一根时钟信号线。它是由eMMC发送给主机的,且频率与时钟线相同,用于和主机端进行数据接收的同步。该信号线只能在HS400模式下配置启用,启用后可以提高数据传输的稳定性。

- 1条命令信号线(CMD): 是双向命令通道信号线,用于主机向eMMC发送命令以及eMMC向主机回传应答。CMD线在上电后都是保持高电平状态,因此命令和应答数据的起始位都是“0”

- 8条数据信号线(DAT0-7): 用于主机和eMMC之间的数据传输。在设备上电或者软复位后,只有DAT0可以进行数据传输,在eMMC完成初始化后,可通过命令CMD6配置DAT0-3或者DAT0-7进行数据传输,即将eMMC配置为 4 bits或者8 bits传输模式。

eMMc控制器

- 协议

- 擦写均衡

- 坏块管理

- ECC校验

- 电源管理

- 时钟管理

- 数据存取

初始化

1、上电 , 进入到pre-idle状态

1)软件复位,设备收到从主机发来的GO_PRE_IDLE_STATE命令(参数为 0xF0F0F0F0的CMD0);

2)硬件复位,可以通过主机拉高RST_n信号线来触发。

2、eMMC确认是否需要进入引导模式

3、eMMC进入引导模式

5、idle状态 : eMMC在退出引导模式后,会进入到设备识别模式中的idle状态。如果没有启用引导模式,上电、硬件重置或软件重置后,都会使eMMC进入 Idle状态。

eMMC完成内部初始化后,会进入Ready状态。主机可以通过发送CMD2广播命令获取总线上所有进入Ready状态的eMMC的CID。

主机发送CMD3赋予这个eMMC一个相对设备地址(RCA) ,使设备进入到Stand-by状态 。

cmd0\1\2\3\7

设备状态切换

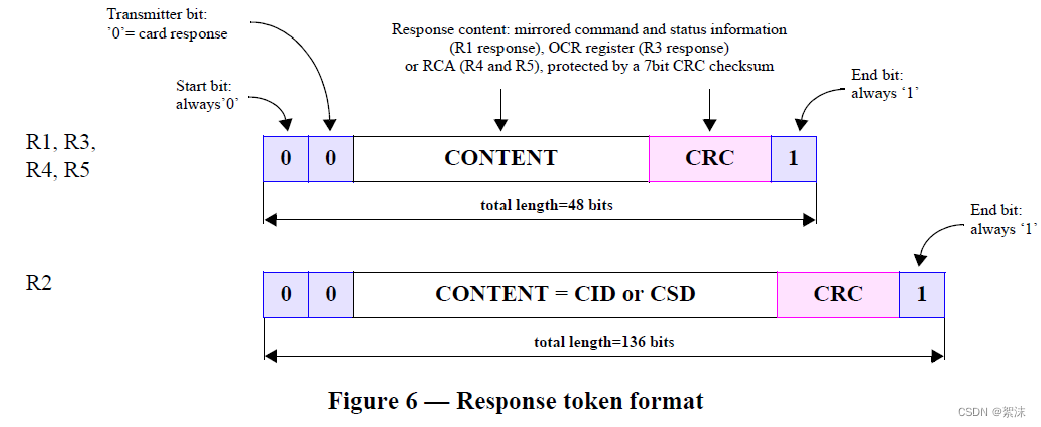

帧格式

cmd response data

命令及响应

命令:启动一种操作的token,从主机发往设备。命令在CMD线上串行传输。

应答:从设备发往主机作为对上一命令回答的token。应答在CMD线上串行传输。

数据:数据线数可以是1(DAT0)、4(DAT0-DAT3)或8(DAT0-DAT7)

CMD线在上电后都是保持高电平状态,因此命令和应答数据的起始位都是“0”

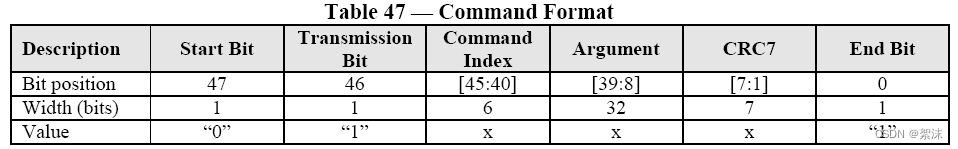

命令格式:

e•MMC总线数据传输包括命令、应答和数据块结构token。数据传输是总线操作。操作总是包含一个命令和一个应答token。此外,某些操作有数据token。

**数据格式:**在所有的数据传输模式下,数据块的传输模式都比较相近,主要又四个部分组成:

StartBit(0)+Data+CRC(0)+StopBit(1)StartBit(0)+Data+CRC(0)+StopBit(1) StartBit(0)+Data+CRC(0)+StopBit(1)

emmc的命令由48bit长度组成,固定以0开始,以1结束,其中的data包含:

transmiter bit:表示数据传输的方式,1代表 host to device ;

command index :使用6个bit指示了command的索引,取值范围是0~63

argument :指代command需要附带发送的参数,具体是否要带参数看具体的command是什么CMDx指令。

CRC7 :包含前面各个部分的数据CRC校验值。接收方如果收到的CRC校验值和计算值不同则会视为传输数据错误。

eMMC将command index(0~56)分成12个class,每个class代表一类功能,包含所有commands的一个子集。具体某一个设备支持哪些class的命令,可以通过CSD寄存器的CCC[95:84]feilds来查询,如bit84为1则表示支持class0。

| 命令分来 | 描述 | note |

|---|---|---|

| class 0 | basic | 基本命令 |

| class 1 | obsolete | 废弃 |

| class 2 | block read | 块数据读相关命令,包括设置块长度、读取单块、读取多块 |

| class 3 | obsolete | 废弃 |

| class 4 | block write | 块数据写相关命令,包括设置块个数、写入单块、写入多块、修改设备id寄存器、修改CSD、设置RTC |

| class 5 | erase | 设置擦除组开始地址、设置擦除组结束地址、擦除操作 |

| class 6 | write protection | 设置写保护、清除写保护、获取device的写保护状态、获取写保护类型 |

| class 7 | lock device | lock/unlock device |

| class 8 | application-specific | 指示下一个命令是一个特定应用命令而非标准命令 |

| class 9 | I/O mode | 写寄存器、设置系统进入中断模式 |

| class 10 | security protocols | 连续传输数据块从device to host或从host to device |

| class 11 | command queuing | 执行队列里的任务 |

寄存器

***OCR:***工作条件寄存器,存放设备的电压信息概况和访问模式;

- ***CID:***设备识别寄存器,存放设备在识别阶段所使用到的设备识别信息。每个设备都有一个独一无二的识别号;

- ***RCA:***相对地址寄存器,存放设备在识别阶段主机分配的设备地址。此地址用于设备识别之后主机与设备之间的寻址通讯;

- ***CSD:***数据寄存器,寄存着设备内容访问方式的信息,其中定义了数据格式、读写数据块的大小、最长数据访问时间、数据传输速度、DSR寄存器是否可用等。

- ***EXT_CSD:***扩展数据寄存器,定义了设备属性和选定的模式。它长512 字节,高320位字节是属性段,定义了设备能力,不能被主机更改。低192位字节是模式段,定义了设备的工作配置。主机可以通过SWITCH命令(CMD6)改变这些配置。

- ***DSR:***驱动寄存器,用于扩展操作条件以提高总线性能(取决于总线长度、传输速率或设备数等参数)

- ***QSR:***队列状态寄存器,存储着在特定时间点队列中的任务状态。

正常读写

主机可以通过命令CMD7,将指定的eMMC从Stand-by状态切换到Transfer状态,然后对eMMC进行读写操作。

主机向eMMC发送读取命令后,eMMC会根据命令参数,向主机发送对应的数据块,发送结束后,eMMC会重新进入Transfer状态

主机向eMMC发送写入命令后,eMMC会根据命令参数,接收从主机发来的数据块,每接收一个数据块,eMMC都会进行CRC校验,校验无误后,eMMC会进入Programming状态,将数据块烧录进NAND Flash里,同时还会将DAT0信号拉低,直到烧录结束。烧录结束后,eMMC返回到Transfer状态。

DAT有两种传输模式:

- SDR(Single Data Rate,1个时钟内传1bits)

- DDR(Double Data Rate,1个时钟内传2bits)

在DDR双倍数据率模式下,DAT线在时钟的上升沿(奇数字节 Byte 1,3,5 …)和下降(偶数字节Byte 2,4,6 …)沿都会传输数据。

每条DAT线上都有两个相互交织的CRC16:

上升沿的CRC组成 odd CRC16,用于校验该DAT线上所有上升沿比特组成的数据。

下降沿的CRC组成even CRC16,用于校验该DAT线上所有下降沿比特组成的数据。

emmc分区

内部的存储空间被划分为了4类区域,最多可以支持8个硬件分区

***Boot Area Partitions:***启动区域分区,存储Bootloader,支持SOC从emmc启动

boot state: Power-up、HW reset 或者 SW reset 后满足条件进入

RPMB Partition 安全特性分区

GeneralPurposePartition 可选分区,可以为分区设置一些额外的属性,比如:提高该分区的读写性能、寿命以及稳定性或者将这些用来作为存放操作系统类的、很少进行擦写更新的分区等。

User Data Area 用户存储区域