三 LPM——counter IP核使用

小结:counter(IP核)cin进位输入,clock时钟信号,cout进位输出,q当前计数值

FPGA设计方式

调用IP核

路径放到prj的ip文件夹下

名字叫counter就行

几位的计数器

计数到多少,4位的记不到100,Clock Enable时钟使能信号,Couter Enable计数使能信号,Carry in/out输入输出都勾上

在这里插入图片描述

下面默认的都不贴

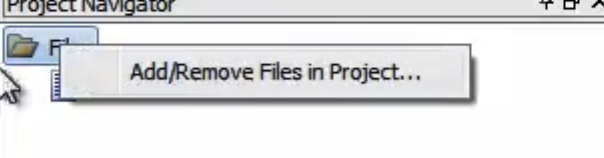

只有一个文件时一定要点add,多个不用了

设为顶层文件,分析和综合一下

设计时只需要关注端口就行

ip核内部做了很多优化,性能有很大提升

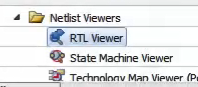

这个可以看内部结构

写ip核的测试文件

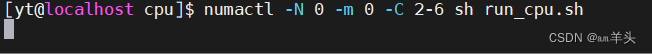

`timescale 1ns/1ns`define clock_period 20module counter_tb;reg cin;reg clk;wire cout;wire [3:0] q;counter counter0(.cin(cin),.clock(clk),.cout(cout),.q(q));initial clk=1;always #(`clock_period/2)clk=~clk;initial beginrepeat(5)begincin=0;#(`clock_period*5)cin=1;#(`clock_period)cin=0;end#(`clock_period*200)$stop;endendmodule

加入仿真文件assignments—>setting—>

记得把名字复制到上面的test bench name

可以这样将数值从二进制改成unsigned

改ip核参数

ip核的位数不变

改为默认

变成计数到最大

八位计数器

右边这个应该是q[7:4]

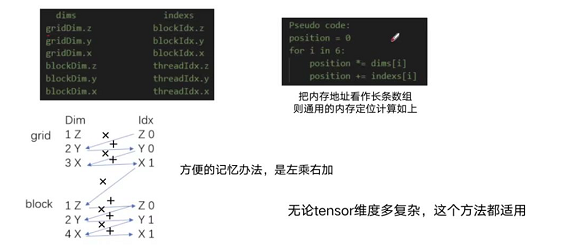

再新建一个模块文件

module counter_top(cin,clk,cout,q);input cin;input clk;output cout;output [7:0]q;wire cout0;counter counter0(.cin(cin),.clock(clk),.cout(cout0),.q(q[3:0]));counter counter1(.cin(cout0),.clock(clk),.cout(cout),.q(q[7:4])); endmodule保存到prj,分析综合,设为顶层文件

新建一个仿真文件

`timescale 1ns/1ns`define clock_period 20module counter_top_tb;reg cin; //进位输入reg clk; //计数基准时钟wire cout;//进位输出wire [7:0] q;counter_top counter0(.cin(cin),.clk(clk),.cout(cout),.q(q));initial clk = 1;always #(`clock_period/2)clk = ~clk;initial beginrepeat(20)begin//给多少脉冲具体看计数器怎么设置cin = 0;#(`clock_period*5)cin = 1;#(`clock_period)cin = 0; end#(`clock_period*200);$stop;endendmodule重新设置仿真文件

进行仿真

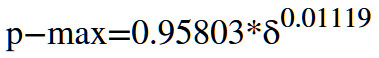

如果将最大计数改为10,八位的记到153(10011001)(99)

总结:实际上都是用的软件官方的ip核的计数器模板,

例化不一定是在模块文件里,也可以是在仿真文件里,相当于调用库函数