数字光纤通信线路编译码实验

此实验属于西电大三选修光通信课程的实验,共分为两部分,第一部分为光纤通信系统综合实验(在实验室完成),第二部分为数字光纤通信线路编译码实验,此文章主要讲解第二部分,另外两次实验的实验报告与工程文件可前往此处下载:https://download.csdn.net/download/yifantan/85941354?spm=1001.2014.3001.5503

一、实验目的

- 熟悉指定序列NRZ码生成原理以及光纤线路CMI编译码原理。

2.初步熟练Altera公司QUARTUS II仿真平台的使用。

3.进一步熟悉数字电路设计技巧。

4.基本掌握如何进行FPGA的电路设计与仿真。

5.了解FPGA功能的物理验证。

二、实验环境

QUARTUS II 13.0

三、实验基本原理及预习

- 编写VERILOG语言新工程,设计实现FPGA内部功能: 15位学号序列(二进制码(非BCD码)表示的本人学号最后四位(前面补零))NRZ码的生成;

CMI编码;

CMI译码(在实验室条件下使用统一系统时钟,输入为CMI编码输出);

时钟分频功能 - 使用对所做设计完成正确编译。

- 使用ALTERA-MODELSIM仿真环境完成信号波形仿真。

FPGA电路仿真的输入输出信号即各测试点信号要求如下:

输入:系统时钟信号(7.68MC) :1路;

输出:周期15位二进制后四位学号序列:

1路;(480Kbps)

CMI编码输出信号: 1路;

CMI译码输出信号: 1路; - 对仿真信号波形结果进行原理分析,发现可能的问题并加以解决,得到正确的仿真结果。

四、设计文件

| 设计文件代码展示 |

module test_top(output reg pin98_te3, //codeinoutput reg pin99_te4, //cmi_cededoutput reg pin100_te5, //cmi_decodedinput wire pin103_te6, //system clk 7.68Mhzinput wire rst //reset);reg [3:0] counter; //对时钟clk1十六分频 对时钟clk2八分频

reg clk1; //学号NRZ序列及CMI解码序列时钟 480kbps

reg clk2; //CMI编码序列时钟960kpbsalways@(posedge pin103_te6 or negedge rst) //counter从0到15循环

beginif(!rst) counter <= 4'b0;else if(counter == 4'b1111)begincounter <= 4'b0;endelse if(pin103_te6)begin counter <= counter+1;end

end// clk1, 16分频

always@(posedge pin103_te6 or negedge rst)

beginif(!rst)clk1 <= 0;else if(counter[3] == 0)clk1 <= 1'b0;else if(counter[3] == 1)clk1 <= 1'b1;

end//clk2, 8分频

always@(posedge pin103_te6 or negedge rst)

beginif(!rst)clk2 <= 0;else if(counter[2] == 0)clk2 <= 1'b1;else if(counter[2] == 1)clk2 <= 1'b0;

end//输出15位学号NRZ码 后四位0094 变为1011110

reg [3:0] num;

always@(posedge clk1 or negedge rst)

beginif(!rst)beginnum <= 4'b0;endelse if(num == 4'b1111)beginnum <= 4'b0;endelse num <= num+1;case(num)4'b1001:pin98_te3 <=1;4'b1010:pin98_te3 <=0;4'b1011:pin98_te3 <=1;4'b1100:pin98_te3 <=1;4'b1101:pin98_te3 <=1; 4'b1110:pin98_te3 <=1; 4'b1111:pin98_te3 <=0;default:pin98_te3 <=0;endcase

end reg [1:0] cmi_reg; //CMI编码寄存器

reg flag =0;

always@(posedge clk1)

beginif(pin98_te3 == 0) //0码变为01码cmi_reg <= 2'b01;else if(pin98_te3 == 1) //1码变为00、11交替beginif(flag == 0)begincmi_reg <= 2'b00;flag <=~flag;endelse if(flag == 1)begincmi_reg <= 2'b11;flag <=~flag;endend

end// cmi_ceded 输出CMI编码

reg flag0 = 1'b0;

always@(posedge clk2)

beginflag0 <= flag0 + 1;if(flag0 == 1)pin99_te4 <= cmi_reg[0];else if(flag0 == 0)pin99_te4<=cmi_reg[1];

end//cmi_decoded 输出CMI解码

always@(posedge clk2)beginif(cmi_reg == 2'b01)pin100_te5<=0;else if(cmi_reg==2'b00 || cmi_reg==2'b11)pin100_te5<=1;endendmodule

激励文件等其他部分请前往资源下载(内含完整报告和工程文件):https://download.csdn.net/download/yifantan/85941354

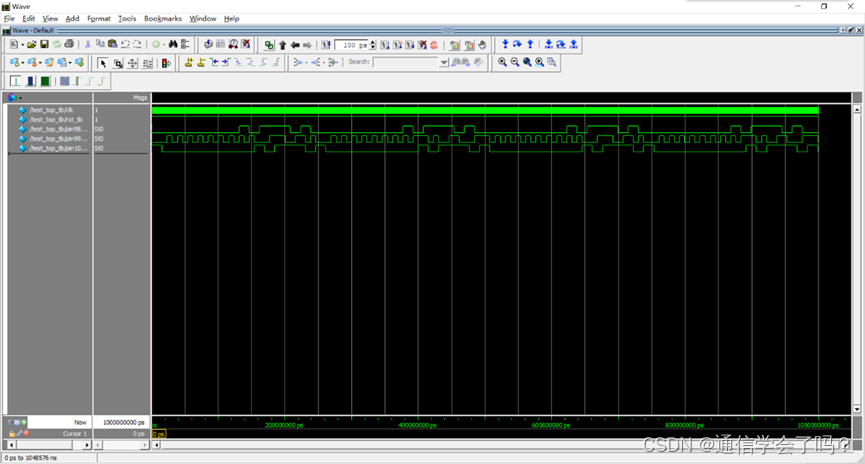

五、仿真结果分析

MODELSIM软件中的波形仿真文件

相关报告和代码请前往此处下载:https://download.csdn.net/download/yifantan/85941354?spm=1001.2014.3001.5503