大家都知道在芯片设计行业,项目是至关重要的一环。从项目的初期到交付,不同的岗位的工程师在项目的各环节主要负责什么?他们是怎样配合的?下面看看资深工程师怎么说。

一个项目,从初期到交付的过程是比较漫长的。我们知道最早的时候,我们把它叫做项目规划,即 schedule。

这个schedule 实际上讲芯片的基本的性能达到什么样的要求,包括功耗、封装等相关的东西,就是项目立项,这是第一点了。我们讲了如果你概念都出现了错误,即项目一开始定义的时候,比如你要做一个高性能的控制,你的CPU都达不到这样的能力,坦率的讲你这个项目是不会成功的。

到第二阶段就变成了RTL的细节设计。这是我们对这种设计工程师的要求了,简单点讲,你通过HDL的形式把我们的ideal转化成一个可以综合的电路,这是我们比较核心的东西。

跟所谓的RTL对应的,你编出来的功能一定要保证至少功能的正确性。这部分东西就是我们说的叫做DFV,即验证工程师。这几部分搞定了之后,再往下是综合工程师了,再往下就是物理实现的工程师,即后端设计实现的工程师。

再往下就会有两个工程师出现了。你要保证你的这样的一个设计是满足时序的要求,这是一部分。还有一部分我们说的叫什么?叫PV,即physical verification,准确的进就是你设计出来的图纸需要满足厂家定义的设计规则。否则我们讲你一定是不可以成功流片的。也就是你做了这样的设计之后,你的设计不可制造。

我基本上在这样的一个绿色的区域里面,虽然我是后端工程师,我天天在跟RTL的工程师打交道。我们知道你作为一个RTL的工程师,你需要完成两件事情。RTL程师不仅仅是你会用、会写HDL代码,这是不可以的。你做一颗芯片,功能正确是你最基本的要求。除此之外,你还要满足性能的指标,还要满足功耗和面积的指标。这几点缺一不可。

作为我们来讲,我们认为RTL工程师实际上是在做两件事情。第一件事情是要通过自己的个人技能,比如某种HDL,我要实现这样的一个功能,比如一个通信芯片、一个控制芯片等等,你要实现这样的一个基本功能。

第二件事情是在实现这样的功能的基础之上,你需要设计时序,我们讲时序是设计出来的,不是后端的工程师努力出来的,后端工程师只能做锦上添花的一件事情,谈不上雪中送炭了。

我们讲了后端工程师只能做这种锦上添花的事情,达不到脱胎换骨的级别,也就是所有的根源都在RTL。大家最后统一的一句话就是,所有问题的根源都在设计,这个还是括号,不包含DFV验证出来的错误。

因为我们讲了后端工程师,实际上是不关心功能的。每个圈里面都有好多人了,到了这里你也就知道了自己大概都要做什么。一个项目至少每一个圈里面都有一个人,也是经过二三十年的发展,比较完善、比较能够保证设计质量的一个流程。

我们讲了刚才也说过了,所有的问题的根源都在RTL上。比如我们后端做完之后,功耗超标怎么办,面积超标,怎么办?这样的情况下,必然要通过RTL的调整,才能够完成。

整个团队,包括前端,后端,还是分不太清楚的,天天都在配合,无时无刻都在配合。这是我给大家要讲的我的一些个人理解。

下面就来为大家分享六大方向的项目资源

数字前端设计

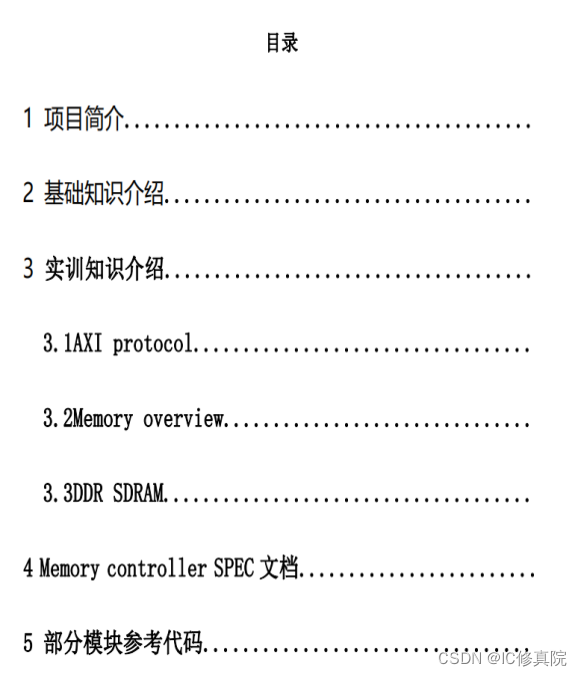

本项目设计完成了一个 memory controller 模块,实现了对 array read/write/refresh的控制,其接口完成了 AXI bus 到 array interface 之间的转换。

数字功能验证

本项目基于UVM验证平台。UART作为通用串行数据总线,用于异步双向通信,实现数据的串并传唤。此UART模块支持全双工数据传输和接收,数据位58bit,停止位12bit,奇偶校验,16个字节FIFO深度。

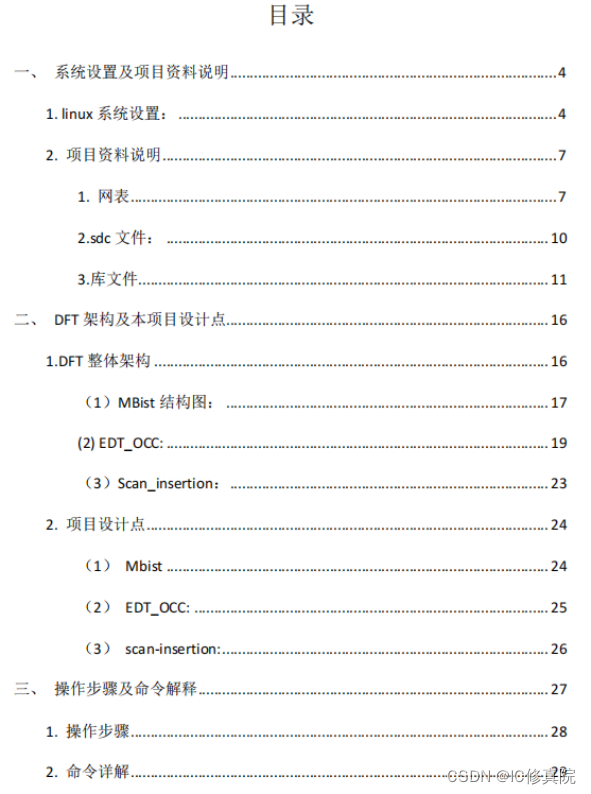

数字DFT设计

本项目基于tessent,内包含8W+寄存器,完成了对辅助MCU的NPU芯片的DFT设计。

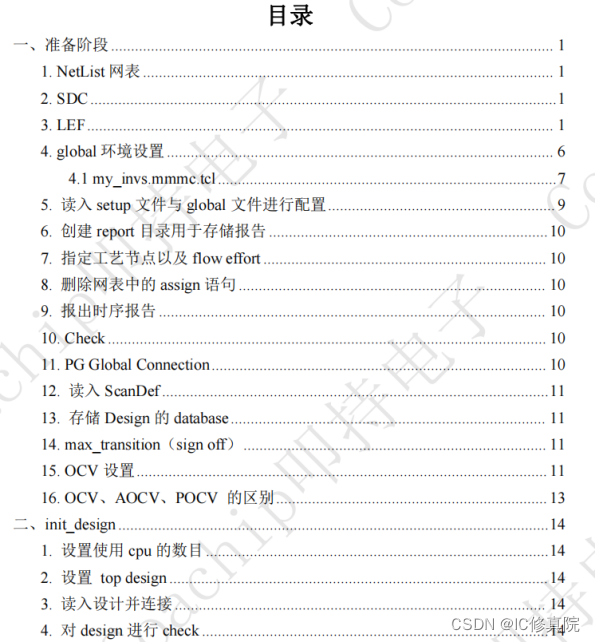

数字后端实现

本项目是一款采用tsmc28nm工艺的aes运算模块,项目实现过程覆盖数字后端APR、STA、Formal等流程,模块规模达到20W+instance,工作频率为500Mhz,模块尺寸1mm*1mm。

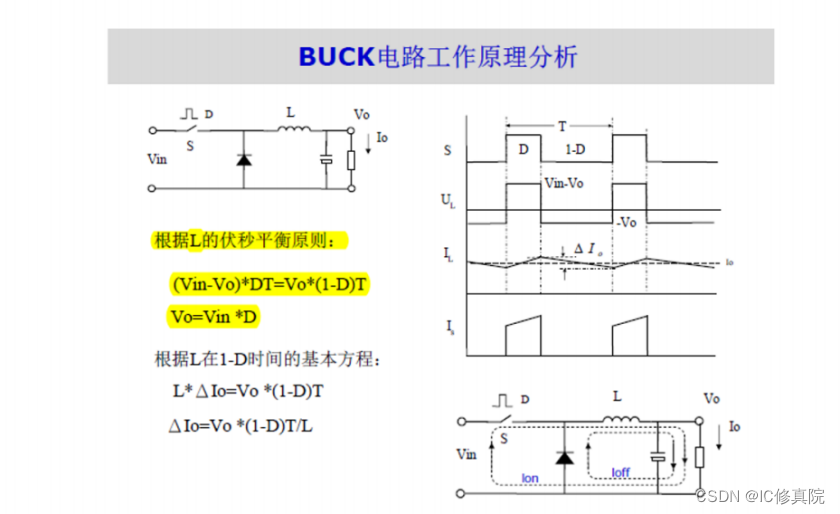

模拟IC设计

本项目设计了一款开关型直流电压变换器(Buck),实现了对输入直流电压的降压变换。

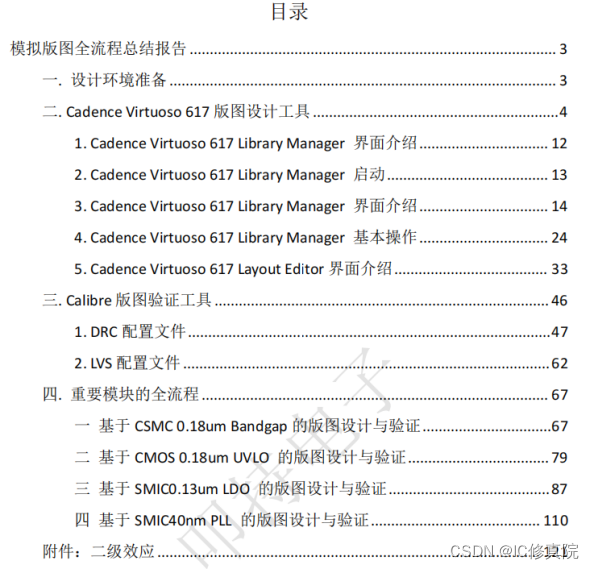

模拟版图

内含四个项目,设计主要基于virtuoso 617,完成了CSMC 0.18um工艺Bandgap版图设计/CSMC 0.18um工艺UVLO版图设计/SMIC 0.13um工艺LDO版图设计/SMIC 40nm工艺PLL版图设计,并通过版图物理验证,按照器件匹配规则,对版图性能进行优化。

如果你当下对入行/转行有一定困惑和意向,或者想获取项目资源,以及免费获取学习资料,任何关于转行的问题都有老师会为你解答。

这里放个入口:IC入行指导