题目描述

设计一个状态机,用来检测序列 10111,要求:

1、进行非重叠检测 即101110111 只会被检测通过一次

2、寄存器输出且同步输出结果

注意rst为低电平复位

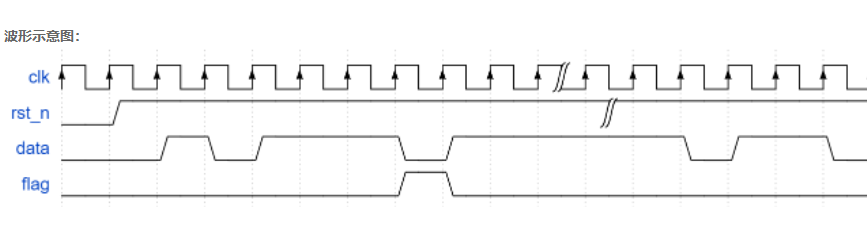

这一题比较简单,就是一个普通的Moore状态机,从波形图来看,在接收了10111之后,指示信号flag置高电平,随后开始接收判断1,而不是接收0;稍微需要留意的是,由于选择的是非阻塞赋值,所以再进行flag输出判断时,判断条件应该为nstate == F(接收最后一个1后跳变的状态,详见代码) 而不是state == F,以免慢一个clk。

具体详解如下,题目简单就不画状态图了

`timescale 1ns/1nsmodule sequence_test1(input wire clk ,input wire rst ,input wire data ,output reg flag

);

//*************code***********//parameter A=0,B=1,C=2,D=3,E=4,F=5;reg [2:0] state,nstate;always @(*) beginif(~rst)nstate <= A;elsecase(state)A: nstate <= (data)? B:A; //初始态,接收1 B: nstate <= (data)? B:C; //接收0,若为1,保持B;C: nstate <= (data)? D:A; //接收1,若为0,返回A D: nstate <= (data)? E:A; //接收1,若为0,返回A E: nstate <= (data)? F:A; //接收1,若为0,返回A F: nstate <= A;endcase endalways @(posedge clk or negedge rst) beginif(~rst)state <= A;elsestate <= nstate;endalways @(posedge clk or negedge rst) beginif(~rst)flag <= 0;elseflag <= (nstate==F)? 1:0 ;end//*************code***********//

endmoduledone!