| 接口 | 分辨率 | 说明 |

| RGB | 800*480以下 | 大部分AP均支持RGB接口,此类LCD在低端平板广泛使用 |

| LVDS | 1024*768及以上 | 主要通过转换芯片将RGB等专程LVDS来支持;少量AP直接集成;此类LCD目前在中高端平板和笔记本中广泛使用 |

| MIPI | 1080P以下 | 手机平台标准接口,与LVDS类似,但更省电;目前普及趋势明显,TI、nVidia、高通等最新平台大多配备RGB和MIPI接口;1080P是其能力的极限 |

| eDP | 支持1080P以上 | 比较新的规范,在笔记本行业将广泛用于取代LVDS,支持超高分辨率 |

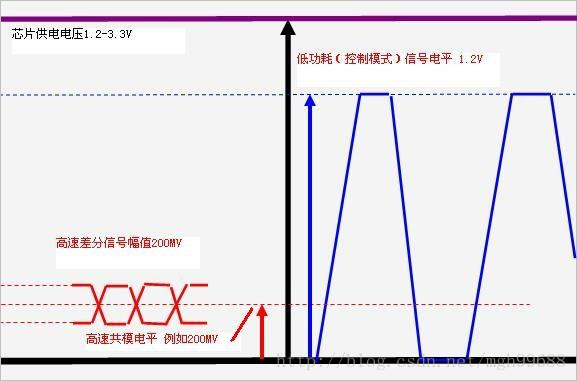

MIPI 是专门在高速(数据传输)模式下采用低振幅信号摆幅,针对功率敏感型应用而量身定做的。图2比较了MIPI与其它差分技术的信号摆幅。

由于MIPI是采用差分信号传输的,所以在设计上需要按照差分设计的一般规则进行严格的设计,关键是需要实现差分阻抗的匹配,MIPI协议规定传输线差分阻抗值为80-125欧姆。

图2:几种流行的差分摆幅(differential-swing)技术的信号振幅比较

----------------------------------------------------------------------------------------------------------------

MIPI规定了一个差分时钟通道(lane)和一个从1到4数量可扩展的数据通道,可根据处理器和外设的需求来调节数据率。而且,MIPI D-PHY规范只给出了数据率范围,并没有规定具体的工作速率。在一个应用中,可用的数据通道和数据率都由接口两端的器件决定。不过,目前可用的MIPI D-PHY IP内核可提供每数据通道高达1 Gbps的传输率,这种特性无疑意味着MIPI完全适用于当前及未来的高性能应用。

采用MIPI作为数据接口还有一大好处。由于MIPI DSI 和 CSI-2架构为新设计带来了灵活性,并支持XGA显示和高于8百万像素相机等令人瞩目的功能,故MIPI非常适合于新的智能电话和MID设计。有了具备MIPI功能的新处理器设计提供的带宽能力,现在就可以考虑利用单个MIPI接口来实现高分辨率双屏显示和/或双相机等新颖功能了。

在采用了这些功能的设计中,针对MIPI信号进行设计和优化的高带宽模拟开关,如飞兆半导体公司的FSA642,可用于多个显示屏或相机组件之间的切换。FSA642是一款高带宽三路 差分单刀双掷 (SPDT)模拟开关,能够实现两个外设MIPI器件之间共享一路MIPI 时钟通道和两路MIPI数据通道。这样的开关可以提供一些额外的优点:对未选择器件的杂散信号(stub)进行隔离,并提高布线和外设布局的灵活性。为了确保MIPI互连路径上的这些物理开关的成功设计,除带宽之外,还必须考虑以下一些主要的开关参数:

1. 关断隔离:为了保持有源时钟/数据路径的信号完整性,要求开关具备高效的关断隔离性能。对于200mV、最大共模失配(common-mode mismatch)5mV的高速MIPI差分信号,开关路径之间的关断隔离应该为-30dBm或更好。

2. 差分延迟差:差分对内部信号间的延迟差(skew)(差分对内延迟差)和时钟与数据通道差分交叉点之间的延迟差(通道间延迟差) 必需降至50 ps或更小。对于这些参数,这类开关的业界同类最佳延迟差性能目前在20 ps 到 30 ps之间。

3. 开关阻抗:在选择模拟开关时,第三个主要考虑事项是导通阻抗(RON) 和导通电容 (CON)的阻抗特性的折衷选择。MIPI D-PHY链路同时支持低功耗数据传输和高速数据传输模式。因此,开关的RON应该平衡选择以优化混合工作模式的性能。理想情况下,这一参数应该分别针对每一个工作模式而设定。结合每一模式的最佳RON,并保持很低的开关CON对保持接收端的压摆率(slew rate)十分重要。一般规则是,使CON 低于10 pF将有助于避免高速模式下通过开关的信号转换时间的恶化(延长)。

------------------------------------------------------------------------

MIPI接口的模组,相较于并口具有速度快,传输数据量大,功耗低,抗干扰好的优点,越来越受到客户的青睐,并在迅速增长。例如一款同时具备MIPI和并口传输的8M的模组,8位并口传输时,需要至少11根的传输线,高达96M的输出时钟,才能达到12FPS的全像素输出;而采用MIPI接口仅需要2个通道6根传输线就可以达到在全像素下12FPS的帧率,且消耗电流会比并口传输低大概20MA。由于MIPI是采用差分信号传输的,所以在设计上需要按照差分设计的一般规则进行严格的设计,关键是需要实现差分阻抗的匹配,MIPI协议规定传输线差分阻抗值为80-125欧姆。

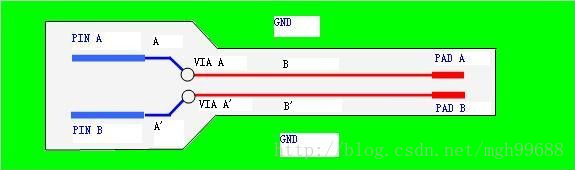

上图是个典型的理想差分设计状态,为了保证差分阻抗,线宽和线距应该根据软件仿真进行仔细选择;为了发挥差分线的优势,差分线对内部应该紧密耦合,走线的形状需要对称,甚至过孔的位置都需要对称摆放;差分线需要等长,以免传输延迟造成误码;另外需要注意一点,为了实现紧密的耦合,差分对中间不要走地线,PIN的定义上也最好避免把接地焊盘放置在差分对之间(指的是物理上2个相邻的差分线)。

下面简单介绍MIPI的通道模式和线上电平。在正常的操作模式下,数据通道处于高速模式或者控制模式。在高速模式下,通道状态是差分的0或者1,也就是线对内P比N高时,定义为1,P比N低时,定义为0,此时典型的线上电压为差分200MV,请注意图像信号仅在高速模式下传输;在控制模式下,高电平典型幅值为1.2V,此时P和N上的信号不是差分信号而是相互独立的,当P为1.2V,N也为1.2V时,MIPI协议定义状态为LP11,同理,当P为1.2V,N为0V时,定义状态为LP10,依此类推,控制模式下可以组成LP11,LP10,LP01,LP00四个不同的状态;MIPI协议规定控制模式4个不同状态组成的不同时序代表着将要进入或者退出高速模式等;比如LP11-LP01-LP00序列后,进入高速模式。下图为线上电平的图示。