引言

从本文开始,就开始系统学习 System Verilog ,不只是语法,还有结合 Questa Sim 的实际编程练习、Debug。

本文简单介绍 System Verilog 语言的用途以及学习的必要性。

前文链接:

我的 System Verilog 学习记录(1)

诸如 Verilog 和 VHDL 的硬件描述语言用于描述硬件行为,可以转换为由组合逻辑门和时序逻辑单元组成的电路块。为了验证 HDL 描述的硬件电路的正确性,需要一种在OOP(面向对象)具备更多特性的编程语言来支持复杂的测试流程,我们称之为 硬件验证语言。

System Verilog 就是Verilog 的一种拓展,具备诸多验证特性,允许EDA工具(引擎)使用复杂的testbench 和在仿真使用随机激励去验证设计。

为啥不用 Verilog 来做验证 ?

回溯到20世纪90年代,Verilog 是验证设计功能性的主要语言,但是只对能一些小规模设计、复杂度低的设计、特征量少的设计进行验证。随着设计复杂程度的提高,人们对更好的设计验证工具的需求程度也是渐渐增加。System Verilog 在这方面的优越性远超 Verilog ,因为其具备执行可约束的随机激励,在 testbench 结构中、功能覆盖率检查中、断言等等支持面向对象的特性。

何为验证 ?

验证就是保证一个硬件设计按预期运行的过程。芯片设计是一个涉及领域很宽并且很耗时的过程,需要耗资上百万去制造。如果在设计过程的早期阶段发现功能缺陷将会帮助节省很大的成本。如果在设计流程的后期发现一个 Bug ,那么所有的设计步骤需要重新再走一遍,这样会消耗很多资源、资金和时间,如果是设计的全流程都需要重新走一遍,那么这个过程称之为重新流片(respin)。

类似于 Vera 的硬件验证语言怎么样 ?

它们曾被使用过一段时间。System Verilog 可以看作是 Verilog(最流行的HDL语言) 的一种扩展,因此用它去验证 Verilog 的设计它是能够看的明白的。并且,System Verilog也支持面向对象,这将设计的验证过程提到了一个更到层次的抽象级。

它在验证中如何使用 ?

绝大多数的硬件设计都包含若干 Verilog 设计文件(.v 文件),其中有一个顶层文件,顶层文件中例化了各个子模块以达到整体设计的期望行为和功能。我们将验证所需的环境称为 testbench ,一般都用 System Verilog 语言去编写。目的就是用不同的激励驱动设计,然后观察输出,与期望值相比较,确定设计的行为是否正确。

为了达到这样的目的,设计的顶层模块应该例化在 testbench 环境中,并且设计的输入输出端口应该准确地和 testbench 中的组件信号相连接。设计的输入按照我们的意愿给进合适的激励信号。输出的结果和期望值进行分析比较,以确认设计行为是否正确。

举个栗子

chipverify官网给出了一个简单的设计验证例子:

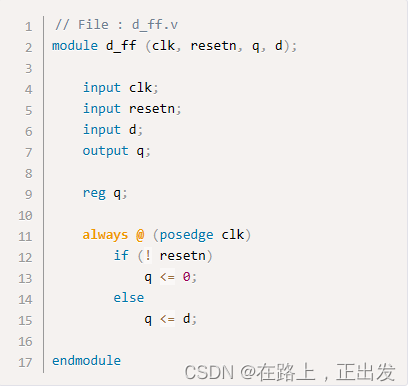

设计文件:

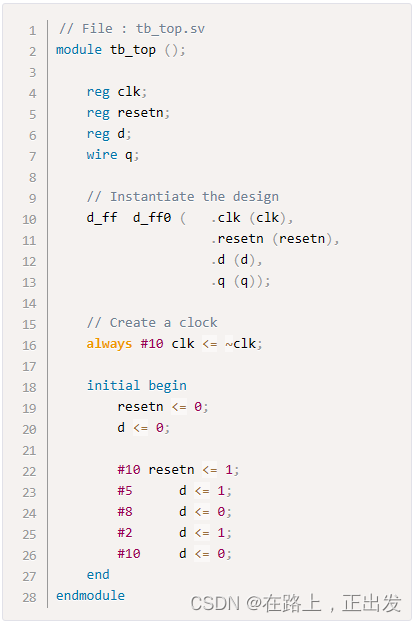

验证文件: