前言

本篇文章旨在讨论环境仿真中对于寄存器配置的随机。

寄存器域的随机性

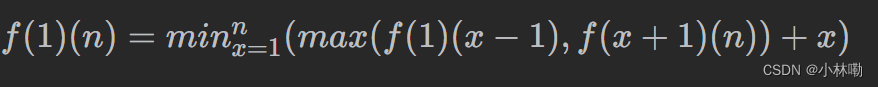

使用ralgen生成的寄存器本身是rand属性的,也就是说其自身是可以通过约束随机的方式在用例中进行随机性配置的,比如下面这个寄存器:

class ral_reg_REG_PRJ_sys_cfg_base_config extends uvm_reg;rand uvm_reg_field mode;rand uvm_reg_field kernel_size;rand uvm_reg_field stride;function new(string name = "REG_PRJ_sys_cfg_base_config");super.new(name, 32,build_coverage(UVM_NO_COVERAGE));endfunction: newvirtual function void build();this.mode = uvm_reg_field::type_id::create("mode",,get_full_name());this.mode.configure(this, 2, 0, "RW", 1, 2'h0, 1, 1, 0);this.kernel_size = uvm_reg_field::type_id::create("kernel_size",,get_full_name());this.kernel_size.configure(this, 20, 2, "RW", 1, 20'hab, 1, 1, 0);this.stride = uvm_reg_field::type_id::create("stride",,get_full_name());this.