目录

- 1.前言:

- 2.工程整体框架:

- 3.GTX IP 配置及细节讲解

- 4.GTX收发数据编解码讲解

- 5.工程1介绍:OV5640转GTX

- 6.工程2介绍:HDMI转GTX

- 7.上板调试

- 8.福利领取

1.前言:

没玩儿过GXP、GTX或者更高端的GTH、GTZ,都不好意思说自己玩儿过FPGA,这么说不怕得罪一大帮兄弟,事实的确如此,试想,如果你只玩儿过FPGA的流水灯、串口、I2C、图像处理之类的,其实并没有接触到FPGA的核心点,为啥呢?FPGA的流水灯、串口、I2C之类的东西,我一个stm32单片机足以,图像处理之类的我一个TI的DSP也可以,实在不行我上海思之类的也足以,那么你FPGA还有啥特别的?器件贵功耗还高;

但高速串行收发器呢?比如GTX,在FPGA面前,还有谁?呵呵~~

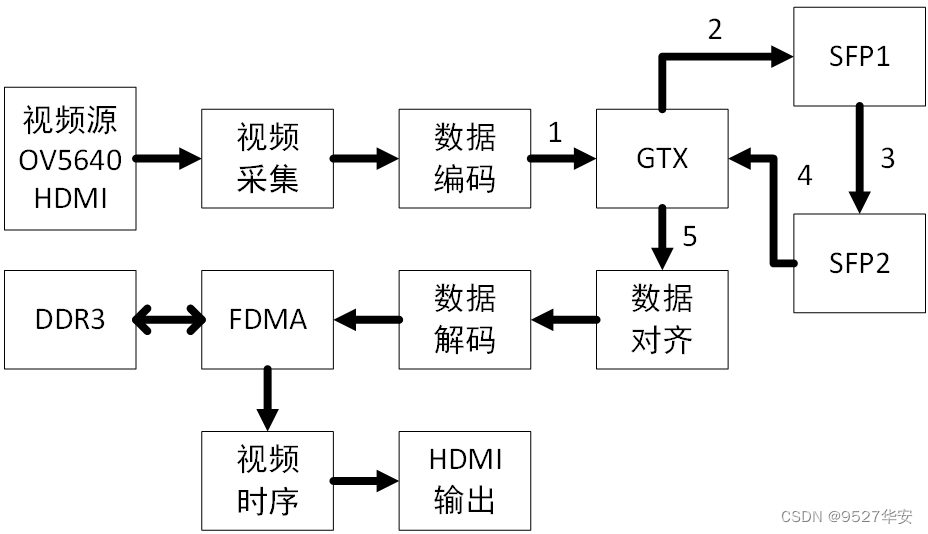

2.工程整体框架:

工程整体框架如下:

视频源:提供了两套工程,一个视频源是OV5640,另一个是HDMI输入,IT6802解码,关于IT6802解码部分,可以参考我之前的文章点击查看:IT6802解码HDMI视频

视频采集:OV5640和HDMI都采集为rgb888格式视频;

数据编码:将采集的rgb888格式视频数据编码为32为并行数据;

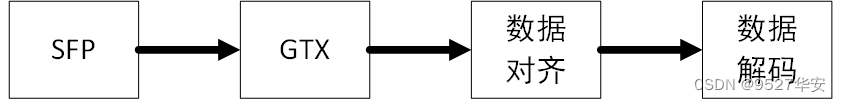

GTX:使用Xilinx官方IP实现,负责GTX的串并/并串转换:

SFP1:GTX发送接口,用过SFP线缆与SFP2连接,形成环路;

SFP2:GTX接收接口,用过SFP线缆与SFP1连接,形成环路;

数据对齐:接收GTX的串并转换后的32位数据,并对错位数据进行重新对齐,保证数据的完整性;

数据解码:将GTX的串并转换后的32位数据还原位带有vs、de和rgb888格式的视频流数据;

FDMA:负责对vs、de和rgb888格式的视频流数据做三帧缓存处理,使得输出视频变得流畅,关于FDMA部分可以参考我之前的文章点击查看:FDMA视频三帧缓存

DDR3:外设,缓存视频的内存;

视频时序:负责生成输出视频所需的时序,严格参照VASE标准设计;

HDMI输出:使用Xilinx官方原语设计的HDMI输出模块,负责将视频输出到显示器;

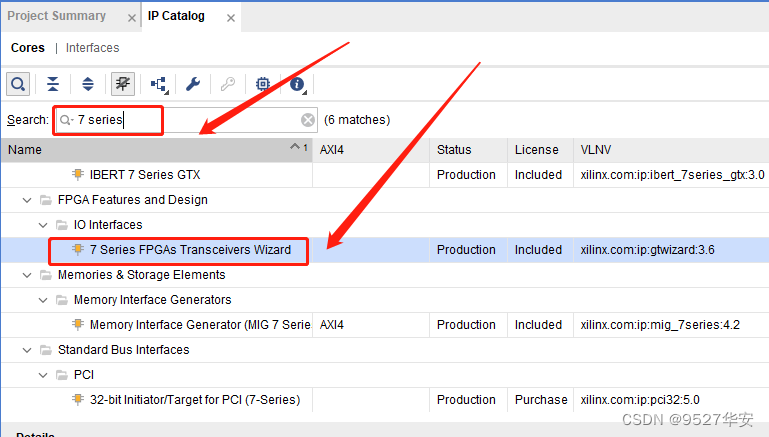

3.GTX IP 配置及细节讲解

前面的内容纯属装B,别当真。直接上干活:

在vivado里搜 7 series,就会出现这个ip,然后添加进来:

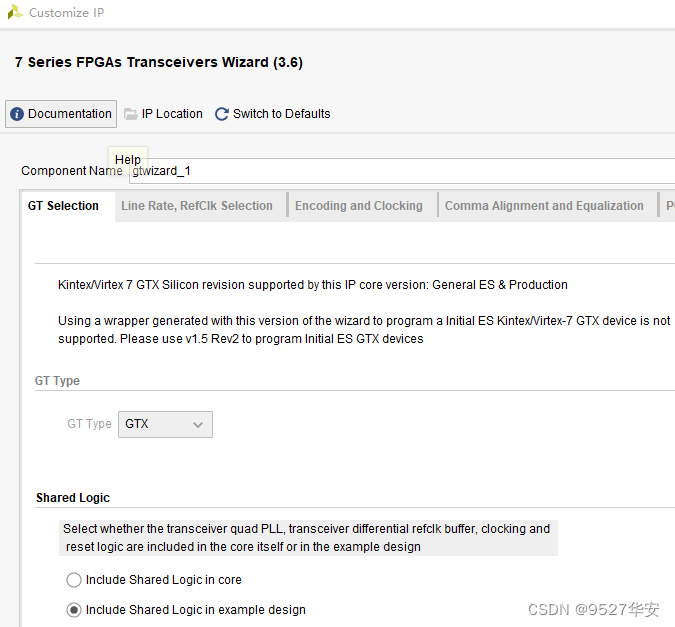

第一页选默认:

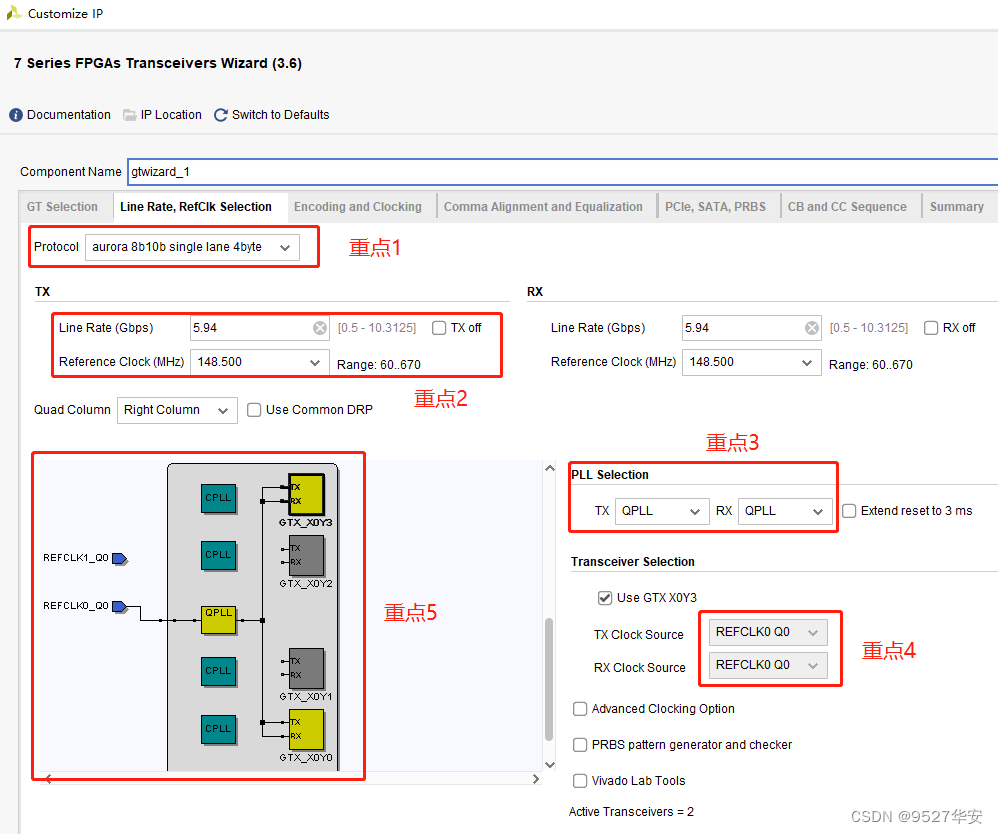

下一页全是重点,拿出小本本:

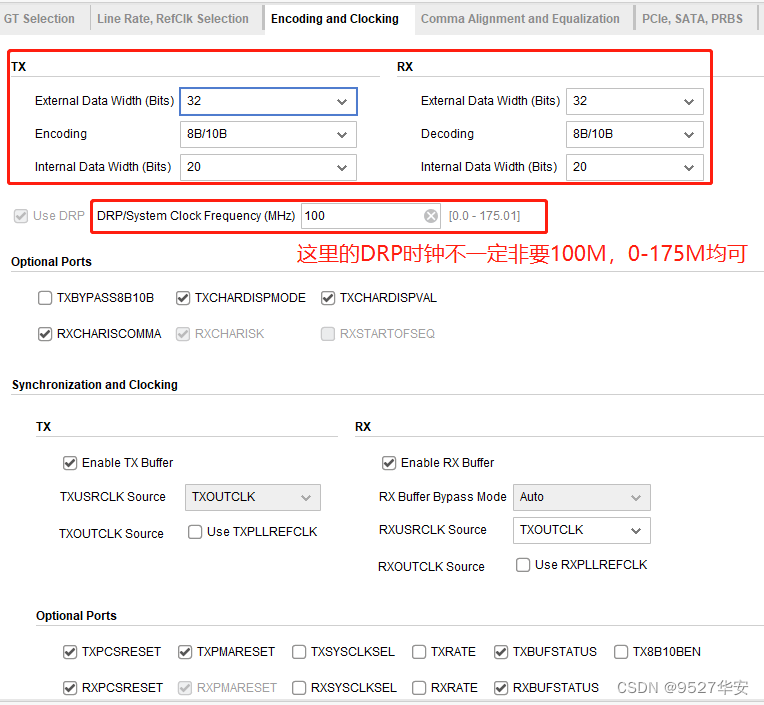

重点1:由于我们使用8bit/10bit编解码协议,所以选他;

下面的重点全部跟你板子的原理图密切相关,所以具体情况具体参考你的板子原理图,但方法是一样的;

重点2:线速率与参考时钟的选择:

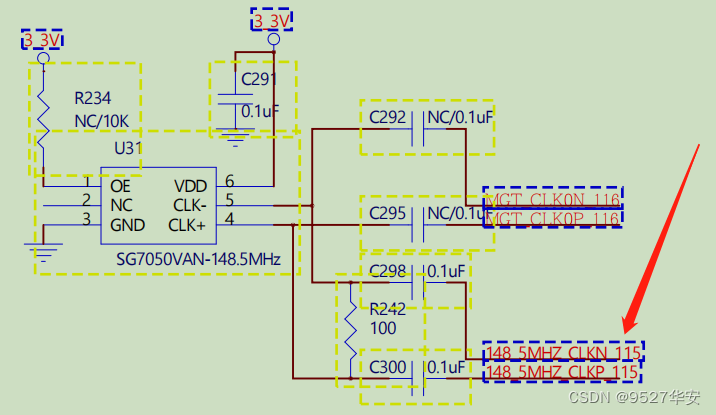

记住,线速率的选择取决于GTX差分时钟,具体看你的板子原理图,以我的板子为例,如下:

原理图可知,GTX的BANK115的REFCLK0接到了148.5的差分时钟,也就是说,我们的GTX参考时钟是148.5M;

补充一句,市面上的FPGA开发板(某原子某联某金)基本都是125M时钟,如果你自己的板子跟他们的板子时钟不一样,拿到他们的例程或教程跟着做时,估计你会一脸懵逼,这里不知道怎么配置了,哈哈。

好了说正事儿,既然参考时钟定了,那就剩下线速率的配置了,线速率=n参考时钟;

我的光模块最高能跑10G,所以就选择一个中间值吧,148.54=5.94G;

这下应该知道线速率和参考时钟怎么选了吧。

重点3:PLL选择;

这里可以选择CPLL和QPLL,都没问题;

重点4:收发引脚和时钟选择;

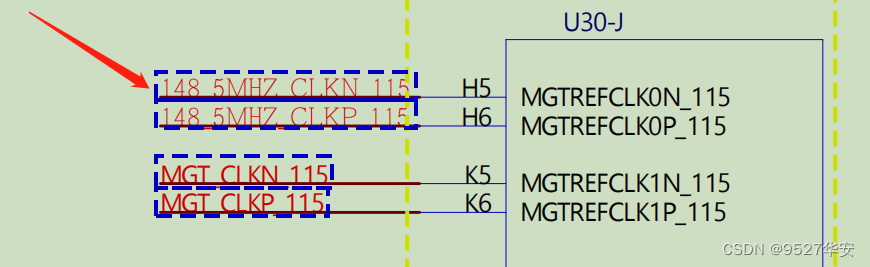

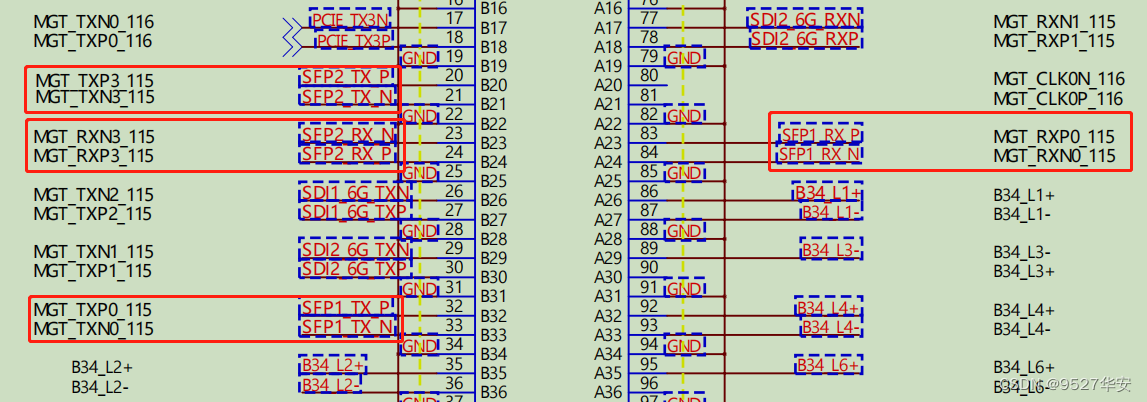

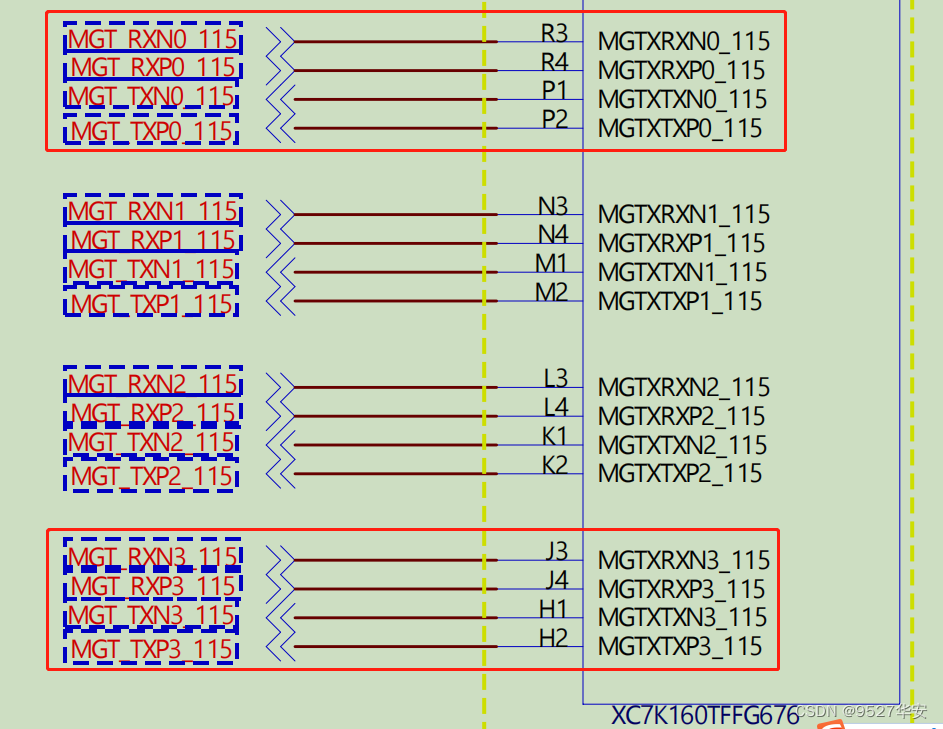

先看收发引脚,我的板子是K7-325T-FGG676,所以只有两个GTX,分别位于BANK115和BANK116,板子上有2个SFP接口,都连接在BANK115,原理图部分如下:

原理图可知:SFP1的收发引脚连接到了X0Y0;SFP2的收发引脚连接到了X0Y3;

??????咋得来的?

要说清楚这个问题,先看看GTX的组成;

我的板子只有2个GTX的基本组成是QUAD,简称Q,分为Q0和Q1,其中Q0对应BANM115,Q1对应BANM116,1个Q由4个GTPE2_CHANNEL和1个GTPE2_COMMON组成,具体去Xilinx官网看官方资料吧。

4个GTPE2_CHANNEL实际上就是4路GTX收发通道,命名和排序分别是:X0Y0、X0Y1、X0Y2、X0Y3,对应原理图中BANK115中的0~3;

这么讲应该能明白了;

所以我们需要使能X0Y0和X0Y3,也就是在小框里选√;

再根据前面的原理图可知:

参考时钟位于Q0的REFCLK0;

SFP1位于Q0的X0Y0;

SFP2位于Q0的X0Y3;

所以:重点4和重点5的选择就是这么来的,解析完毕;

下一页配置如下:

基本都是默认配置;

后面的配置都保持默认即可,然后生成IP;

然后打开官方例程:

然后打开官方例程的顶层文件,然后就是自由的DIY魔改了,

下面直接给出我的魔改方案源码:

`timescale 1ns / 1ps

`define DLY #1(* DowngradeIPIdentifiedWarnings="yes" *)

//***********************************Entity Declaration************************

(* CORE_GENERATION_INFO = "gtwizard_0,gtwizard_v3_6_11,{protocol_file=aurora_8b10b_single_lane_4byte}" *)

module gtwizard_0_exdes #

(parameter EXAMPLE_CONFIG_INDEPENDENT_LANES = 1,//configuration for frame gen and checkparameter EXAMPLE_LANE_WITH_START_CHAR = 0, // specifies lane with unique start frame charparameter EXAMPLE_WORDS_IN_BRAM = 512, // specifies amount of data in BRAMparameter EXAMPLE_SIM_GTRESET_SPEEDUP = "FALSE", // simulation setting for GT SecureIP modelparameter EXAMPLE_USE_CHIPSCOPE = 0, // Set to 1 to use Chipscope to drive resetsparameter STABLE_CLOCK_PERIOD = 10)

(input wire Q0_CLK0_GTREFCLK_PAD_N_IN,input wire Q0_CLK0_GTREFCLK_PAD_P_IN,//input wire DRP_CLK_IN_P,//input wire DRP_CLK_IN_N,//output wire TRACK_DATA_OUT,

//sfp1 output o_sfp1_tx_clk ,input [31:0] i_sfp1_tx_data ,input [3: 0] i_sfp1_tx_kchar, output o_sfp1_rx_clk ,output [31:0] o_sfp1_rx_data ,output [3: 0] o_sfp1_rx_kchar,output o_sfp1_tx_rstn ,output o_sfp1_rx_rstn ,

//sfp2 output o_sfp2_tx_clk ,input [31:0] i_sfp2_tx_data ,input [3: 0] i_sfp2_tx_kchar, output o_sfp2_rx_clk ,output [31:0] o_sfp2_rx_data ,output [3: 0] o_sfp2_rx_kchar,output o_sfp2_tx_rstn ,output o_sfp2_rx_rstn , input drp_clk_100m,input wire [1:0] RXN_IN,input wire [1:0] RXP_IN,output wire [1:0] TXN_OUT,output wire [1:0] TXP_OUT,output [1:0] sfp_tx_disable

);assign drpclk_in_i=drp_clk_100m;

assign sfp_tx_disable=2'b00;//sfp1

assign o_sfp1_tx_clk = gt0_txusrclk2_i ;//用户发送时钟

assign o_sfp1_rx_clk = gt0_rxusrclk2_i ;//用户接收时钟

assign gt0_txdata_i = i_sfp1_tx_data ;//用户发送数据

assign gt0_txcharisk_i = i_sfp1_tx_kchar ;//用户发送K码

assign o_sfp1_rx_data = gt0_rxdata_i ;//用户接收数据

assign o_sfp1_rx_kchar = gt0_rxcharisk_i ;//用户接收K码

assign o_sfp1_tx_rstn = gt0_txfsmresetdone_i ;//gtx初始化完成标志

assign o_sfp1_rx_rstn = gt0_rxfsmresetdone_i ;//gtx初始化完成标志//sfp2

assign o_sfp2_tx_clk = gt1_txusrclk2_i ;

assign o_sfp2_rx_clk = gt1_rxusrclk2_i ;

assign gt1_txdata_i = i_sfp2_tx_data ;

assign gt1_txcharisk_i = i_sfp2_tx_kchar ;

assign o_sfp2_rx_data = gt1_rxdata_i ;

assign o_sfp2_rx_kchar = gt1_rxcharisk_i ;

assign o_sfp2_tx_rstn = gt1_txfsmresetdone_i ;//gtx初始化完成标志

assign o_sfp2_rx_rstn = gt1_rxfsmresetdone_i ;//gtx初始化完成标志wire soft_reset_i;(*mark_debug = "TRUE" *) wire soft_reset_vio_i;//************************** Register Declarations ****************************wire gt_txfsmresetdone_i;wire gt_rxfsmresetdone_i;(* ASYNC_REG = "TRUE" *)reg gt_txfsmresetdone_r;(* ASYNC_REG = "TRUE" *)reg gt_txfsmresetdone_r2;wire gt0_txfsmresetdone_i;wire gt0_rxfsmresetdone_i;(* ASYNC_REG = "TRUE" *)reg gt0_txfsmresetdone_r;(* ASYNC_REG = "TRUE" *)reg gt0_txfsmresetdone_r2;(* ASYNC_REG = "TRUE" *)reg gt0_rxfsmresetdone_r;(* ASYNC_REG = "TRUE" *)reg gt0_rxfsmresetdone_r2;(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_r;(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_r2;(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_r3;(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_vio_r;(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_vio_r2;(* ASYNC_REG = "TRUE" *)reg gt0_rxresetdone_vio_r3;wire gt1_txfsmresetdone_i;wire gt1_rxfsmresetdone_i;(* ASYNC_REG = "TRUE" *)reg gt1_txfsmresetdone_r;(* ASYNC_REG = "TRUE" *)reg gt1_txfsmresetdone_r2;(* ASYNC_REG = "TRUE" *)reg gt1_rxfsmresetdone_r;(* ASYNC_REG = "TRUE" *)reg gt1_rxfsmresetdone_r2;(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_r;(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_r2;(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_r3;(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_vio_r;(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_vio_r2;(* ASYNC_REG = "TRUE" *)reg gt1_rxresetdone_vio_r3;reg [5:0] reset_counter = 0;reg [3:0] reset_pulse;//**************************** Wire Declarations ******************************////------------------------ GT Wrapper Wires ------------------------------//________________________________________________________________________//________________________________________________________________________//GT0 (X1Y0)//-------------------------- Channel - DRP Ports --------------------------wire [8:0] gt0_drpaddr_i;wire [15:0] gt0_drpdi_i;wire [15:0] gt0_drpdo_i;wire gt0_drpen_i;wire gt0_drprdy_i;wire gt0_drpwe_i;//------------------------- Digital Monitor Ports --------------------------wire [7:0] gt0_dmonitorout_i;//----------------------------- Loopback Ports -----------------------------wire [2:0] gt0_loopback_i;//---------------------------- Power-Down Ports ----------------------------wire [1:0] gt0_rxpd_i;wire [1:0] gt0_txpd_i;//------------------- RX Initialization and Reset Ports --------------------wire gt0_eyescanreset_i;wire gt0_rxuserrdy_i;//------------------------ RX Margin Analysis Ports ------------------------wire gt0_eyescandataerror_i;wire gt0_eyescantrigger_i;//----------------------- Receive Ports - CDR Ports ------------------------wire gt0_rxcdrhold_i;wire gt0_rxcdrovrden_i;//----------------- Receive Ports - Clock Correction Ports -----------------wire [1:0] gt0_rxclkcorcnt_i;//---------------- Receive Ports - FPGA RX interface Ports -----------------wire [31:0] gt0_rxdata_i;//----------------- Receive Ports - Pattern Checker Ports ------------------wire gt0_rxprbserr_i;wire [2:0] gt0_rxprbssel_i;//----------------- Receive Ports - Pattern Checker ports ------------------wire gt0_rxprbscntreset_i;//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------wire [3:0] gt0_rxdisperr_i;wire [3:0] gt0_rxnotintable_i;//------------------------- Receive Ports - RX AFE -------------------------wire gt0_gtxrxp_i;//---------------------- Receive Ports - RX AFE Ports ----------------------wire gt0_gtxrxn_i;//----------------- Receive Ports - RX Buffer Bypass Ports -----------------wire gt0_rxbufreset_i;wire [2:0] gt0_rxbufstatus_i;//------------ Receive Ports - RX Byte and Word Alignment Ports ------------wire gt0_rxbyteisaligned_i;wire gt0_rxbyterealign_i;wire gt0_rxcommadet_i;wire gt0_rxmcommaalignen_i;wire gt0_rxpcommaalignen_i;//------------------- Receive Ports - RX Equalizer Ports -------------------wire gt0_rxdfelpmreset_i;wire [6:0] gt0_rxmonitorout_i;wire [1:0] gt0_rxmonitorsel_i;//------------- Receive Ports - RX Fabric Output Control Ports -------------wire gt0_rxoutclk_i;wire gt0_rxoutclkfabric_i;//----------- Receive Ports - RX Initialization and Reset Ports ------------wire gt0_gtrxreset_i;wire gt0_rxpcsreset_i;wire gt0_rxpmareset_i;//---------------- Receive Ports - RX Margin Analysis ports ----------------wire gt0_rxlpmen_i;//--------------- Receive Ports - RX Polarity Control Ports ----------------wire gt0_rxpolarity_i;//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------wire [3:0] gt0_rxchariscomma_i;wire [3:0] gt0_rxcharisk_i;//------------ Receive Ports -RX Initialization and Reset Ports ------------wire gt0_rxresetdone_i;//---------------------- TX Configurable Driver Ports ----------------------wire [4:0] gt0_txpostcursor_i;wire [4:0] gt0_txprecursor_i;//------------------- TX Initialization and Reset Ports --------------------wire gt0_gttxreset_i;wire gt0_txuserrdy_i;//-------------- Transmit Ports - 8b10b Encoder Control Ports --------------wire [3:0] gt0_txchardispmode_i;wire [3:0] gt0_txchardispval_i;//---------------- Transmit Ports - Pattern Generator Ports ----------------wire gt0_txprbsforceerr_i;//-------------------- Transmit Ports - TX Buffer Ports --------------------wire [1:0] gt0_txbufstatus_i;//------------- Transmit Ports - TX Configurable Driver Ports --------------wire [3:0] gt0_txdiffctrl_i;wire [6:0] gt0_txmaincursor_i;//---------------- Transmit Ports - TX Data Path interface -----------------wire [31:0] gt0_txdata_i;//-------------- Transmit Ports - TX Driver and OOB signaling --------------wire gt0_gtxtxn_i;wire gt0_gtxtxp_i;//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------wire gt0_txoutclk_i;wire gt0_txoutclkfabric_i;wire gt0_txoutclkpcs_i;//------------------- Transmit Ports - TX Gearbox Ports --------------------wire [3:0] gt0_txcharisk_i;//----------- Transmit Ports - TX Initialization and Reset Ports -----------wire gt0_txpcsreset_i;wire gt0_txpmareset_i;wire gt0_txresetdone_i;//--------------- Transmit Ports - TX Polarity Control Ports ---------------wire gt0_txpolarity_i;//---------------- Transmit Ports - pattern Generator Ports ----------------wire [2:0] gt0_txprbssel_i;//________________________________________________________________________//________________________________________________________________________//GT1 (X1Y3)//-------------------------- Channel - DRP Ports --------------------------wire [8:0] gt1_drpaddr_i;wire [15:0] gt1_drpdi_i;wire [15:0] gt1_drpdo_i;wire gt1_drpen_i;wire gt1_drprdy_i;wire gt1_drpwe_i;//------------------------- Digital Monitor Ports --------------------------wire [7:0] gt1_dmonitorout_i;//----------------------------- Loopback Ports -----------------------------wire [2:0] gt1_loopback_i;//---------------------------- Power-Down Ports ----------------------------wire [1:0] gt1_rxpd_i;wire [1:0] gt1_txpd_i;//------------------- RX Initialization and Reset Ports --------------------wire gt1_eyescanreset_i;wire gt1_rxuserrdy_i;//------------------------ RX Margin Analysis Ports ------------------------wire gt1_eyescandataerror_i;wire gt1_eyescantrigger_i;//----------------------- Receive Ports - CDR Ports ------------------------wire gt1_rxcdrhold_i;wire gt1_rxcdrovrden_i;//----------------- Receive Ports - Clock Correction Ports -----------------wire [1:0] gt1_rxclkcorcnt_i;//---------------- Receive Ports - FPGA RX interface Ports -----------------wire [31:0] gt1_rxdata_i;//----------------- Receive Ports - Pattern Checker Ports ------------------wire gt1_rxprbserr_i;wire [2:0] gt1_rxprbssel_i;//----------------- Receive Ports - Pattern Checker ports ------------------wire gt1_rxprbscntreset_i;//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------wire [3:0] gt1_rxdisperr_i;wire [3:0] gt1_rxnotintable_i;//------------------------- Receive Ports - RX AFE -------------------------wire gt1_gtxrxp_i;//---------------------- Receive Ports - RX AFE Ports ----------------------wire gt1_gtxrxn_i;//----------------- Receive Ports - RX Buffer Bypass Ports -----------------wire gt1_rxbufreset_i;wire [2:0] gt1_rxbufstatus_i;//------------ Receive Ports - RX Byte and Word Alignment Ports ------------wire gt1_rxbyteisaligned_i;wire gt1_rxbyterealign_i;wire gt1_rxcommadet_i;wire gt1_rxmcommaalignen_i;wire gt1_rxpcommaalignen_i;//------------------- Receive Ports - RX Equalizer Ports -------------------wire gt1_rxdfelpmreset_i;wire [6:0] gt1_rxmonitorout_i;wire [1:0] gt1_rxmonitorsel_i;//------------- Receive Ports - RX Fabric Output Control Ports -------------wire gt1_rxoutclk_i;wire gt1_rxoutclkfabric_i;//----------- Receive Ports - RX Initialization and Reset Ports ------------wire gt1_gtrxreset_i;wire gt1_rxpcsreset_i;wire gt1_rxpmareset_i;//---------------- Receive Ports - RX Margin Analysis ports ----------------wire gt1_rxlpmen_i;//--------------- Receive Ports - RX Polarity Control Ports ----------------wire gt1_rxpolarity_i;//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------wire [3:0] gt1_rxchariscomma_i;wire [3:0] gt1_rxcharisk_i;//------------ Receive Ports -RX Initialization and Reset Ports ------------wire gt1_rxresetdone_i;//---------------------- TX Configurable Driver Ports ----------------------wire [4:0] gt1_txpostcursor_i;wire [4:0] gt1_txprecursor_i;//------------------- TX Initialization and Reset Ports --------------------wire gt1_gttxreset_i;wire gt1_txuserrdy_i;//-------------- Transmit Ports - 8b10b Encoder Control Ports --------------wire [3:0] gt1_txchardispmode_i;wire [3:0] gt1_txchardispval_i;//---------------- Transmit Ports - Pattern Generator Ports ----------------wire gt1_txprbsforceerr_i;//-------------------- Transmit Ports - TX Buffer Ports --------------------wire [1:0] gt1_txbufstatus_i;//------------- Transmit Ports - TX Configurable Driver Ports --------------wire [3:0] gt1_txdiffctrl_i;wire [6:0] gt1_txmaincursor_i;//---------------- Transmit Ports - TX Data Path interface -----------------wire [31:0] gt1_txdata_i;//-------------- Transmit Ports - TX Driver and OOB signaling --------------wire gt1_gtxtxn_i;wire gt1_gtxtxp_i;//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------wire gt1_txoutclk_i;wire gt1_txoutclkfabric_i;wire gt1_txoutclkpcs_i;//------------------- Transmit Ports - TX Gearbox Ports --------------------wire [3:0] gt1_txcharisk_i;//----------- Transmit Ports - TX Initialization and Reset Ports -----------wire gt1_txpcsreset_i;wire gt1_txpmareset_i;wire gt1_txresetdone_i;//--------------- Transmit Ports - TX Polarity Control Ports ---------------wire gt1_txpolarity_i;//---------------- Transmit Ports - pattern Generator Ports ----------------wire [2:0] gt1_txprbssel_i;//____________________________COMMON PORTS________________________________//-------------------- Common Block - Ref Clock Ports ---------------------wire gt0_gtrefclk1_common_i;//----------------------- Common Block - QPLL Ports ------------------------wire gt0_qplllock_i;wire gt0_qpllrefclklost_i;wire gt0_qpllreset_i;//----------------------------- Global Signals -----------------------------wire drpclk_in_i;wire DRPCLK_IN;wire gt0_tx_system_reset_c;wire gt0_rx_system_reset_c;wire gt1_tx_system_reset_c;wire gt1_rx_system_reset_c;wire tied_to_ground_i;wire [63:0] tied_to_ground_vec_i;wire tied_to_vcc_i;wire [7:0] tied_to_vcc_vec_i;wire GTTXRESET_IN;wire GTRXRESET_IN;wire QPLLRESET_IN;//--------------------------- User Clocks ---------------------------------wire gt0_txusrclk_i; wire gt0_txusrclk2_i; wire gt0_rxusrclk_i; wire gt0_rxusrclk2_i; wire gt1_txusrclk_i; wire gt1_txusrclk2_i; wire gt1_rxusrclk_i; wire gt1_rxusrclk2_i; wire gt0_txmmcm_lock_i;wire gt0_txmmcm_reset_i;wire gt0_rxmmcm_lock_i; wire gt0_rxmmcm_reset_i;wire gt1_txmmcm_lock_i;wire gt1_txmmcm_reset_i;wire gt1_rxmmcm_lock_i; wire gt1_rxmmcm_reset_i;//--------------------------- Reference Clocks ----------------------------wire q0_clk0_refclk_i;//--------------------- Frame check/gen Module Signals --------------------wire gt0_matchn_i;wire [3:0] gt0_txcharisk_float_i;wire [15:0] gt0_txdata_float16_i;wire [31:0] gt0_txdata_float_i;wire gt0_block_sync_i;wire gt0_track_data_i;wire [7:0] gt0_error_count_i;wire gt0_frame_check_reset_i;wire gt0_inc_in_i;wire gt0_inc_out_i;wire [31:0] gt0_unscrambled_data_i;wire gt1_matchn_i;wire [3:0] gt1_txcharisk_float_i;wire [15:0] gt1_txdata_float16_i;wire [31:0] gt1_txdata_float_i;wire gt1_block_sync_i;wire gt1_track_data_i;wire [7:0] gt1_error_count_i;wire gt1_frame_check_reset_i;wire gt1_inc_in_i;wire gt1_inc_out_i;wire [31:0] gt1_unscrambled_data_i;wire reset_on_data_error_i;wire track_data_out_i;//--------------------- Chipscope Signals ---------------------------------(*mark_debug = "TRUE" *)wire rxresetdone_vio_i;wire [35:0] tx_data_vio_control_i;wire [35:0] rx_data_vio_control_i;wire [35:0] shared_vio_control_i;wire [35:0] ila_control_i;wire [35:0] channel_drp_vio_control_i;wire [35:0] common_drp_vio_control_i;wire [31:0] tx_data_vio_async_in_i;wire [31:0] tx_data_vio_sync_in_i;wire [31:0] tx_data_vio_async_out_i;wire [31:0] tx_data_vio_sync_out_i;wire [31:0] rx_data_vio_async_in_i;wire [31:0] rx_data_vio_sync_in_i;wire [31:0] rx_data_vio_async_out_i;wire [31:0] rx_data_vio_sync_out_i;wire [31:0] shared_vio_in_i;wire [31:0] shared_vio_out_i;wire [163:0] ila_in_i;wire [31:0] channel_drp_vio_async_in_i;wire [31:0] channel_drp_vio_sync_in_i;wire [31:0] channel_drp_vio_async_out_i;wire [31:0] channel_drp_vio_sync_out_i;wire [31:0] common_drp_vio_async_in_i;wire [31:0] common_drp_vio_sync_in_i;wire [31:0] common_drp_vio_async_out_i;wire [31:0] common_drp_vio_sync_out_i;wire [31:0] gt0_tx_data_vio_async_in_i;wire [31:0] gt0_tx_data_vio_sync_in_i;wire [31:0] gt0_tx_data_vio_async_out_i;wire [31:0] gt0_tx_data_vio_sync_out_i;wire [31:0] gt0_rx_data_vio_async_in_i;wire [31:0] gt0_rx_data_vio_sync_in_i;wire [31:0] gt0_rx_data_vio_async_out_i;wire [31:0] gt0_rx_data_vio_sync_out_i;wire [163:0] gt0_ila_in_i;wire [31:0] gt0_channel_drp_vio_async_in_i;wire [31:0] gt0_channel_drp_vio_sync_in_i;wire [31:0] gt0_channel_drp_vio_async_out_i;wire [31:0] gt0_channel_drp_vio_sync_out_i;wire [31:0] gt0_common_drp_vio_async_in_i;wire [31:0] gt0_common_drp_vio_sync_in_i;wire [31:0] gt0_common_drp_vio_async_out_i;wire [31:0] gt0_common_drp_vio_sync_out_i;wire [31:0] gt1_tx_data_vio_async_in_i;wire [31:0] gt1_tx_data_vio_sync_in_i;wire [31:0] gt1_tx_data_vio_async_out_i;wire [31:0] gt1_tx_data_vio_sync_out_i;wire [31:0] gt1_rx_data_vio_async_in_i;wire [31:0] gt1_rx_data_vio_sync_in_i;wire [31:0] gt1_rx_data_vio_async_out_i;wire [31:0] gt1_rx_data_vio_sync_out_i;wire [163:0] gt1_ila_in_i;wire [31:0] gt1_channel_drp_vio_async_in_i;wire [31:0] gt1_channel_drp_vio_sync_in_i;wire [31:0] gt1_channel_drp_vio_async_out_i;wire [31:0] gt1_channel_drp_vio_sync_out_i;wire [31:0] gt1_common_drp_vio_async_in_i;wire [31:0] gt1_common_drp_vio_sync_in_i;wire [31:0] gt1_common_drp_vio_async_out_i;wire [31:0] gt1_common_drp_vio_sync_out_i;wire gttxreset_i;wire gtrxreset_i;wire mux_sel_i;wire user_tx_reset_i;wire user_rx_reset_i;wire tx_vio_clk_i;wire tx_vio_clk_mux_out_i; wire rx_vio_ila_clk_i;wire rx_vio_ila_clk_mux_out_i;wire qpllreset_i;wire [(80 -32) -1:0] zero_vector_rx_80 ;wire [(8 -4) -1:0] zero_vector_rx_8 ;wire [79:0] gt0_rxdata_ila ;wire [1:0] gt0_rxdatavalid_ila; wire [7:0] gt0_rxcharisk_ila ;wire gt0_txmmcm_lock_ila ;wire gt0_rxmmcm_lock_ila ;wire gt0_rxresetdone_ila ;wire gt0_txresetdone_ila ;wire [79:0] gt1_rxdata_ila ;wire [1:0] gt1_rxdatavalid_ila; wire [7:0] gt1_rxcharisk_ila ;wire gt1_txmmcm_lock_ila ;wire gt1_rxmmcm_lock_ila ;wire gt1_rxresetdone_ila ;wire gt1_txresetdone_ila ;//**************************** Main Body of Code *******************************// Static signal Assigments assign tied_to_ground_i = 1'b0;assign tied_to_ground_vec_i = 64'h0000000000000000;assign tied_to_vcc_i = 1'b1;assign tied_to_vcc_vec_i = 8'hff;assign zero_vector_rx_80 = 0;assign zero_vector_rx_8 = 0;assign q0_clk0_refclk_i = 1'b0;//***********************************************************************//// ////--------------------------- The GT Wrapper ----------------------------//// ////***********************************************************************//// Use the instantiation template in the example directory to add the GT wrapper to your design.// In this example, the wrapper is wired up for basic operation with a frame generator and frame // checker. The GTs will reset, then attempt to align and transmit data. If channel bonding is // enabled, bonding should occur after alignment.// While connecting the GT TX/RX Reset ports below, please add a delay of// minimum 500ns as mentioned in AR 43482.gtwizard_0_support #(.EXAMPLE_SIM_GTRESET_SPEEDUP ("FALSE"),.STABLE_CLOCK_PERIOD (10))gtwizard_0_support_i(.soft_reset_tx_in (soft_reset_i),.soft_reset_rx_in (soft_reset_i),.dont_reset_on_data_error_in (tied_to_ground_i),.q0_clk0_gtrefclk_pad_n_in(Q0_CLK0_GTREFCLK_PAD_N_IN),.q0_clk0_gtrefclk_pad_p_in(Q0_CLK0_GTREFCLK_PAD_P_IN),.gt0_tx_mmcm_lock_out (gt0_txmmcm_lock_i),.gt0_rx_mmcm_lock_out (gt0_rxmmcm_lock_i),.gt0_tx_fsm_reset_done_out (gt0_txfsmresetdone_i),.gt0_rx_fsm_reset_done_out (gt0_rxfsmresetdone_i),.gt0_data_valid_in (1'b1),.gt1_tx_mmcm_lock_out (gt1_txmmcm_lock_i),.gt1_rx_mmcm_lock_out (gt1_rxmmcm_lock_i),.gt1_tx_fsm_reset_done_out (gt1_txfsmresetdone_i),.gt1_rx_fsm_reset_done_out (gt1_rxfsmresetdone_i),.gt1_data_valid_in (1'b1),.gt0_txusrclk_out(gt0_txusrclk_i),.gt0_txusrclk2_out(gt0_txusrclk2_i),.gt0_rxusrclk_out(gt0_rxusrclk_i),.gt0_rxusrclk2_out(gt0_rxusrclk2_i),.gt1_txusrclk_out(gt1_txusrclk_i),.gt1_txusrclk2_out(gt1_txusrclk2_i),.gt1_rxusrclk_out(gt1_rxusrclk_i),.gt1_rxusrclk2_out(gt1_rxusrclk2_i),//_____________________________________________________________________//_____________________________________________________________________//GT0 (X1Y0)//-------------------------- Channel - DRP Ports --------------------------.gt0_drpaddr_in (gt0_drpaddr_i),.gt0_drpdi_in (gt0_drpdi_i),.gt0_drpdo_out (gt0_drpdo_i),.gt0_drpen_in (gt0_drpen_i),.gt0_drprdy_out (gt0_drprdy_i),.gt0_drpwe_in (gt0_drpwe_i),//------------------------- Digital Monitor Ports --------------------------.gt0_dmonitorout_out (gt0_dmonitorout_i),//----------------------------- Loopback Ports -----------------------------.gt0_loopback_in (gt0_loopback_i),//---------------------------- Power-Down Ports ----------------------------.gt0_rxpd_in (gt0_rxpd_i),.gt0_txpd_in (gt0_txpd_i),//------------------- RX Initialization and Reset Ports --------------------.gt0_eyescanreset_in (tied_to_ground_i),.gt0_rxuserrdy_in (tied_to_vcc_i),//------------------------ RX Margin Analysis Ports ------------------------.gt0_eyescandataerror_out (gt0_eyescandataerror_i),.gt0_eyescantrigger_in (tied_to_ground_i),//----------------------- Receive Ports - CDR Ports ------------------------.gt0_rxcdrhold_in (gt0_rxcdrhold_i),.gt0_rxcdrovrden_in (tied_to_ground_i),//----------------- Receive Ports - Clock Correction Ports -----------------.gt0_rxclkcorcnt_out (gt0_rxclkcorcnt_i),//---------------- Receive Ports - FPGA RX interface Ports -----------------.gt0_rxdata_out (gt0_rxdata_i),//----------------- Receive Ports - Pattern Checker Ports ------------------.gt0_rxprbserr_out (gt0_rxprbserr_i),.gt0_rxprbssel_in (gt0_rxprbssel_i),//----------------- Receive Ports - Pattern Checker ports ------------------.gt0_rxprbscntreset_in (gt0_rxprbscntreset_i),//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------.gt0_rxdisperr_out (gt0_rxdisperr_i),.gt0_rxnotintable_out (gt0_rxnotintable_i),//------------------------- Receive Ports - RX AFE -------------------------.gt0_gtxrxp_in (RXP_IN[0]),//---------------------- Receive Ports - RX AFE Ports ----------------------.gt0_gtxrxn_in (RXN_IN[0]),//----------------- Receive Ports - RX Buffer Bypass Ports -----------------.gt0_rxbufreset_in (gt0_rxbufreset_i),.gt0_rxbufstatus_out (gt0_rxbufstatus_i),//------------ Receive Ports - RX Byte and Word Alignment Ports ------------.gt0_rxbyteisaligned_out (gt0_rxbyteisaligned_i),.gt0_rxbyterealign_out (gt0_rxbyterealign_i),.gt0_rxcommadet_out (gt0_rxcommadet_i),.gt0_rxmcommaalignen_in (1'b1),.gt0_rxpcommaalignen_in (1'b1),//------------------- Receive Ports - RX Equalizer Ports -------------------.gt0_rxdfelpmreset_in (tied_to_ground_i),.gt0_rxmonitorout_out (gt0_rxmonitorout_i),.gt0_rxmonitorsel_in (2'b00),//------------- Receive Ports - RX Fabric Output Control Ports -------------.gt0_rxoutclkfabric_out (gt0_rxoutclkfabric_i),//----------- Receive Ports - RX Initialization and Reset Ports ------------.gt0_gtrxreset_in (tied_to_ground_i),.gt0_rxpcsreset_in (tied_to_ground_i),.gt0_rxpmareset_in (gt0_rxpmareset_i),//---------------- Receive Ports - RX Margin Analysis ports ----------------.gt0_rxlpmen_in (gt0_rxlpmen_i),//--------------- Receive Ports - RX Polarity Control Ports ----------------.gt0_rxpolarity_in (gt0_rxpolarity_i),//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------.gt0_rxchariscomma_out (gt0_rxchariscomma_i),.gt0_rxcharisk_out (gt0_rxcharisk_i),//------------ Receive Ports -RX Initialization and Reset Ports ------------.gt0_rxresetdone_out (gt0_rxresetdone_i),//---------------------- TX Configurable Driver Ports ----------------------.gt0_txpostcursor_in (gt0_txpostcursor_i),.gt0_txprecursor_in (gt0_txprecursor_i),//------------------- TX Initialization and Reset Ports --------------------.gt0_gttxreset_in (tied_to_ground_i),.gt0_txuserrdy_in (tied_to_vcc_i),//-------------- Transmit Ports - 8b10b Encoder Control Ports --------------.gt0_txchardispmode_in (gt0_txchardispmode_i),.gt0_txchardispval_in (gt0_txchardispval_i),//---------------- Transmit Ports - Pattern Generator Ports ----------------.gt0_txprbsforceerr_in (gt0_txprbsforceerr_i),//-------------------- Transmit Ports - TX Buffer Ports --------------------.gt0_txbufstatus_out (gt0_txbufstatus_i),//------------- Transmit Ports - TX Configurable Driver Ports --------------.gt0_txdiffctrl_in (gt0_txdiffctrl_i),.gt0_txmaincursor_in (7'b0000000),//---------------- Transmit Ports - TX Data Path interface -----------------.gt0_txdata_in (gt0_txdata_i),//-------------- Transmit Ports - TX Driver and OOB signaling --------------.gt0_gtxtxn_out (TXN_OUT[0]),.gt0_gtxtxp_out (TXP_OUT[0]),//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------.gt0_txoutclkfabric_out (gt0_txoutclkfabric_i),.gt0_txoutclkpcs_out (gt0_txoutclkpcs_i),//------------------- Transmit Ports - TX Gearbox Ports --------------------.gt0_txcharisk_in (gt0_txcharisk_i),//----------- Transmit Ports - TX Initialization and Reset Ports -----------.gt0_txpcsreset_in (tied_to_ground_i),.gt0_txpmareset_in (tied_to_ground_i),.gt0_txresetdone_out (gt0_txresetdone_i),//--------------- Transmit Ports - TX Polarity Control Ports ---------------.gt0_txpolarity_in (gt0_txpolarity_i),//---------------- Transmit Ports - pattern Generator Ports ----------------.gt0_txprbssel_in (gt0_txprbssel_i),//_____________________________________________________________________//_____________________________________________________________________//GT1 (X1Y3)//-------------------------- Channel - DRP Ports --------------------------.gt1_drpaddr_in (gt1_drpaddr_i),.gt1_drpdi_in (gt1_drpdi_i),.gt1_drpdo_out (gt1_drpdo_i),.gt1_drpen_in (gt1_drpen_i),.gt1_drprdy_out (gt1_drprdy_i),.gt1_drpwe_in (gt1_drpwe_i),//------------------------- Digital Monitor Ports --------------------------.gt1_dmonitorout_out (gt1_dmonitorout_i),//----------------------------- Loopback Ports -----------------------------.gt1_loopback_in (gt1_loopback_i),//---------------------------- Power-Down Ports ----------------------------.gt1_rxpd_in (gt1_rxpd_i),.gt1_txpd_in (gt1_txpd_i),//------------------- RX Initialization and Reset Ports --------------------.gt1_eyescanreset_in (tied_to_ground_i),.gt1_rxuserrdy_in (tied_to_vcc_i),//------------------------ RX Margin Analysis Ports ------------------------.gt1_eyescandataerror_out (gt1_eyescandataerror_i),.gt1_eyescantrigger_in (tied_to_ground_i),//----------------------- Receive Ports - CDR Ports ------------------------.gt1_rxcdrhold_in (gt1_rxcdrhold_i),.gt1_rxcdrovrden_in (tied_to_ground_i),//----------------- Receive Ports - Clock Correction Ports -----------------.gt1_rxclkcorcnt_out (gt1_rxclkcorcnt_i),//---------------- Receive Ports - FPGA RX interface Ports -----------------.gt1_rxdata_out (gt1_rxdata_i),//----------------- Receive Ports - Pattern Checker Ports ------------------.gt1_rxprbserr_out (gt1_rxprbserr_i),.gt1_rxprbssel_in (gt1_rxprbssel_i),//----------------- Receive Ports - Pattern Checker ports ------------------.gt1_rxprbscntreset_in (gt1_rxprbscntreset_i),//---------------- Receive Ports - RX 8B/10B Decoder Ports -----------------.gt1_rxdisperr_out (gt1_rxdisperr_i),.gt1_rxnotintable_out (gt1_rxnotintable_i),//------------------------- Receive Ports - RX AFE -------------------------.gt1_gtxrxp_in (RXP_IN[1]),//---------------------- Receive Ports - RX AFE Ports ----------------------.gt1_gtxrxn_in (RXN_IN[1]),//----------------- Receive Ports - RX Buffer Bypass Ports -----------------.gt1_rxbufreset_in (gt1_rxbufreset_i),.gt1_rxbufstatus_out (gt1_rxbufstatus_i),//------------ Receive Ports - RX Byte and Word Alignment Ports ------------.gt1_rxbyteisaligned_out (gt1_rxbyteisaligned_i),.gt1_rxbyterealign_out (gt1_rxbyterealign_i),.gt1_rxcommadet_out (gt1_rxcommadet_i),.gt1_rxmcommaalignen_in (1'b1),.gt1_rxpcommaalignen_in (1'b1),//------------------- Receive Ports - RX Equalizer Ports -------------------.gt1_rxdfelpmreset_in (tied_to_ground_i),.gt1_rxmonitorout_out (gt1_rxmonitorout_i),.gt1_rxmonitorsel_in (2'b00),//------------- Receive Ports - RX Fabric Output Control Ports -------------.gt1_rxoutclkfabric_out (gt1_rxoutclkfabric_i),//----------- Receive Ports - RX Initialization and Reset Ports ------------.gt1_gtrxreset_in (tied_to_ground_i),.gt1_rxpcsreset_in (tied_to_ground_i),.gt1_rxpmareset_in (gt1_rxpmareset_i),//---------------- Receive Ports - RX Margin Analysis ports ----------------.gt1_rxlpmen_in (gt1_rxlpmen_i),//--------------- Receive Ports - RX Polarity Control Ports ----------------.gt1_rxpolarity_in (gt1_rxpolarity_i),//----------------- Receive Ports - RX8B/10B Decoder Ports -----------------.gt1_rxchariscomma_out (gt1_rxchariscomma_i),.gt1_rxcharisk_out (gt1_rxcharisk_i),//------------ Receive Ports -RX Initialization and Reset Ports ------------.gt1_rxresetdone_out (gt1_rxresetdone_i),//---------------------- TX Configurable Driver Ports ----------------------.gt1_txpostcursor_in (gt1_txpostcursor_i),.gt1_txprecursor_in (gt1_txprecursor_i),//------------------- TX Initialization and Reset Ports --------------------.gt1_gttxreset_in (tied_to_ground_i),.gt1_txuserrdy_in (tied_to_vcc_i),//-------------- Transmit Ports - 8b10b Encoder Control Ports --------------.gt1_txchardispmode_in (gt1_txchardispmode_i),.gt1_txchardispval_in (gt1_txchardispval_i),//---------------- Transmit Ports - Pattern Generator Ports ----------------.gt1_txprbsforceerr_in (gt1_txprbsforceerr_i),//-------------------- Transmit Ports - TX Buffer Ports --------------------.gt1_txbufstatus_out (gt1_txbufstatus_i),//------------- Transmit Ports - TX Configurable Driver Ports --------------.gt1_txdiffctrl_in (gt1_txdiffctrl_i),.gt1_txmaincursor_in (7'b0000000),//---------------- Transmit Ports - TX Data Path interface -----------------.gt1_txdata_in (gt1_txdata_i),//-------------- Transmit Ports - TX Driver and OOB signaling --------------.gt1_gtxtxn_out (TXN_OUT[1]),.gt1_gtxtxp_out (TXP_OUT[1]),//--------- Transmit Ports - TX Fabric Clock Output Control Ports ----------.gt1_txoutclkfabric_out (gt1_txoutclkfabric_i),.gt1_txoutclkpcs_out (gt1_txoutclkpcs_i),//------------------- Transmit Ports - TX Gearbox Ports --------------------.gt1_txcharisk_in (gt1_txcharisk_i),//----------- Transmit Ports - TX Initialization and Reset Ports -----------.gt1_txpcsreset_in (tied_to_ground_i),.gt1_txpmareset_in (tied_to_ground_i),.gt1_txresetdone_out (gt1_txresetdone_i),//--------------- Transmit Ports - TX Polarity Control Ports ---------------.gt1_txpolarity_in (gt1_txpolarity_i),//---------------- Transmit Ports - pattern Generator Ports ----------------.gt1_txprbssel_in (gt1_txprbssel_i),//____________________________COMMON PORTS________________________________.gt0_qplllock_out(),.gt0_qpllrefclklost_out(),.gt0_qplloutclk_out(),.gt0_qplloutrefclk_out(),.sysclk_in(drpclk_in_i));always @(posedge gt0_rxusrclk2_i or negedge gt0_rxresetdone_i)beginif (!gt0_rxresetdone_i)begingt0_rxresetdone_r <= `DLY 1'b0;gt0_rxresetdone_r2 <= `DLY 1'b0;gt0_rxresetdone_r3 <= `DLY 1'b0;endelsebegingt0_rxresetdone_r <= `DLY gt0_rxresetdone_i;gt0_rxresetdone_r2 <= `DLY gt0_rxresetdone_r;gt0_rxresetdone_r3 <= `DLY gt0_rxresetdone_r2;endendalways @(posedge gt0_txusrclk2_i or negedge gt0_txfsmresetdone_i)beginif (!gt0_txfsmresetdone_i)begingt0_txfsmresetdone_r <= `DLY 1'b0;gt0_txfsmresetdone_r2 <= `DLY 1'b0;endelsebegingt0_txfsmresetdone_r <= `DLY gt0_txfsmresetdone_i;gt0_txfsmresetdone_r2 <= `DLY gt0_txfsmresetdone_r;endendalways @(posedge gt1_rxusrclk2_i or negedge gt1_rxresetdone_i)beginif (!gt1_rxresetdone_i)begingt1_rxresetdone_r <= `DLY 1'b0;gt1_rxresetdone_r2 <= `DLY 1'b0;gt1_rxresetdone_r3 <= `DLY 1'b0;endelsebegingt1_rxresetdone_r <= `DLY gt1_rxresetdone_i;gt1_rxresetdone_r2 <= `DLY gt1_rxresetdone_r;gt1_rxresetdone_r3 <= `DLY gt1_rxresetdone_r2;endendalways @(posedge gt1_txusrclk2_i or negedge gt1_txfsmresetdone_i)beginif (!gt1_txfsmresetdone_i)begingt1_txfsmresetdone_r <= `DLY 1'b0;gt1_txfsmresetdone_r2 <= `DLY 1'b0;endelsebegingt1_txfsmresetdone_r <= `DLY gt1_txfsmresetdone_i;gt1_txfsmresetdone_r2 <= `DLY gt1_txfsmresetdone_r;endend//------------ optional Ports assignments --------------

assign gt0_rxprbscntreset_i = tied_to_ground_i;

assign gt0_rxprbssel_i = 0;

assign gt0_loopback_i = 0;assign gt0_txdiffctrl_i = 0;

assign gt0_rxbufreset_i = tied_to_ground_i;

assign gt0_rxcdrhold_i = tied_to_ground_i;//------GTH/GTP

assign gt0_rxdfelpmreset_i = tied_to_ground_i;

assign gt0_rxpmareset_i = tied_to_ground_i;

assign gt0_rxpolarity_i = tied_to_ground_i;

assign gt0_rxpd_i = 0;

assign gt0_txprecursor_i = 0;

assign gt0_txpostcursor_i = 0;

assign gt0_txchardispmode_i = 0;

assign gt0_txchardispval_i = 0;

assign gt0_txpolarity_i = tied_to_ground_i;

assign gt0_txpd_i = 0;

assign gt0_txprbsforceerr_i = tied_to_ground_i;

assign gt0_txprbssel_i = 0;

assign gt1_rxprbscntreset_i = tied_to_ground_i;

assign gt1_rxprbssel_i = 0;

assign gt1_loopback_i = 0;assign gt1_txdiffctrl_i = 0;

assign gt1_rxbufreset_i = tied_to_ground_i;

assign gt1_rxcdrhold_i = tied_to_ground_i;//------GTH/GTP

assign gt1_rxdfelpmreset_i = tied_to_ground_i;

assign gt1_rxpmareset_i = tied_to_ground_i;

assign gt1_rxpolarity_i = tied_to_ground_i;

assign gt1_rxpd_i = 0;

assign gt1_txprecursor_i = 0;

assign gt1_txpostcursor_i = 0;

assign gt1_txchardispmode_i = 0;

assign gt1_txchardispval_i = 0;

assign gt1_txpolarity_i = tied_to_ground_i;

assign gt1_txpd_i = 0;

assign gt1_txprbsforceerr_i = tied_to_ground_i;

assign gt1_txprbssel_i = 0;

assign gt0_drpaddr_i = 9'd0;

assign gt0_drpdi_i = 16'd0;

assign gt0_drpen_i = 1'b0;

assign gt0_drpwe_i = 1'b0;

assign gt1_drpaddr_i = 9'd0;

assign gt1_drpdi_i = 16'd0;

assign gt1_drpen_i = 1'b0;

assign gt1_drpwe_i = 1'b0;

assign soft_reset_i = tied_to_ground_i;

endmodule

可以对照官方源码,看看去掉了哪些添加了哪些,不懂的可以找我问问~~

4.GTX收发数据编解码讲解

下一步就是添加自定义代码了,需要添加如下代码模块:

数据对齐模块;

数据编码模块;

数据解码模块;

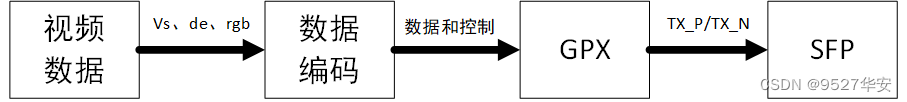

数据编码模块和GTX的应用部分如下:

视频数据经过数据编码模块,变为有固定格式的数据帧,同时伴随着控制信号;

数据帧格式如下:(可自定义)

parameter VS_START_0 = 32'h55_00_00_bc, //发送场同步开始帧头0parameter VS_START_1 = 32'h55_00_01_bc, //发送场同步开始帧头0parameter UNUSE_DATA_0 = 32'h55_00_02_bc, //发送无效数据0parameter UNUSE_DATA_1 = 32'h55_00_03_bc, //发送无效数据1parameter OK_DATA_START = 32'h55_00_04_bc, //发送有效数据开始parameter OK_DATA_END = 32'h55_00_05_bc, //发送有效数据结束parameter VS_END_0 = 32'h55_00_06_bc, //发送场同步结束帧尾0parameter VS_END_1 = 32'h55_00_07_bc, //发送场同步结束帧尾1

视频数据进来时是以hs、vs、de和rgb的格式,但GTX不管你这些,他发出去的数据是高速串行的差分信号,所以数据在进入GTX之前必须做如下处理:

1、24位的rgb数据先转为16位,再由16位转为32位;因为GTX的发送入口时32位;

2、将视频数据的vs、de和rgb处理为32位的并行数据,准备送入GTX的发送接口;

3、使用1个fifo实现16位转为32位;

利用上面的帧格式,就可以是原始的视频数据变为32位的并行数据了,

具体怎么实现的,粘贴一段状态机中的代码应该就由眉目了:

case(state)frame_sys0:begin //发送帧同步信号55_00_00_bcstate <= frame_sys1;coded_data <= VS_START_0;coded_ctr <= 4'b0001;endframe_sys1:begin //发送帧同步信号55_00_01_bcstate <= unuse_data0;coded_data <= VS_START_1;coded_ctr <= 4'b0001;endunuse_data0:begin //发送无用的信号55_00_02_bc state <= unuse_data1;coded_data <= UNUSE_DATA_0;coded_ctr <= 4'b0001;endunuse_data1:begin //发送无用的信号55_00_03_bc if(coded_data_count >= FIFO_VTH_SET) state <= h_data_begin; //当FIFO 中有一行数据 else beginstate <= unuse_data0;coded_data<= UNUSE_DATA_1;end end

也就是说:将vs的上下沿转化为了控制帧;同时伴随着4位的coded_ctr;由于代码太长,这里不方便全部给出,需要源码的兄弟可以找我;

数据编码模块和GTX的应用部分如下:

这部分是整个工程的重点:

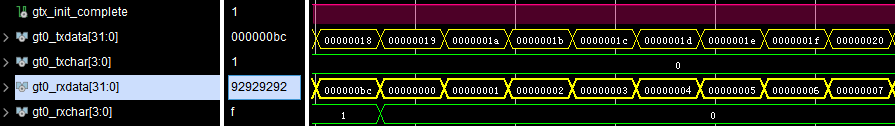

GTX串并转换后得到32位的并行数据,但这个数据经过5.94G的高速传输后有可能出现数据错位的情况,这时数据对齐模块的作用就来了;

本模块将gtx接收后的数据利用k码进行对齐,通过逻辑分析仪抓取调试过程中,有时候会出现,发送的32位数据可能出现16位数据移位,也就是上一个32位的数据低16位可能和下一个32位数据的高16位拼接在一起,我们如何知道我们发出的数据,通过光纤传输接收后进行了错位,此时就轮到K码大显威力了,当我们接收的数据错位时,K码也会错位,此前我们发送的0001 ,可能会变为0100,然后我们根据这个0100来把接收到的数据重新组合,就可以得到正确的结果;

下面给出该部分的核心代码:

always@(posedge rx_clk or negedge rst_n) beginif(!rst_n) rx_data_align <= 32'd0;else begincase(align_bit)4'b0001: rx_data_align <= rx_data;//没错位直接赋值4'b0100: rx_data_align <= {rx_data[15:0],rx_data_r[31:16]};//错位进行拼接default: rx_data_align <= 32'd0;endcaseend

end

数据解码:

这部分的所用是根据之前的数据帧格式,还原出32位并行数据的vs、de和rgb888数据,相当于是数据编码的反向过程;同理,也需要一个fifo做数据位宽转换;

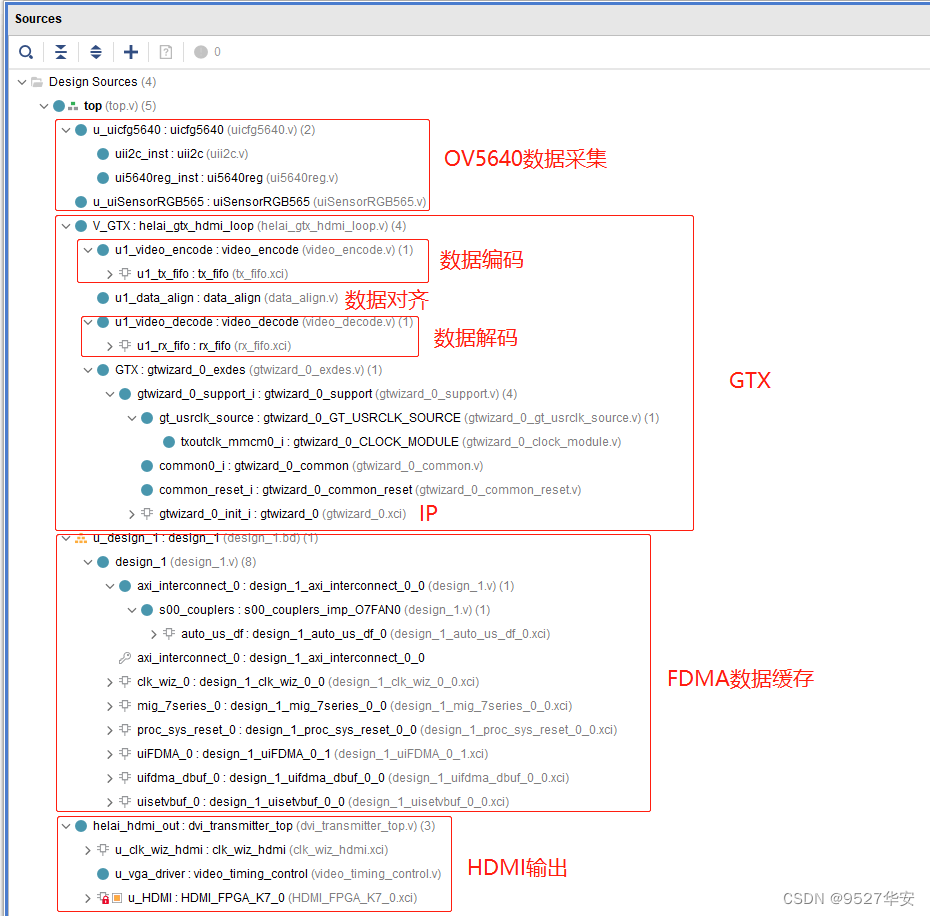

5.工程1介绍:OV5640转GTX

开发板:Kintex7开发板;

开发环境:vivado2019.1;

输入:OV5640,720P,RGB888视频格式;

输出:HDMI输出,720P;

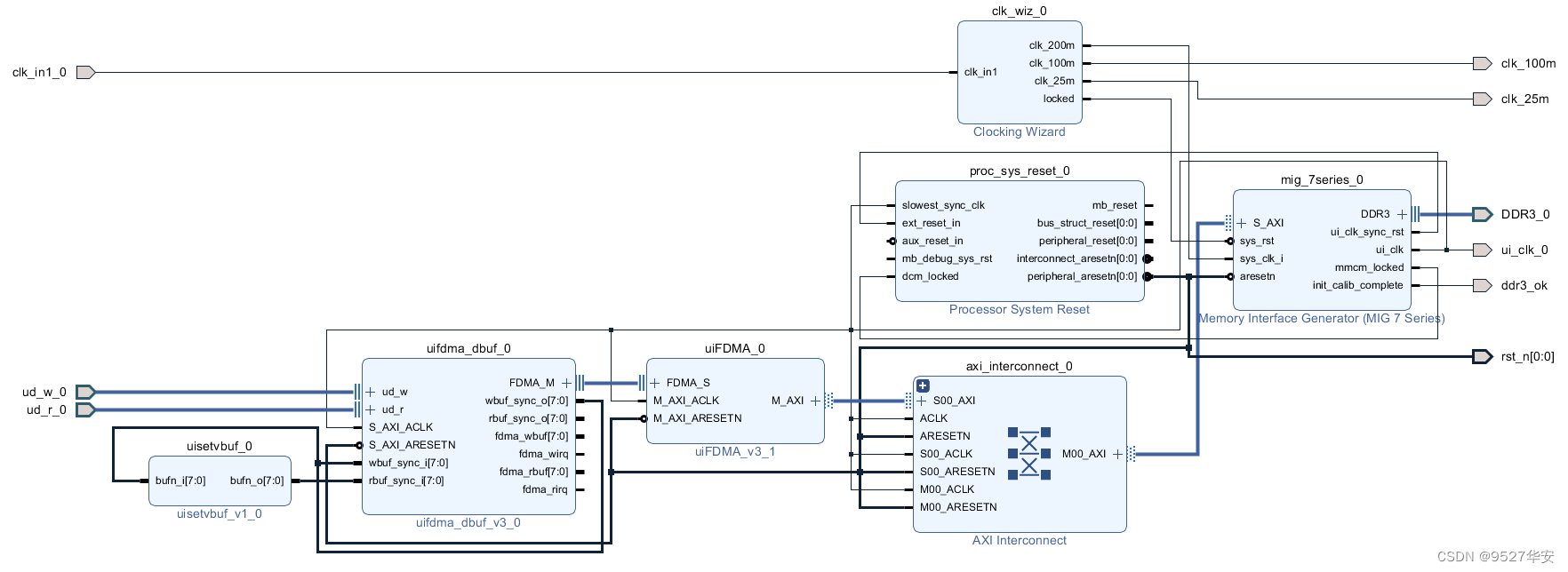

工程BD如下:

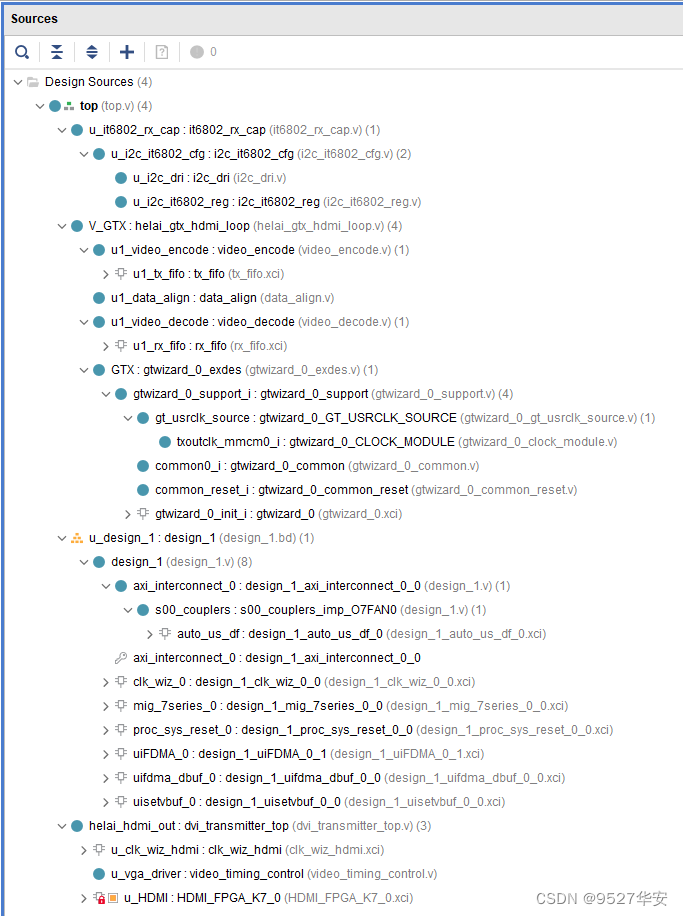

工程代码架构如下:

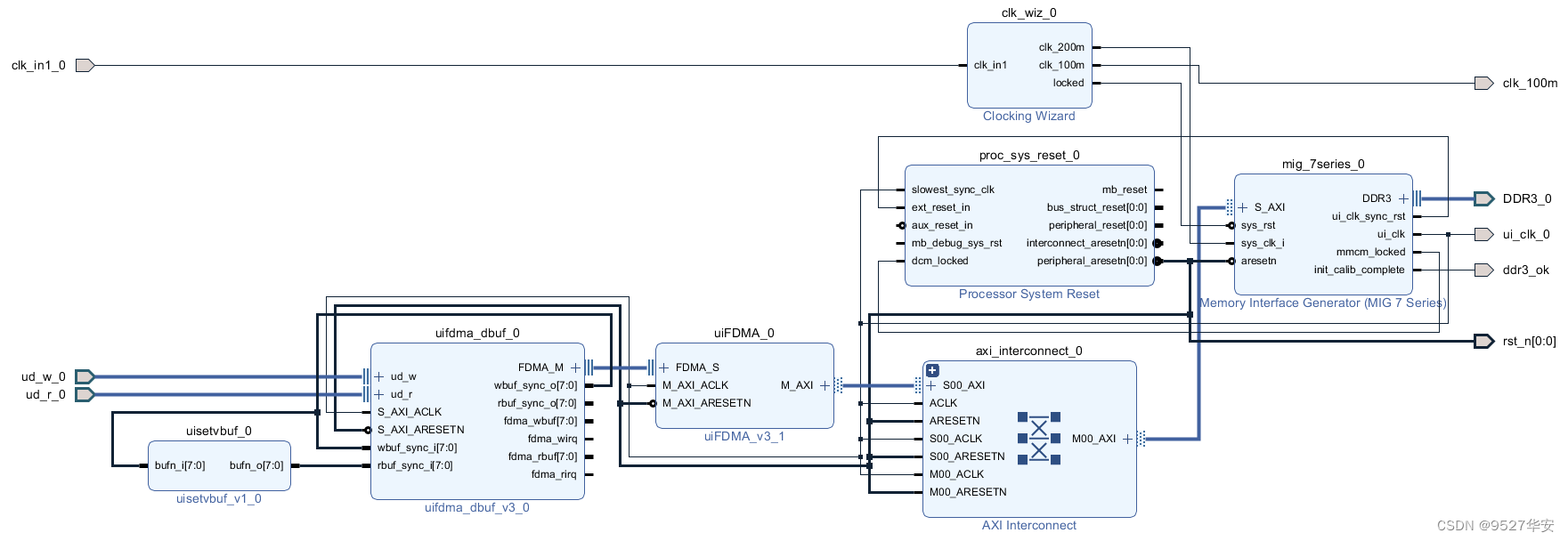

6.工程2介绍:HDMI转GTX

开发板:Kintex7开发板;

开发环境:vivado2019.1;

输入:HDMI输入,1080P,RGB888视频格式;

输出:HDMI输出,1080P;

工程BD如下:

工程代码架构如下:

7.上板调试

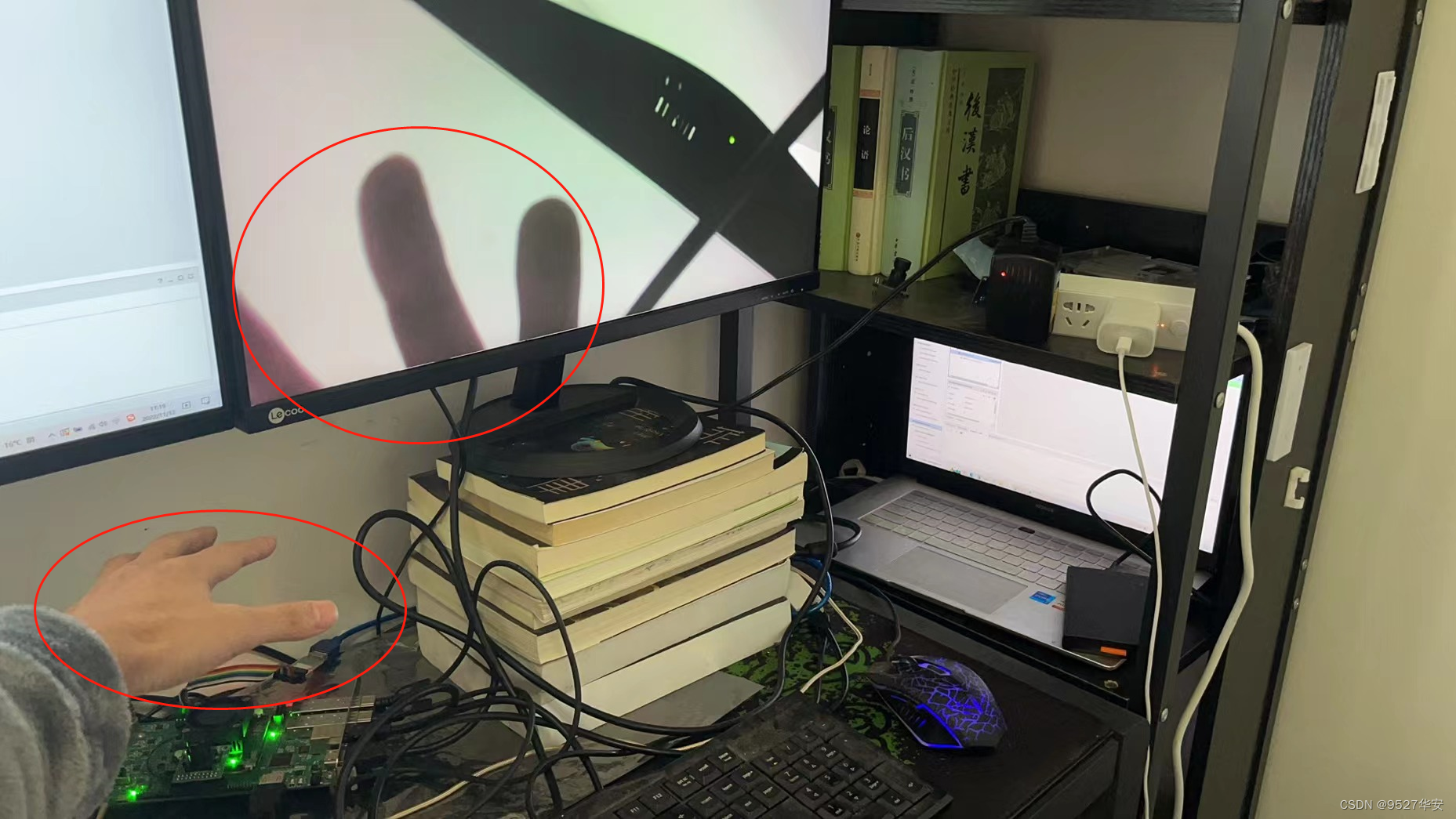

OV5640输出结果:

8.福利领取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下: