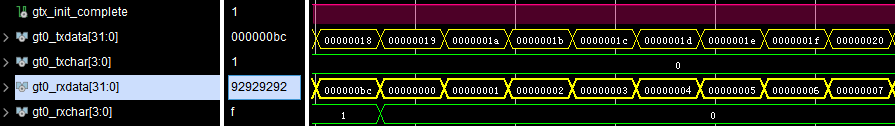

Xilinx GTX/GTH时钟篇(7系列)

时钟选择是整个GTX使用的重点,通常调试出现问题很多原因都是出现在时钟方面。这个章节描述GTH时钟的重点内容。

GTH可以使用相邻QUAD的参考时钟,如下图所示QUAD2可以使用QUAD1和QUAD3的参考时钟。

一个QUAD的时钟系统如下图所示。

时钟的独立性:TX/RX的时钟独立,channel 时钟的独立,QUAD时钟的独立。

时钟的可选择性:TX/RX的时钟可选,channel 时钟的可选,QUAD时钟的可选。

CPLL通常用于低速率传输通常在3.125G以下,QPLL通常用于高速率传输,QPLL的时钟更加精确,原则是能用QPLL就不用CPLL。

时钟的选择以QPLL为例子

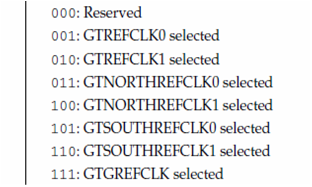

CPLLREFCLKSEL[2:0]/QPLLREFCLKSEL[2:0]

这里有一点需要注意的是:VIVADO2017.4 及其后续版本的VIVADO的软件中

如果你选择GTNORTHREFCLK0/ GTREFCLK0/ GTSOUTHREFCLK0

则GT中CPLLREFCLKSEL[2:0]/QPLLREFCLKSEL[2:0]的值等于“001”;

如果你选择GTNORTHREFCLK1/ GTREFCLK1/ GTSOUTHREFCLK1

则CPLLREFCLKSEL[2:0]/QPLLREFCLKSEL[2:0]的值等于“010”

也是就说在新版的VIVADO软件中CPLLREFCLKSEL[2:0]/QPLLREFCLKSEL[2:0]的值只区分参考时钟是“1”或者是“0”。总之按照实际的时钟路由选择相应的时钟即可

下面这张图是我自己整合了GTH中文档的多个时钟系统所画,描述时钟路由的具体选择,子时钟的产生以及使用。

接下来讲GTH用户时钟产生和分配

以TX为例子RX也类似

TXOUTCLK通常作为txusrclk2的时钟源

TXOUTCLKSEL :通常默认为3‘b010,选择 TXOUTCLKPMA作为时钟源,那么用户时钟和PMA的时钟就是同一个时钟域,并且是同源时钟。只有当TX BUFF被禁用时才选择3’b011 or 3’b100。

TXUSRCLK 与TXUSRCLK2必须时上升沿对齐,并且具备最小的偏斜。用low-skew的时钟资源如BUFG, BUFGs, BUFHs, andBUFRs等驱动TXUSRCLK 和TXUSRCLK2。

TXUSRCLK 与TXUSRCLK2必须同源。

第一种

the frequency of TXUSRCLK2 is equal to TXUSRCLK

第二种

the frequency of TXUSRCLK2 is equal to half of the frequency of TXUSRCLK

通常我们在使用GTH时都不关注这些内容,这些内容是生成GTH时的默认情况。我的一个项目中客户要求了GTH的动态配置(DRP)时,才深入的了解了这个知识点。