1.下载并安装ISE

- 官网下载ISE安装包,Xilinx主页选择Download,之后选择ise archive,选择14.7,下载如下链接。

解压后以管理员身份运行,并接受相关协议,选择System Edition并选择自己的安装路径,路径不能有中文。

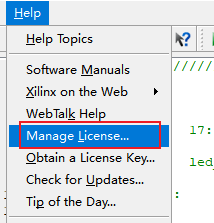

2.获取license文件,将准备好的license文件通过license管理工具添加,打开工具应选择“Locate Existing License(s)”,在第二页选择“Load license”,load准备好的文件即可。

3.解决闪退的问题(不兼容)。ISE14.7同win10 64位存在不兼容的现象,可能会出现闪退的情况,有时license管理工具也会异常。可以在开始屏幕中选择32bit环境打开。或者采用如下方式,使其兼容64bit环境。

①在安装目录.\Xilinx\14.7\ISE_DS\ISE\lib\nt64下,将文件“libPortability.dll”重命名为“libPortability.dll.old”,对文件“libPortabilityNOSH.dll"进行复制粘贴操作,将产生的副本重命名为”libPortability.dll”

②在安装目录.\Xilinx\14.7\ISE_DS\common\lib\nt64下,将文件”libPortability.dll“重命名为”libPortability.dll.old”

③将目录.\Xilinx\14.7\ISE_DS\ISE\lib\nt64下的文件”libPortability.dll“复制

粘贴到目录.\Xilinx\14.7\ISE_DS\common\lib\nt64下

2.创建工程生成bit文件

以使一个led以0.5s为周期闪烁创建第一个ISE工程。

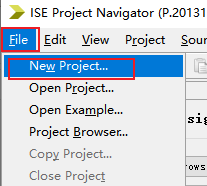

- 打开ISE软件,选择File—New Project创建工程。

2. 输入工程名并选择路径

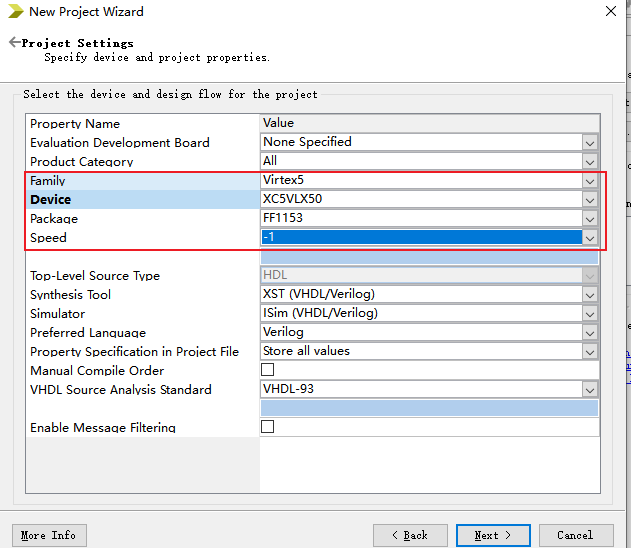

3.选择FPGA芯片型号 包括芯片所属系列(family),具体型号(device),封装类型(package),速度等级(speed),以及综合工具,仿真器,首选语言等。

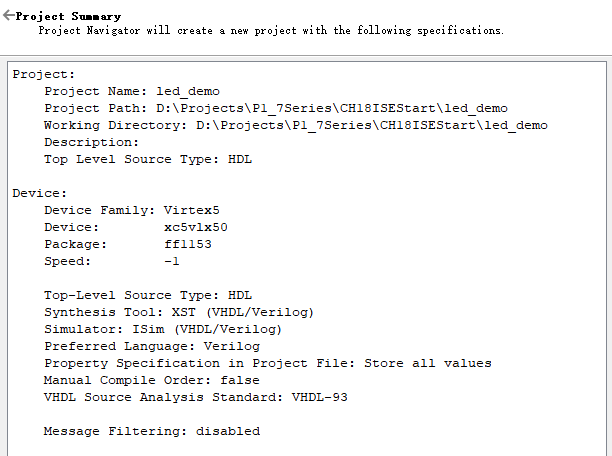

4.project summary概述工程配置。

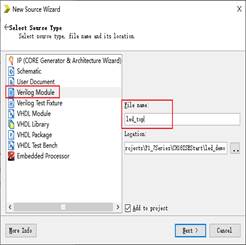

5.添加源文件,使用verilog语言则选verilog module,并输入该文件名。

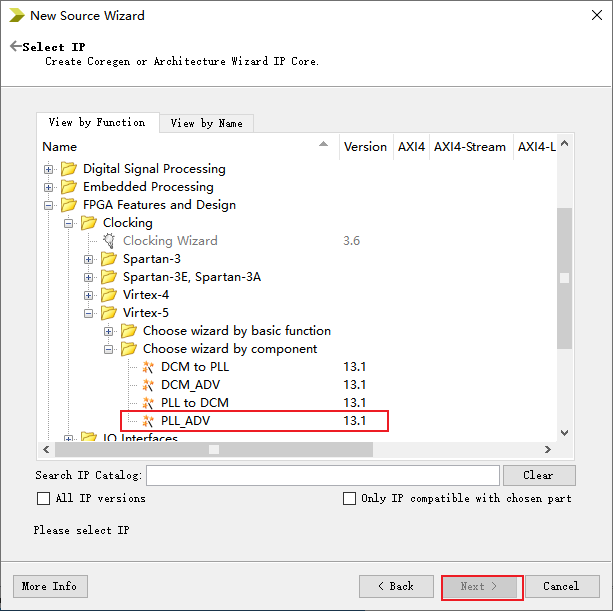

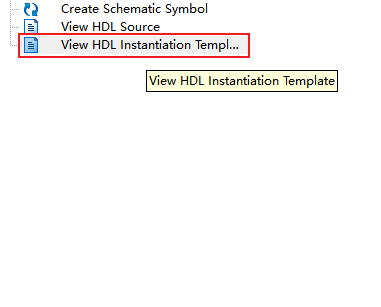

6.添加IP核,同上述步骤5,在第二图中选择IP即可。此处需要注意,xilinx的早期器件只能使用ISE开发,这也是ISE仍然存在的原因。而早期器件有些现在7系列支持的IP是不支持的。如下所示为PLL_ADV IP,用来给时钟分倍频,类似于7系列的clock wizard IP。ISE的风格如下。生成IP后在design面板可以查看IP例化模板。

7.在led_top源文件中输入以下代码

odule led_top(input clk_50o,output led);wire clk_200;wire clk_locked;// Instantiate the module

clk_tree my_clk (.CLKIN1_IN(clk_50o), .RST_IN(1'b0), .CLKOUT0_OUT(clk_200), .LOCKED_OUT(clk_locked));reg [27:0] led_cnt;always@(posedge clk_200 or negedge clk_locked)beginif(!clk_locked)led_cnt <= 28'd0;else if(led_cnt == 28'd200_000_000)led_cnt <= 0;else led_cnt <= led_cnt + 1'b1;endassign led = (led_cnt <= 28'd100_000_000) ? 1'b0 : 1'b1;

endmodule8.添加约束文件,可通过如下图形化配置。

也可通过编写ucf文件,如下:

NET "clk_50o" LOC = AG21;

NET "clk_50o" IOSTANDARD = LVCMOS25;

TIMESPEC TS_clk_50o = PERIOD "clk_50o" 20 ns HIGH 50 %;

# PlanAhead Generated physical constraints

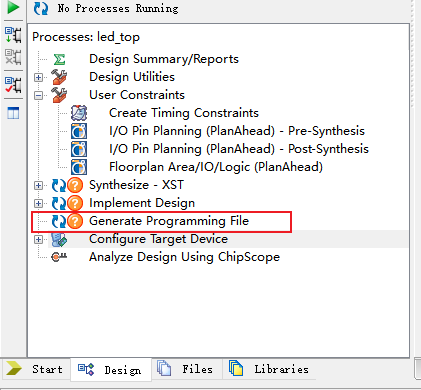

NET "led" LOC = AK19;9.双击Generate programming file,功能与vivado中的generate bitstream一致。

编译成功,则会显示

3.烧写文件

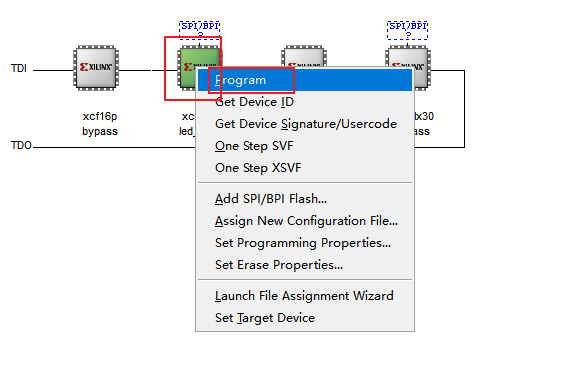

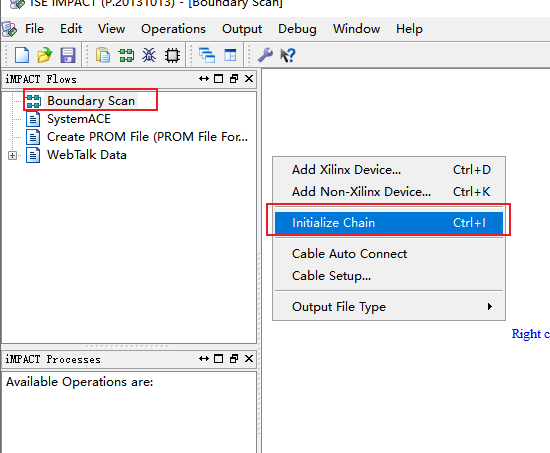

1.双击configure target device,随后对话框选ok。

2.双击Boundary Scan,连接下载器和电源,随后单击右键,选择Initial Chain

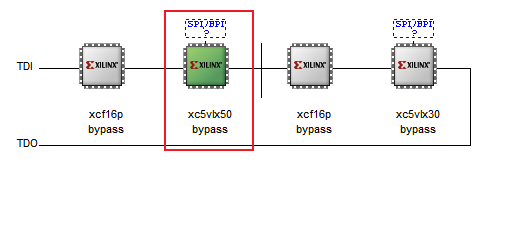

3.在线烧录的方式,双击fpga芯片,选择bit文件

4.随后右键foga芯片,选择program完成烧写。